Программа для ЭВМ это упорядоченная последовательность команд, подлежащая обработке

Скачать 1.98 Mb. Скачать 1.98 Mb.

|

47.Периферийные устройства микроконтроллеров: параллельные порты ввода/вывода, таймеры и процессоры событий, интерфейсы последовательного ввода/вывода.Параллельные порты ввода/вывода Каждый МК имеет некоторое количество линий ввода/вывода, которые объединены в 8-разрядные параллельные порты ввода/вывода РТх («х» – имя порта, используемое в техническом описании). Порты обозначают либо цифрами (РТ0, РТ1, РТ2 и т.д.), либо буквами латинского алфавита (РТА, РТВ, РТС и т.д.). В карте памяти МК каждый порт ввода/вывода представлен регистром данных порта DPTx. В режиме ввода логические уровни сигналов на линиях порта РТх отображаются нулями и единицами в соответствующих разрядах регистра DPTx. В режиме вывода данные, записанные под управлением программы в регистр DPTx, передаются на выводы МК, которые используются в качестве линий порта РТх. Обращение к регистру данных DPTx осуществляется теми же командами, что и обращение к ячейкам резидентной памяти. Кроме того, во многих МК отдельные разряды портов могут быть опрошены командами битовых операций. С функциональной точки зрения различают следующие типы параллельных портов:

Выходные каскады линий ввода/вывода часто называют драйверами(не путать с аналогичным обозначением программных средств). Различают следующие типы драйверов ввода/вывода:

В драйверах первого типа каждой линии порта поставлен в соответствие одноименный разряд регистра направления передачи DDPTx. Нулевое значение разряда конфигурирует линию на ввод, единичное – на вывод. После сброса МК все линии настроены на ввод. В режиме ввода непосредственно в момент считывания логический уровень сигнала линии передается на внутреннюю магистраль данных, минуя регистр данных порта DPTx. В процессе чтения линии ее состояние не запоминается в регистре DPTx и, следовательно, каждое новое обращение к порту ввода может возвращать новое значение. В режиме ввода линия находится в высокоомном состоянии (Z-состояние). Значение, которое будет возвращать операция чтения неподключенного входа, в общем случае не определено. Особенность драйверов двунаправленных портов, которые не требуют инициализации, заключается в том, что при считывании возвращаемое значение равно логическому произведению сигнала на линии и содержимого одноименного разряда регистpa данных порта DPTx. По этой причине те разряды порта, которые будут считываться, должны быть предварительно установлены в 1 командой записи в порт и лишь затем прочитаны. Порты с рассматриваемой схемотехникой не имеют регистра направления передачи и, следовательно, не должны инициализироваться. При работе в режиме ввода линия имеет высокое входное сопротивление, но при чтении неподключенного входа возвращается 1. Квазидвунаправленные драйверы отличаются от предыдущего драйвера тем, что на линии установлен внутренний подтягивающий резистор RPULLUP. Поэтому входное сопротивление линии ввода не столь велико, как в двух предыдущих случаях, т.е. входной буфер линии не эквивалентен входу логического элемента. Поэтому драйвер с рассматриваемой схемотехникой и получил название квазидвунаправленного. Линии с этим типом драйвера не требуют инициализации, но для работы в режиме ввода, так же как и в предыдущем случае, необходимо предварительно записать в соответствующий разряд регистра данных 1. Драйверы линий с изменяемой схемотехникой могут быть выполнены двумя способами. Однако преследуемая цель одна – сократить число навесных элементов. В первом случае драйвер каждой линии содержит подтягивающим к 1 резистор RPULLUP, который обеспечивает уровень логической единицы на входе при неподключенном выводе. Во втором случае драйвер дополнен подтягивающим к 0 резистором RPULLDOWN, который способен служить нагрузочным резистором датчика, выходной каскад которого выполнен по схеме эмиттерного повторителя. Различают линии с нормальной и повышенной нагрузочной способностью. Если речь идет о нормальной нагрузочной способности, то следует ориентироваться на следующие цифры: Iвых0 = 1,6-2,0 мА, Iвых1 = 0,4-2,0 мА. Типовые значения повышенной нагрузочной способности: Iвых0 = Iвых1 = 25 мА. Предельное значение повышенной нагрузочной способности составляет: Iвых1 = 60 мА (Microchip PIC17). Число выводов МК с повышенной нагрузочной способностью обычно ограничено. Таймеры и процессоры событий Модули таймера в 8-разрядных МК различных фирм имеют следующие особенности: число каналов входного сравнения и выходного захвата (IС и ОС), которые реализованы в модуле таймера МК, может быть различно. Так, в МК Motorola семейства НС05 типовыми решениями являются модули 2IC+2OC или 1IC+1OC, и модуль таймера в составе МК всегда только один. МК Motorola семейства НС11 имеют в своем составе модуль таймера с конфигурацией 3IC+5OC;

Аппаратные средства таймера позволяют решить многие задачи управления в реальном времени. Однако процесс совершенствования алгоритмов управления предъявляет все новые требования к структуре МК. Как следствие, все более отчетливо проявляются ограничения модулей таймера:

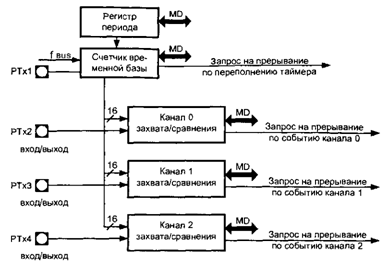

Следующий этап в развитии модулей подсистемы реального времени МК – модули процессоров событий. Модульпроцессорасобытий(рис. 72) содержит в себе 16-разрядный счетчик временной базы и некоторое количество универсальных каналов захвата/сравнения. Счетчик может тактироваться импульсной последовательностью с выхода программируемого делителя частоты тактирования внутренних магистралей fBUS или внешним генератором. Счетчик имеет опции пуска/останова и сброса в 0. В некоторых моделях процессора событий счетчик временной базы доступен для чтения «на лету». Режим чтения «на лету» предусматривает автоматическое копирование содержимого старшего и младшего байтов счетчика в специальные буферные регистры в момент выполнения операции чтения любого байта счетчика (старшего или младшего). Тогда при чтении второго байта счетчика возвращается код из соответствующего буферного регистра. Тем самым исключается ошибка считывания по причине изменения состояния счетчика временной базы за время чтения. Наиболее совершенные модели процессора событий 8-разрядных МК допускают изменение коэффициента счета счетчика временной базы  . . Рисунок 72 – Структура процессора событий Универсальные каналы захвата/сравнения в процессоре событий полностью идентичны друг другу и в зависимости от программных настроек могут работать в одном из трех режимов:

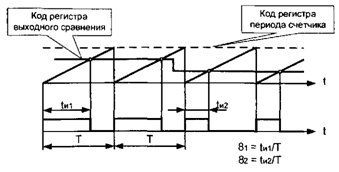

Первые два режима по принципу действия ничем не отличаются от аналогичных режимов модуля таймера. В режиме широтно-импульсной модуляции (рис. 73) на выводе PTxi МК формируется последовательность импульсов с периодом, равным периоду работы счетчика временной базы. Длительность импульса (в некоторых моделях длительность паузы) прямо пропорциональна коду в регистре данных канала. Поскольку счетчик временной базы допускает изменение коэффициента счета, то одновременно может регулироваться и период широтно-модулированной импульсной последовательности.  Рисунок 73 – Принцип работы канала захвата/сравнения в режиме ШИМ Рисунок 73 – Принцип работы канала захвата/сравнения в режиме ШИМРежим ШИМ в различных моделях процессоров событий имеет существенные отличия. В некоторых МК код коэффициента заполнения имеет однобайтовый формат, следовательно, дискретность регулирования коэффициента заполнения составляет 1/256 периода ШИМ-сигнала. В других моделях МК код коэффициента заполнения имеет двухбайтовый формат и, следовательно, дискретность регулирования составляет 1/216 периода ШИМ-сигнала. Модули таймеров особенно со схемами захвата/сравнения – достаточно сложные устройства. Их функциональная гибкость в простейших системах управления часто оказывается избыточной. Поэтому в некоторых МК, выполненных в корпусах с небольшим количеством выводов (16 или 20), с целью снижения стоимости ИС реализуются упрощенные таймеры. Таймеры содержат постоянно считающий 8-разрядный счетчик с триггером переполнения и программируемый делитель частоты. Такие таймеры могут формировать лишь метки реального времени с периодом следования, который определяется набором коэффициентов деления программируемого делителя частоты. Контроллеры последовательного ввода/вывода 8-разрядные МК имеют в своем составе два контроллера последовательного обмена, а некоторые модели – даже три. Задачи, которые решаются средствами модуля контроллера последовательного ввода/вывода, могут быть условно разделены на три группы:

В состав 8-разрядных МК входят следующие модули контроллеров последовательных интерфейсов: модуль универсального последовательного интерфейса USI (Universal Serial Interface). Может поддерживать протоколы асинхронного обмена для интерфейсов RS-232, RS-422, RS-485, а также синхронные протоколы интерфейсов SPI и I2C; модуль универсального асинхронного интерфейса UART (Universal Asynchronous Receiver and Transmitter). Поддерживает протоколы асинхронного обмена интерфейсов RS-232, RS-422 и RS-485;

Одноименные модули контроллеров последовательных интерфейсов даже одной фирмы-производителя имеют отличия в реализации для разных семейств МК. Однако эти отличия преимущественно сводятся к различию регистров специальных функций, которые обслуживают модуль. Меньше затрагивают алгоритмы функционирования одноименных модулей. И, по определению, все аналогичные модули обязательно реализуют на аппаратном уровне логику протокола обмена выбранного интерфейса. |