Курсовая по МПСУ. МПСУ КУРСОВАЯ. программируемый контроллер для управления судовыми механизмами

Скачать 146.48 Kb. Скачать 146.48 Kb.

|

|

Министерство транспорта Российской Федерации Федеральное агентство морского и речного транспорта ФГОУ ВПО "Морская государственная академия имени адмирала Ф.Ф.Ушакова" Судомеханический факультет Кафедра судовой электроавтоматики курсовая работа по дисциплине "Микропроцессорные системы управления" на тему: «ПРОГРАММИРУЕМЫЙ КОНТРОЛЛЕР для управления судовыми механизмами» Специальность 240600 "Эксплуатация судового электрооборудования и средств автоматики" Выполнил: курсант 441 уч.гр. ПАК. А. В. Руководитель: САМОЙЛЕНКО А. Ю. Новороссийск 2020 1. Задание на курсовую работу Целью курсовой работы является разработка программируемого контроллера (ПК), предназначенного для управления в функции времени судовыми механизмами дискретного действия. 1. Исходные данные для проектирования: Таблица 1

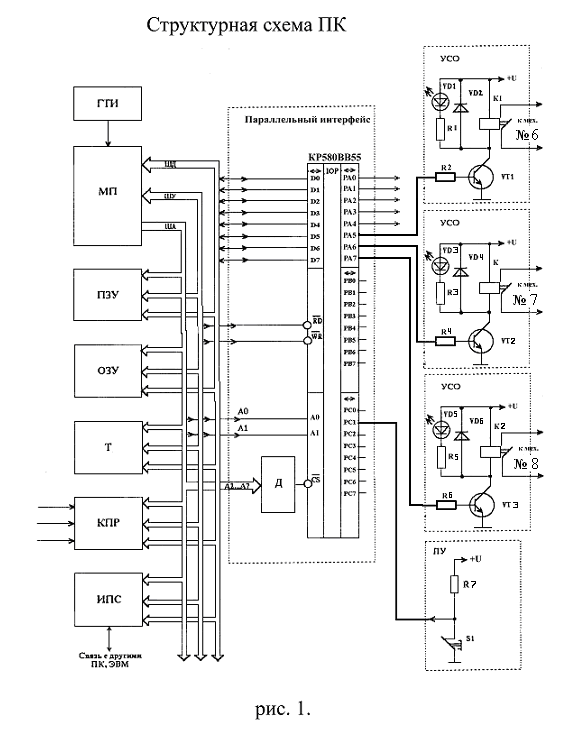

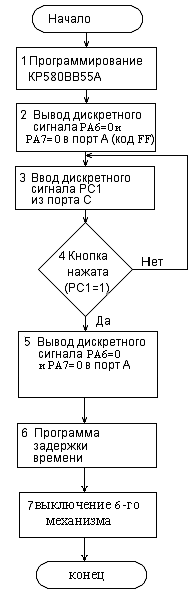

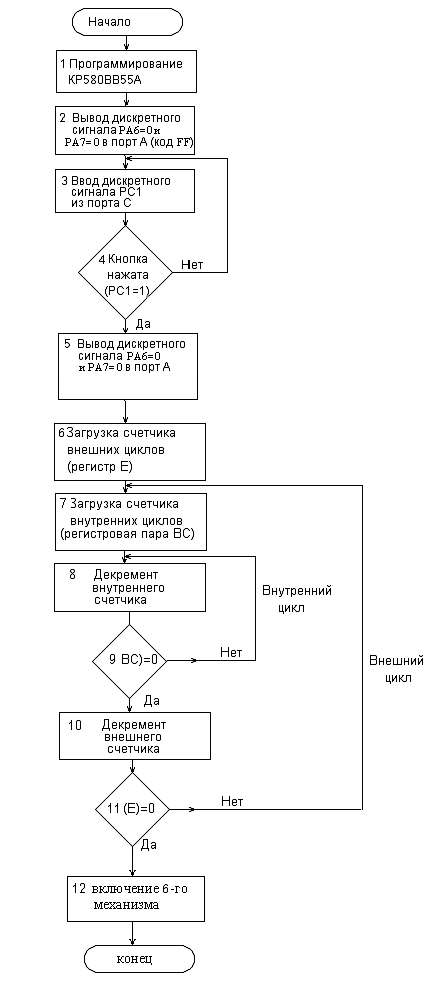

2. Другие данные и условия проектирования: схема ПК выполняется на основе микропроцессора КР580ВМ80; интерфейс ПК выполняется на основе микросхемы программируемого параллельного интерфейса типа КР580ВВ55; на незадействованные для управления заданными механизмами выходы ПК сигналы подаваться не должны; алгоритм управления запускается в работу кратковременным (менее ) нажатием управляющей кнопки. 3. Тип микропроцессорной микросхемы или блока для анализа их характеристик: NL-8AI. 4. Программа разрабатываемого программируемого контроллера должна быть отлажена на учебном микропроцессорном комплекте и продемонстрирована в работе во время защиты курсовой работы. Содержание1. Задание на курсовую работу 2 2. Структурная схема ПК 4 3. Характеристики микропроцессорного модуля NL-8AI 8 4. Укрупнённая блок-схема алгоритма работы ПК 11 5. Детальная блок-схема алгоритма работы ПК 13 6. Расчёт задержки времени 14 7. Программа работы ПК 16 8. Список использованной литературы 17 2. Структурная схема ПК Упрощенная структурно-принципиальная схема ПК содержит набор функциональных узлов, присущих большинству ПК, используемых в судовых системах автоматики. Блоки ПК связаны между собой тремя информационными шинами – шиной адреса (ША), шиной данных (ШД) и шиной управления (ШУ). Совокупность этих шин образует системную магистраль. В ПЗУ хранится программа работы контроллера. Оперативное запоминающее устройство (ОЗУ) служит для временного хранения данных. Микропроцессор (МП) обеспечивает математическую и логическую обработку информации и работает по программе хранящейся в ПЗУ, реализует собственно алгоритм работы ПК. Темп работы МП задается генератором тактовых импульсов. Таймер (Т) используется для организации работы ПК в функции времени. Контроллер прерываний (КПР) обеспечивает оперативную реакцию ПК на внешние события, не терпящие отлагательства. Например, сигналы от датчиков критических параметров управляемого оборудования. Блок последовательного интерфейса (ИПС) обеспечивает связь данного контроллера с другими ПК или центральной ЭВМ. Он позволяет организовать работу ПК в составе комплексной системы автоматизации судна. Наиболее часто в блоке ИПС реализован один из стандартных последовательных интерфейсов – CL или RS-485 (а также модификации последнего). Блок параллельного интерфейса на рисунке раскрыт до уровня принципиальной схемы. Через устройство сопряжения с объектом (УСО) он обеспечивает связь с управляемым оборудованием (механизмами), а также с пультом управления (ПУ). Параллельный интерфейс выполнен на основе БИС программируемого параллельного интерфейса (ППИ) КР580ВВ55, широко используемой для этих целей в контроллерах самого разного назначения. В состав параллельного интерфейса входит также дешифратор (Д) включающий в работу ППИ, когда МП обращается (т.е. задает адрес) к какому-либо порту микросхемы. При этом выбор конкретного порта в микросхеме осуществляется двумя младшими разрядами кода адреса, подаваемыми на входы А0 и А1 микросхемы с шины адреса. Направление передачи информации между МП и ППИ определяется сигналами, поступающими с ШУ на входы RD или WR. При наличии сигнала RD (чтение) информация из выбранного порта через шину данных передается от ППИ (с выходов D0 – D7) к МП. При наличии сигнала WR информация от МП поступает в один из портов ППИ. Данный контроллер обеспечивает управление 8 механизмами дискретного действия. Для управления используется порт А ППИ, к каждому из входов которого подключен релейный блок. На рисунке показана схема релейного блока управления механизмом №2, №4, №5. По существу релейный блок – это усилитель, обеспечивающий управление маломощным электромагнитным реле К1, контакты которого определенным образом включены в цепь управления собственно механизма. Такая схема – одна из простейших возможных схем построения УСО, вместе с тем, она широко применяется. Использование реле обеспечивает гальваническое разделение схемы ПК (с низковольтным питанием) и схемы собственно механизма, которая обычно находится под более высоким напряжением постоянного или переменного тока. Работает релейный блок следующим образом. Когда на выходе РА2 микросхемы КР580ВВ55 присутствует сигнал логического нуля, на базу транзистора VT1 напряжение не подается, он закрыт. Все напряжение питания  приложено к транзистору. Напряжение на обмотке реле К1 отсутствует и светодиод VD1, индицирующий состояние реле, погашен. При появлении логической единицы на выходе РА2 появляется ток базы VT1, ограничиваемый резистором R1. Транзистор открывается, обмотка реле запитывается и реле срабатывает, замыкая контакты и воздействуя таким образом на состояние механизма. Светодиод VD1 начинает светиться, т.к. он через токоограничивающий резистор R2 подключен параллельно обмотке реле. Диод VD2 защищает транзистор от перенапряжения, возникающего при выключении тока через обмотку реле. приложено к транзистору. Напряжение на обмотке реле К1 отсутствует и светодиод VD1, индицирующий состояние реле, погашен. При появлении логической единицы на выходе РА2 появляется ток базы VT1, ограничиваемый резистором R1. Транзистор открывается, обмотка реле запитывается и реле срабатывает, замыкая контакты и воздействуя таким образом на состояние механизма. Светодиод VD1 начинает светиться, т.к. он через токоограничивающий резистор R2 подключен параллельно обмотке реле. Диод VD2 защищает транзистор от перенапряжения, возникающего при выключении тока через обмотку реле.Пульт управления ПУ содержит кнопку S1 и резистор R7. В исходном, не нажатом положении, контакт кнопки замкнут и отсутствие напряжения на ней соответствует сигналу логического нуля. При нажатии кнопки все напряжение U приложено к S1, что соответствует сигналу логической единицы. Состояние кнопки в виде сигнала логической единицы или нуля подается на вход PC1 порта С, который должен быть настроен на ввод, в то время как порт A работает на вывод. Порт B в данном ПК не используется и его настройка значения не имеет. Для отладки контроллера используется учебный микропроцессорный комплект (УМК) с макетной платой М1, выполняющей интерфейсную функцию. Схема параллельного интерфейса, УСО и ПУ выполненная на макетной плате М1, в целом соответствует схеме ПК, за исключением отсутствующих реле. Выходные сигналы ПК индицируются светодиодами. На макетной плате заданы М1 следующие адреса портов: порт A – 80H, порт B – 81H, порт C – 82H, регистр управляющего слова – 83Н.  3. Характеристики микропроцессорного модуля «NL-8AI» Модули характеризуются следующими основными свойствами: температурным диапазоном работоспособности от -40 до +50 С; имеют защиту от: o неправильного подключения полярности источника питания; o перенапряжения по входу; o короткого замыкания по выходу; o перегрузки по току нагрузки; o перенапряжения по выходу; o перегрева выходных каскадов; o электростатических разрядов по выходу, входу и порту RS-485; o выбросов напряжения при индуктивной нагрузке; o перегрева выходных каскадов порта RS-485; o короткого замыкания клемм порта RS-485; Точность измерений NL-8AI защит плавкими предохранителями от повышенных токов или мощности; двойной сторожевой таймер выполняет рестарт устройства в случае его "зависания" и провалов питания, а также переводит выходы в безопасные состояния при "зависании" управляющего компьютера; имеют групповую изоляцию входов и групповую изоляцию выходов с тестовым напряжением изоляции 2500 В; входы имеют общую гальваническую изоляцию от части модуля, соединенной с источником питания и портом RS. Изоляция обеспечивает уменьшение влияния синфазного напряжения, которое может присутствовать на входных клеммах. Изоляция защищает также модуль от разности потенциалов между "землей" источника сигнала и приемника, которая может возникнуть при наличии недалеко расположенного мощного оборудования; разрешающая способность 16 бит; программно переключаемые диапазоны входных сигналов: 150 мВ, 500 мВ, 1 В, 5 В, 10 В, 20 мА (для NL-8AI). три типа формата данных: инженерный, шестнадцатеричный, проценты от шкалы. Тип формата выбирается программно; скорость обмена через порт RS-485, бит/с: 1200; 2400, 4800, 9600, 19200, 38400, 57600, 115200. Выбирается программно; модули имеют встроенный контроллер и благодаря наличию каналов дискретного вывода могут выполнять функцию автономного локального релейного или ПИД регулирования; встроенное ЭППЗУ позволяет хранить настройки модуля при выключенном питании; программное обеспечение: ОРС сервер; степень защиты от воздействий окружающей среды - IP20; наработка на отказ не менее 100 000 час.; вес модуля не более 500 г. 4. Укрупнённая блок-схема алгоритма работы ПК  Рис. 4. Блок-схема работы ПК В блоке 1 задаётся направление работы портов ППИ КР580ВВ55. Порт А – вывод данных, порт В – не используется, порт С – ввод данных. В блоке 2 в порт А выводятся управляющие дискретные сигналы РА6=0, РА7=0 В блоках 3 и 4 проверяется состояние кнопки подключенной к линии РС1 порта С. Программа ожидает её нажатие – непрерывно осуществляя переход к началу блока 3. С нажатием кнопки РС1 начинает выполнятся блок 5. В блоке 5 в порт А выводятся дискретные сигналы РА6=0, РА7=0 которые выключают механизмы 7 и 8. Такое состояние сохраняется всё время, пока выполняется блок 6, в котором реализована задержка времени. По истечении времени задержки происходит переход к блоку 7. Блок 7 производит вывод дискретного сигнала РА5=0. Это приводит к выключению механизма 6. 5. Детальная блок-схема алгоритма работы ПК На рис. 5 показана детальная блок-схема алгоритма работы ПК. В блоке 1 задаётся направление работы портов ППИ КР580ВВ55. Порт А – вывод данных, порт В – , разряды РС7-РС4 порта С – ввод данных. В блоке 2 в порт А выводятся управляющие дискретные сигналы РА6=0, РА7=0, которые останавливают механизмы 7 и 8. В блоках 3 и 4 проверяется состояние кнопки подключенной к линии РС1 порта С. Программа ожидает её нажатие – непрерывно осуществляя переход к началу блока 3. С нажатием кнопки РС1 начинает выполнятся блок 5. В блоке 5 в порт А выводятся дискретные сигналы РА6=0, РА7=0 Такое состояние сохраняется всё время, пока выполняется блок 6, в котором реализована задержка времени. По истечении времени задержки происходит переход к блоку 7. Блок 7 производит вывод дискретного сигнала РА5=0. Это приводит к выключению механизма 6. На рис. 6 показана блок-схема алгоритма формирования временной задержки. На рис. 4 он обозначен как единый блок 6. Задержка времени формируется программно, без использования таймера. Для создания задержки в программе организуются два вложенных друг в друга цикла. Их время выполнения зависит от количества проходов циклов, задаваемого числами, заносимыми в регистры Е, В и С микропроцессора. Программа задержки осуществляется блоками 8 – 13. Блок 8 выполняет запись начального числа в регистр В и С. Затем в блоке 10 производится уменьшение значения на единицу. Блок 11 содержимое регистров сравнивается с нулём. Если оно не равно нулю, то повторяется выполнение блока 10 до тех пор, пока значение регистра не станет нулевым. Затем произойдёт выполнение внешнего цикла с использованием регистра Е. Далее повторяется выполнение внутреннего цикла , и так до тех пор пока состояния обоих счётчиков (внутреннего и внешнего циклов) не станут нулевыми. 6. Расчёт задержки времени Время выполнения программы задержки рассчитывается по формуле: t=NвнешнNвнутрtвнутр; Где tвнутр- время, затраченное на один переход во внутреннем цикле. - команда DCXB выполняется за 5 машинных тактов, MOV А,В – 5 тактов, ORAC – 4 такта, JNZ DELAY – 10 тактов. Таким образом, внутренний цикл выполняется за 24 такта. Один такт в УМК длится 0,5 мкс. Поэтому tвнутр=240,5=12 мкс. Время полного выполнения внутреннего цикла составляет: tвнутр=833312=0,1 с. Чтобы обеспечить задержку времени =5с, внешний цикл необходимо повторить 50 раз.  Рис. 5 Детальная блок-схема 7. Программа работы ПК (таблица 1)

Выводы В результате выполнения курсовой работы разработана схема интерфейсного блока и программа работы программируемого контроллера, который управляет тремя судовыми механизмами дискретного действия, например, насосами, вентиляторами и т.д. Программа отлажена на учебном микропроцессорном комплекте. 8. Список использованной литературы Изучение ввода/вывода дискретных сигналов в МПСУ. Методические указания к л/р №2 по курсу МПСУ для специальности 18.09., - Новороссийск: НГМА, 1995г. Методические указания к курсовой работе “Программируемый контроллер для управления судовыми механизмами” по курсу МПСУ для специальности 24.06, - Новороссийск: НГМА, 2007г. Изучение ввода/вывода данных в МПСУ в функции времени. Методические указания к л/р №3 по курсу МПСУ для специальности 18.09., - Новороссийск: НГМА, 1995г. Щелкунов Н.Н., Дианов А.П. Микропроцессорные средства и системы. - М.: Радио и связь, 1989. Микропроцессоры и микропроцессорные комплекты интегральных микросхем. Справочник. В 2-х томах. Под ред. Шахнова В.А. - М.: Радио и связь, 1987. Баранов А.П., Баскаков Л.В., Тихонов Е.В. Применение учебного микропроцессорного комплекта для изучения микропроцессорных систем управления. Учебное пособие. - М.: В/О “Мортехинформреклама”, 1989. Материалы интернет-сайтов фирм-изготовителей микропроцессорных блоков автоматики. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||