Реализация ПУ. Реализация пропорционального регулятора. Реализация пропорционального регулятора Аналоговая реализация с операционными усилителями

Скачать 123.14 Kb. Скачать 123.14 Kb.

|

|

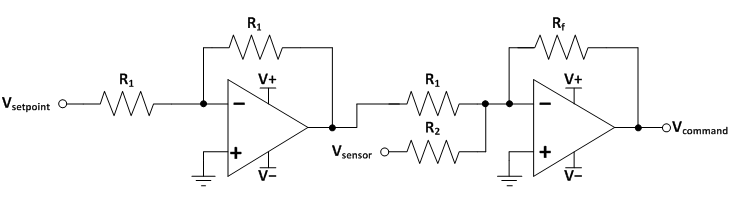

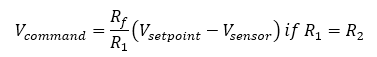

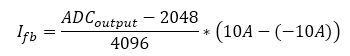

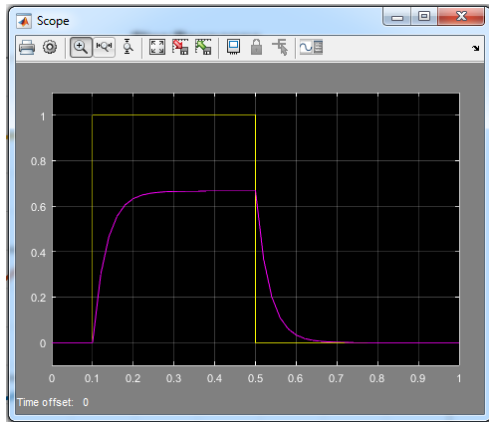

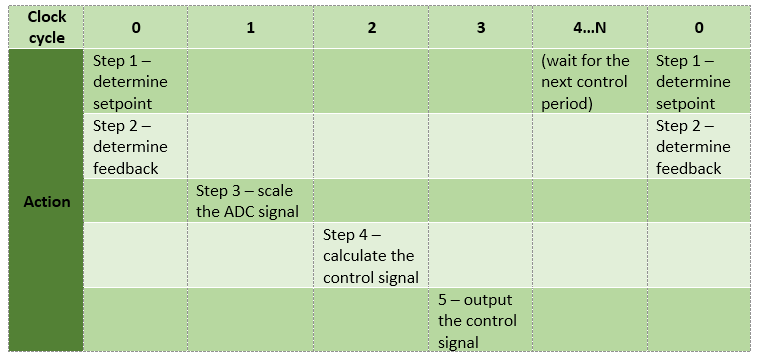

Реализация пропорционального регулятора Аналоговая реализация с операционными усилителями   Представленная схема выдает напряжение, пропорциональное разнице между напряжениями в Vsetpoint и Vsensor.. Первый операционный усилитель представляет собой инвертирующий усилитель с единичным усилением, второй - инвертирующий суммирующий усилитель с коэффициентом усиления  . .Цифровая обработка сигналов (DSP – англ. digital signal processing) Цифровые сигнальные процессоры принимают на вход предварительно оцифрованные физические сигналы, например, звук, видеоизображение, показания температуры, давления и положения, и производят над ними математические манипуляции. Внутренняя структура цифровых сигнальных процессоров специально разрабатывается таким образом, чтобы они могли очень быстро выполнять такие математические функции, как “сложение”, “вычитание”, “умножение” и “деление”. Один из способов реализации: Определить значение lcmd Измерить lfb_adc Масштабировать сигнал обратной связи так, чтобы он использовал тот же диапазон, что и команда. Выход АЦП нужно масштабировать по уравнению:  . .Рассчитать error (error=lcmd-lfb) Рассчитать output (output=proportionalgain*error) Вывести сигнал с помощью АЦП или других средств Реализация Simulink  На рисунке представлена передаточная функция. Она является точным изображением схемы индуктивность-сопротивление, которая показана в «Аналоговой реализации».  На графике текущая команда отмечена желтым, ток индуктора – фиолетовым. Реализация FPGA Принцип реализации FPGA такой же, как и у DSP. Но главным их различием является то, что DSP выполняется последовательно, а FPGA – параллельно. Поэтому когда управляющее действие должно происходить с определенной скоростью, нужно установить временную задержку между этапами, как показано в нижеприведенной таблице.  Шаги 1 и 2 выполняются параллельно, так как не зависят друг от друга. |