23.02.2021 лекция. Режимы работы микропроцессора

Скачать 214.82 Kb. Скачать 214.82 Kb.

|

|

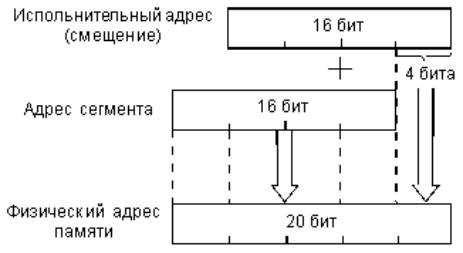

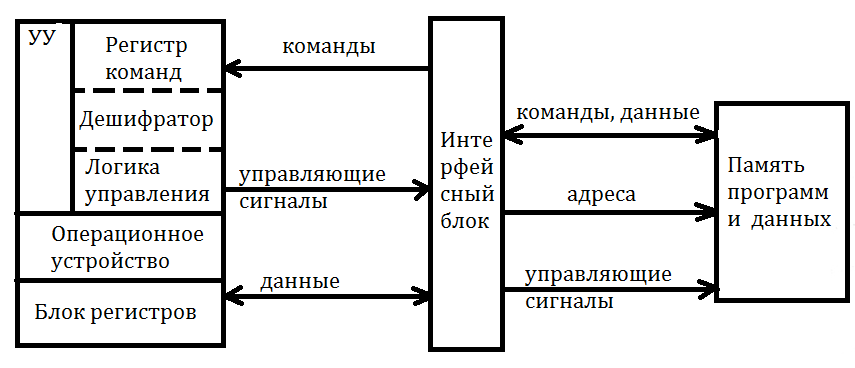

Режимы работы микропроцессора Под организацией процессора понимают совокупность его узлов (устройств, блоков, модулей), связи между узлами и их функциональные характеристики. Организация определяет аппаратную организацию процессора, т. е. состав и взаимодействие его аппаратных средств. Выделяют два уровня организации: ● физическую организацию в виде принципиальной схемы; ● логическую организацию в виде структурно–функциональной схемы. Архитектура процессора - это совокупность его программно–аппаратных средств, обеспечивающих обработку цифровой информации (выполнение программы), т. е. совокупность всех средств, доступных программе (или пользователю). Микроархитектура процессора - это аппаратная организация и логическая структура микропроцессора, регистры, управляющие схемы, арифметико-логические устройства, запоминающие устройства и связывающие их информационные магистрали. Макроархитектура процессора - это система команд, типы обрабатываемых данных, режимы адресации и принципы работы микропроцессора. По форматам используемых команд существуют несколько видов архитектур процессоров: ● CISC–архитектура относится к процессорам (компьютерам) с полным набором команд. Она реализована во многих типах микропроцессоров (напримерPentium), выполняющих большой набор разноформатных команд с использованием многочисленных способов адресации. Система команд процессоров с CISC–архитектурой может содержать несколько сотен команд разного формата (от 1 до 15 байт), или степени сложности, и использовать более 10 различных способов адресации, что позволяет программисту реализовать наиболее эффективные алгоритмы решения различных задач. Развитие традиционных CISC–архитектур микропроцессоров по пути расширения функциональных возможностей и снижения затрат на программирование привело к увеличению числа команд в наборе и числа микрокоманд в команде. Следствием этого явилось усложнение интегральных схем и снижение быстродействия выполнения программ. Один из возможных путей устранения указанных недостатков состоит в использовании сокращенного набора команд, организация которого подчинена увеличению скоростей их выполнения; ● RISC–архитектура относится к процессорам (компьютерам) с сокращенным набором команд (ReducedinstructionSetComputer — RISC). Появление RISC–архитектуры продиктовано тем, что многие CISC–команды и способы адресации используются достаточно редко. Основная особенность RISC–архитектуры проявляется в том, что система команд состоит из небольшого количества часто используемых команд одинакового формата, которые могут быть выполнены за один командный цикл (такт) центрального процессора. Более сложные, редко используемые команды реализуются на программном уровне. Однако за счет значительного повышения скорости исполнения команд средняя производительность RISC–процессоров может оказаться выше, чем у процессоров с CISC–архитектурой. Большинство команд RISC–процессоров связано с операцией регистр–регистр. Для обращения к памяти оставлены наиболее простые с точки зрения временных затрат операции загрузки в регистры и записи в память. Современные RISC–процессоры реализуют около 100 команд, имеющих фиксированный формат длиной 4 байта, и используют небольшое число наиболее простых способов адресации (регистровую, индексную и некоторые другие). Для сокращения количества обращений к внешней оперативной памяти RISC–процессоры содержат десятки–сотни регистров общего назначения (РОН), тогда как в CISC–процессорах всего 8–16 регистров. Обращение к внешней памяти в RISC–процессорах используется только в операциях загрузки данных в РОН или пересылки результатов из РОН в память. За счет сокращения аппаратных средств, необходимых для декодирования и выполнения сложных команд, достигается существенное упрощение интегральных схем RISC–процессоров и снижение их стоимости. Кроме того, значительно повышается производительность. Благодаря указанным достоинствам во многих современных CISC–процессорах (последние модели Pentium и К7) используется RISC–ядро. При этом сложные CISC–команды предварительно преобразуются в последовательность простых RISC–операций и быстро выполняются RISC–ядром; ● VLIW–архитектура относится к микропроцессорам с использованием очень длинных команд (VeryLargeInstructionWord — VLIW). Отдельные поля команды содержат коды, обеспечивающие выполнение различных операций. Одна VLIW–команда может выполнить сразу несколько операций одновременно в различных узлах микропроцессора. Формирование «длинных» VLIW–koманд производит соответствующий компилятор при трансляции программ, написанных на языке высокого уровня. VLIW–архитектура реализована в некоторых типах современных микропроцессоров и является весьма перспективной для создания нового поколения сверхвысокопроизводительных процессоров. По способу организации выборки команд и данных различают два вида архитектур: ● принстонская архитектура, или архитектура фон–Неймана, особенностью которой является (рис. 2.1.1) использование: • общей основной (оперативной) памяти для хранения программ и данных, что позволяет оперативно и эффективно перераспределять ее объем в зависимости от решаемых задач в каждом конкретном случае применении микропроцессора; • общей шины, по которой в процессор поступают команды и данные, а в оперативную память записываются результаты, что значительно упрощает отладку, тестирование и текущий контроль функционирования системы, повышает ее надежность. Чтобы отделить команду от данных, первым из памяти всегда поступает код выполняемой операции, а затем следуют данные. По умолчанию код операции загружается в регистр команд, а данные — в блок регистров. Из–за ограниченного числа внешних выводов противоположные направления обмена данными между микропроцессором, памятью или другими внешними устройствами по общей шине разделены во времени.  Недостаток принстонской архитектуры — использование общей шины для передачи команд и данных ограничивает производительность цифровой системы; ● гарвардская архитектура (создатель ГовардАйкен), особенностью которой является физическое разделение памяти команд (программ) и памяти данных. Это обстоятельство вызвано постоянно возрастающими требованиями к производительности микропроцессорных систем. Память команд и память данных соединяются с процессором отдельными шинами. Благодаря разделению потоков команд и данных, а также совмещению операций их выборки (и записи результатов обработки) обеспечивается более высокая производительность, чем при использовании принстонской архитектуры. Микропроцессор — это центральный блок компьютера, предназначенный для управления работой всех остальных блоков и выполнения арифметических и логических операций над информацией. Задача микропроцессора— выполнять программы, находящиеся в основной памяти. Процессор выполняет каждую команду за несколько шагов: 1. Вызывает очередную команду из памяти и заносит ее в регистр команд. 2. Меняет содержимое счетчика команд, который после этого указывает на следующую команду. 3. Определяет тип вызванной команды. 4. Если команда использует данные из памяти, определяет, где находятся эти данные. 5. При необходимости переносит данные в регистр процессора. 6. Выполняет команду. 7. Переходит к шагу 1, чтобы начать выполнение следующей команды. Такая последовательность является основой работы всех компьютеров. Физическая память, к которой процессор имеет доступ по шине адреса, называется оперативной памятью (или оперативным запоминающим устройством — ОЗУ). ОЗУ организовано как последовательность байтов. Каждому байту соответствует свой уникальный физический адрес (его номер). Процессор поддерживает две модели использования оперативной памяти: сегментированную и страничную. Страничную модель можно рассматривать как надстройку над сегментированной моделью. В случае ее использования оперативная память рассматривается как совокупность блоков фиксированного размера. Сегментация — механизм адресации, обеспечивающий существование нескольких независимых адресных пространств для защиты задач от взаимного влияния. Сегмент - это независимый фрагмент памяти. Основные сегменты: Сегмент кодов– содержит машинные команды для выполнения. Обычно первая выполняемая команда находится в начале этого сегмента, и операционная система передает управление по адресу данного сегмента для начала выполнения программы. Регистр сегмента кода CS и указатель IP определяют адрес памяти, откуда надо прочитать следующую команду. Сегмент данных– содержит определенные данные, константы и рабочие области, необходимые программе. Сегментные регистры DS, ES, GS и FS используются для адресации данных в памяти, индексный регистр SI служит для указания смещения. Сегмент стека. Стек содержит адреса возврата для программы для возврата в операционную систему и для вызовов подпрограмм для возврата в главную программу. Регистр сегмента стека SS и указатель SP указывают на вершину стека. Режим работы процессора— состояние процессора, определяющие его поведение при выполнении различных команд и возможность доступа к различным данным. Реальный режим – это режим, при котором обращение к оперативной памяти происходит по реальным (действительным) адресам. Набор доступных операций не ограничен, защита памяти не используется. Формирование физического адреса в реальном режиме Для хранения адресов памяти используются не отдельные регистры, а пары регистров: · сегментный регистр определяет адрес начала сегмента (то есть положение сегмента в памяти); · регистр указателя (регистр смещения) определяет положение рабочего адреса внутри сегмента. При этом физический 20-разрядный адрес памяти образуется путем сложения смещения и адреса сегмента со сдвигом на 4 бита. Положение этого адреса в памяти показано на рисунке.

Например, сегмент в шестнадцатеричном виде равен 1200, а смещение — 3CDЕ.

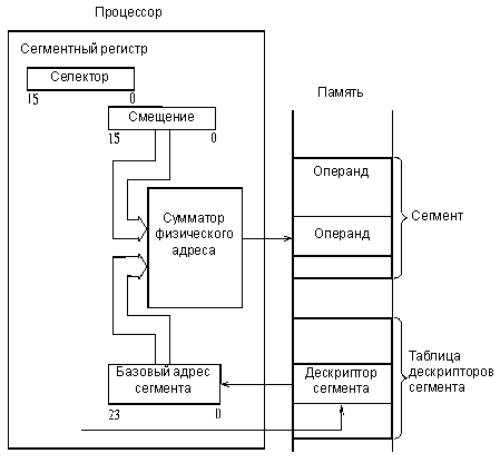

Защищённый режим – это режим, при котором обращение к памяти происходит по виртуальным адресам с использованием механизмов защиты памяти. Набор доступных операций определяется уровнем привилегий. Защищенный режим является основным режимом работы микропроцессора. Программа работает с адресами, которые могут относиться к физически отсутствующим ячейкам памяти, поэтому такое адресное пространство называется виртуальным. Размер виртуального адресного пространства программы может превышать емкость физической памяти. Для адресации виртуального адресного пространства используется сегментированная модель, в которой адрес состоит из двух элементов: селектора сегмента и смещения внутри сегмента. Формирование физического адреса в защищенном режиме Любой сегмент памяти в защищенном режиме имеет следующие атрибуты: -расположение сегмента в памяти; -размер сегмента; -уровень привилегий (определяет права данного сегмента относительно других сегментов); -тип доступа (определяет назначение сегмента). В отличие от реального режима, в защищенном режиме программа уже не может запросто обратиться по любому физическому адресу памяти. Для этого она должна иметь определенные полномочия и удовлетворять ряду требований. Ключевым объектом защищенного режима является специальная структура — дескриптор сегмента, , который представляет собой 8-байтовый дескриптор (краткое описание) непрерывной области памяти, содержащий перечисленные ранее атрибуты.  В сегментном регистре в данном случае хранится не базовый (начальный) адрес сегментов, а коды селекторов, определяющие адреса в памяти, по которым хранятся дескрипторы сегментов. Область памяти с дескрипторами называется таблицей дескрипторов. В защищенном режиме встроенные средства переключения задач обеспечивают многозадачность. Среда задачи состоит из содержимого регистров МП и всего кода с данными в пространстве памяти. Микропроцессор способен быстро переключаться из одной среды выполнения в другую, имитируя параллельную работу нескольких задач. Такое состояние называется виртуальным режимом. При этом задачи МП изолированы и защищены, как от друг друга, так и от обычных задач защищенного режима. Многозадачность (мультипрограммирование) - это такой способ организации работы системы, при котором в ее памяти одновременно содержатся программы и данные для выполнения нескольких задач. Задача (процесс) - это последовательность взаимосвязанных действий, ведущих к достижению некоторой цели. То есть это программа, которая выполняется или ожидает выполнения, пока выполняется другая программа. Мультипрограммирование предназначено для повышения пропускной способности системы путем более равномерной и полной загрузки всего его оборудования, в первую очередь - процессора. Коэффициент мультипрограммирования (КМ) - | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||