Билеты МПС. МПС. Сформулируйте понятие Архитектура микропроцессорной системы (мпс). Дайте определение понятию Архитектура микропроцессора, перечислите основные элементы мп и их назначение. (1 1 1 1)

Скачать 2.26 Mb. Скачать 2.26 Mb.

|

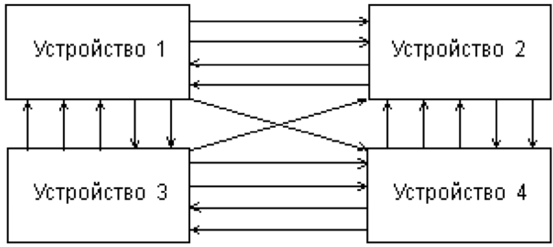

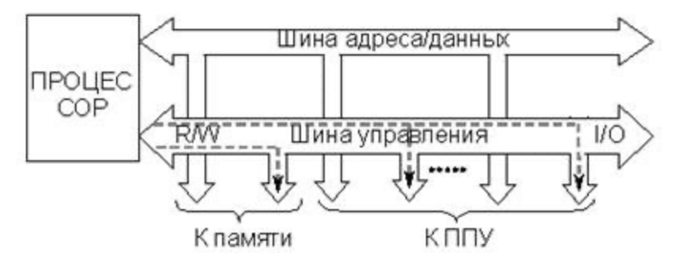

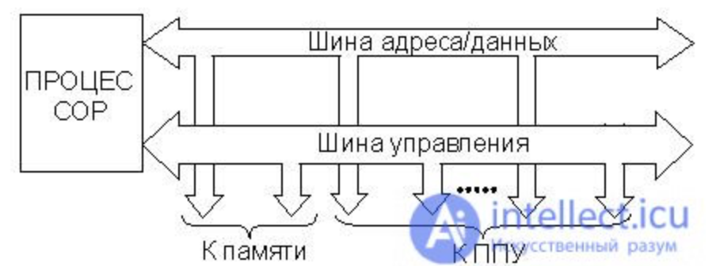

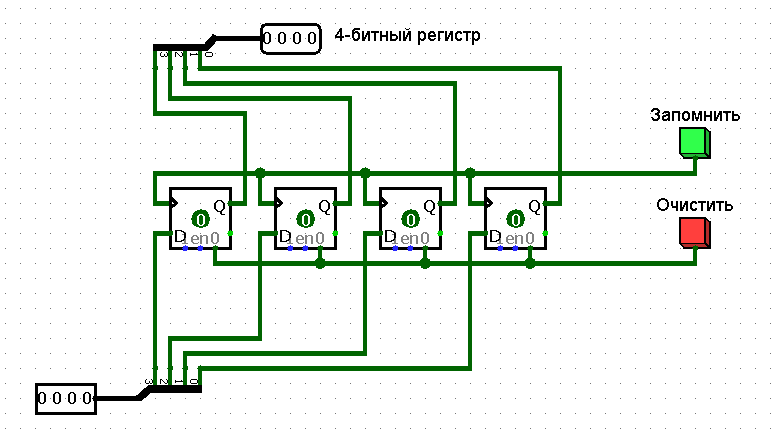

Билет №71. Представление чисел в формате BCD. Преимущества, недостатки. Математический принцип реализации. Аппаратный принцип реализации. BCD - это двоично-десятичный код. Это форма записи рациональных чисел, когда каждый десятичный разряд числа записывается в виде его четырёхразрядного двоичного кода. Например, десятичное число 31110 будет записано в двоичной системе счисления в двоичном коде как 1 0011 01112, а в двоично-десятичном коде как 0011 0001 0001BCD. Преимущества: Упрощен вывод чисел на индикацию - вместо последовательного деления на 10 требуется просто вывести на индикацию каждый полубайт. По этой же причине проще ввод данных с цифровой клавиатуры. Для дробных чисел (как с фиксированной, так и с плавающей запятой) при переводе в человекочитаемый десятичный формат и наоборот не теряется точность. Упрощены умножение и деление на 10, а также округление. По этим причинам двоично-десятичный формат применяется в калькуляторах и других устройствах, которые выводят данные на семисегментные или другие индикаторы, где каждый отдельный индикатор отображает только одну цифру. Недостатки: Требует больше памяти. Усложнены арифметические операции. Математический принцип реализации: *Видимо речь о том, что нужно каждый разряд десятичной системы, перевести в двоичную. Типа, 13, 1 = 0001, 3 = 0010, и тогда 0001 0010* Аппаратный принцип реализации: Математический сопроцессор (процессор с плавающей запятой) - сопроцессор для расширения командного множества центрального процессора и обеспечивающий его функциональностью модуля операций с плавающей запятой, для процессоров, не имеющих интегрированного модуля. Модуль операций с плавающей запятой - часть процессора для выполнения широкого спектра математических операций над вещественными числами. Целочисленным процессорам для работы с вещественными числами требуется больше времени и специальных процедур (разделение на мантиссу, показатель степени) для их выполнения. Модуль операций с плавающей запятой поддерживает работу с ними на уровне примитивов - загрузка, выгрузка вещественного числа или математическая операция над ними выполняется одной командой, за счёт этого достигается значительное ускорение таких операций. 2. Шинная структура связей в микропроцессорной системе. Преимущества данной структуры. Системная магистраль микропроцессорной системы. Структура, назначение, принцип действия. Структура системной шины микропроцессора. Ее составные части. Строение и назначение шины данных. Строение и назначение шины адреса. Строение и назначение шины управления. Структура системной шины с общими шинами команд и данных и с раздельными шинами команд и данных. В микропроцессорных системах применяется так называемая шинная структура связей между отдельными устройствами, входящими в систему. При классической структуре связей все сигналы и коды между устройствами передаются по отдельным линиям связи. Каждое устройство, входящее в систему, передает свои сигналы и коды независимо от других устройств. При этом в системе получается очень много линий связи и разных протоколов обмена информацией.  При шинной структуре связей все сигналы между устройствами передаются по одним и тем же линиям связи. В результате количество линий связи существенно сокращается, а правила обмена (протоколы) упрощаются. Группа линий связи, по которым передаются сигналы или коды как раз и называется шиной.  При шинной структуре связей легко осуществляется пересылка всех информационных потоков в нужном направлении, например, их можно пропустить через один процессор, что очень важно для микропроцессорной системы. Однако при шинной структуре связей вся информация передается по линиям связи последовательно во времени, по очереди, что снижает быстродействие системы по сравнению с классической структурой связей. Большое достоинство шинной структуры связей состоит в том, что все устройства, подключенные к шине, должны принимать и передавать информацию по одним и тем же протоколам. Существенный недостаток шинной структуры связан с тем, что все устройства подключаются к каждой линии связи параллельно. Поэтому любая неисправность любого устройства может вывести из строя всю систему, если она портит линию связи. Все устройства микропроцессорной системы объединяются общей системной шиной - системная магистраль. Она включает в себя три основные шины: шина данных — это основная шина. Количество ее разрядов (линий связи) определяет скорость и эффективность информационного обмена, а также максимально возможное количество команд. Шина данных всегда двунаправленная, так как предполагает передачу информации в обоих направлениях. Обычно шина данных имеет 8, 16, 32 или 64 разряда. За один цикл обмена по 64-разрядной шине может передаваться 8 байт информации, а по 8-разрядной — только один байт. Разрядность шины данных определяет и разрядность всей магистрали. Например, когда говорят о 32-разрядной системной магистрали, подразумевается, что она имеет 32-разрядную шину данных. шина адреса — вторая по важности шина, которая определяет максимально возможную сложность микропроцессорной системы, то есть допустимый объем памяти и, следовательно, максимально возможный размер программы и запоминаемых данных. Количество адресов, обеспечиваемых шиной адреса, определяется как 2N, где N — количество разрядов. Разрядность шины адреса обычно кратна 4 и может достигать 32 и даже 64. Шина адреса может быть однонаправленной (когда магистралью всегда управляет только процессор) или двунаправленной (когда процессор может временно передавать управление магистралью другому устройству, например контроллеру прямого доступа к памяти (ПДП)). шина управления — это вспомогательная шина, управляющие сигналы на которой определяют тип текущего цикла и фиксируют моменты времени, соответствующие разным частям или стадиям цикла. Управляющие сигналы обеспечивают согласование работы процессора (master) с работой памяти или устройства ввода/вывода (slave). Управляющие сигналы также обслуживают запрос и предоставление прерываний, запрос и предоставление прямого доступа. Линии шины управления могут быть как однонаправленными, так и двунаправленными. Технически проще использовать однонаправленные шины, но тогда их число должно увеличиться, т.е. по две шины для операции "Чтение" (Ввод) и "Запись" (Вывод). Это приводит к существенному увеличению числа контактов разъема модуля МП. Для сокращения числа выводов БИС(большой интегральной схемы) используют объединение однонаправленных шин в одну двунаправленную – запись/чтение (READ/WRITE) или ввод/вывод (INPUT/OUTPUT). Виды системной магистрали: · Раздельные шины  · Изолированные шины  · Изолированные шины и мультиплексирование ША и ШД  · Общие шины  · Общие шины и мультиплексирование ША и ШД  3. Построить четырёхбитный регистр. (1 1 1 1)  |