Синтез типовых комбинационных схем. Синтез типовых комбинационных схем

Скачать 179.06 Kb. Скачать 179.06 Kb.

|

|

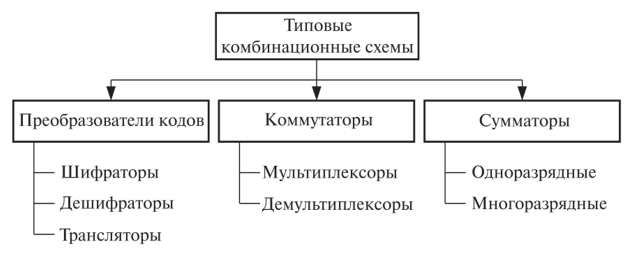

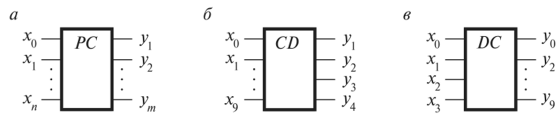

Синтез типовых комбинационных схем https://studref.com/558889/tehnika/sintez_tipovyh_kombinatsionnyh_shem Сложность современных дискретных устройств достаточно велика, а некоторые функциональные блоки повторяются более чем в половине схемных решений. Этот факт определяет целесообразность синтеза логических устройств из стандартных (типовых) комбинационных схем. Они строятся с таким расчетом, чтобы реализуемые ими функции были простыми, однозначно определенными и легко контролируемыми. Это, в свою очередь, позволяет упростить процедуру синтеза логического устройства и процесс его дальнейшей эксплуатации, связанный с возможными нарушениями в работе (от возникновения неисправностей до их обнаружения и последующей замены отказавших узлов). Наибольшее распространение в технике среди стандартных комбинационных схем получили преобразователи кодов, коммутаторы, сумматоры, компараторы и разнообразные контрольные схемы (рис. 3.33) [10]. Преобразователями кодов называются логические устройства, переводящие «-элементный параллельный двоичный код на входе в /«-элементный параллельный двоичный код на выходе.  Рис. 3.33. Наиболее распространенные типовые комбинационные схемы Частными случаями преобразователей кодов являются шифраторы и дешифраторы. На рис. 3.34 приводятся обозначения преобразователей кодов. Шифраторами (кодерами) называются логические устройства, переводящие одноэлементный параллельный код на входе в т-элементный параллельный код на выходе. На входы Xj шифратора поступают кодовые комбинации, содержащие только один единичный разряд. Таким образом, на входах формируется параллельный код, называемый равновесным кодом «1 из я». Данный код преобразуется в произвольный. Шифратор часто используется для ввода информации в цифровые устройства, например, микрокалькуляторы (при этом производится преобразование в двоичную систему счисления): при нажатии определенной клавиши на соответствующий вход шифратора подается сигнал логической единицы, а на выходах формируется двоичное число. На рис. 3.34, б приведено обозначение шифратора для преобразования десятичных чисел в двоичные. Такой шифратор имеет  Рис. 3.34. Преобразователи кодов: а — преобразователь «-элементного кода в /«-элементный; б — шифратор; в — дешифратор 10 входов, соответствующих десятичным числам и 4 выхода, необходимых для представления десяти чисел от 0 до 9 в двоичном виде. Описать работу шифратора можно табличным способом: десятичному числу ставится в соответствие двоичное (табл. 3.20). Таблица 3.20

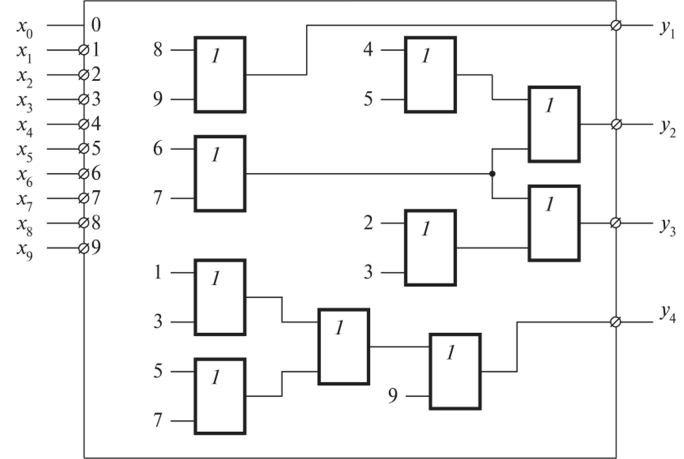

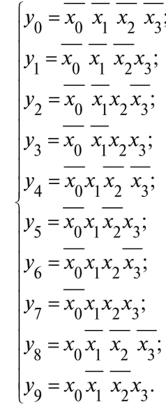

Непосредственно по табл. 3.19 можно выписать ФАЛ, описывающие выходы шифратора:  На рис. 3.35 приводится схема шифратора десятичных чисел, построенная на двухвходовых элементах ИЛИ по записанной выше системе выражений. Для реализации шифратора потребовалось 10 элементов ИЛИ. Дешифраторами (декодерами) называются логические устройства, переводящие л-элементный параллельный код на входе в одноэлементный параллельный код на выходе. Работа дешифратора противоположна работе шифратора и состоит в получении из произвольного кода комбинаций кода «1 из п». Т.е. на выходе дешифратора всегда присутствует только одна логическая единица. Пример дешифратора, переводящего двоичные 102  Рис. 3.35. Схема шифратора числа в десятичные, приведен на рис. 3.34, в. На выходе у{ будет присутствовать сигнал логической единицы в том случае, если на входах Xj будет сформирована соответствующая номеру данного выхода yt двоичная комбинация. Устройство преобразования двоичных чисел в десятичные можно описать следующей таблицей истинности (табл. 3.21). Таблица 3.21

Выходы дешифратора у0—у9 в соответствии с табл. 3.21 задаются данной системой ФАЛ:  Другие преобразователи (не шифраторы и не дешифраторы) получили название трансляторов кодов. Примерами трансляторов являются преобразователи натуральных двоичных кодов в избыточные, например, коды паритета. Рассмотрим пример синтеза транслятора натурального двоичного кода в код паритета [13]. Код паритета — избыточный код, который содержит один контрольный разряд, вычисляемый как сумма по модулю два значений разрядов натурального двоичного кода (информационных разрядов): / = х^ 0 0...0 х^. Код паритета осуществляет контроль четности (или нечетности) кодовой комбинации: если число единиц на входах xt в кодовой комбинации четное, то контрольный разряд принимает значение нуля, в противном случае — единицы. Положим, требуется двоичный код, содержащий три информационных разряда, преобразовать в код паритета. В табл. 3.22 представлены комбинации двоичного кода и соответствующие им комбинации кода паритета.

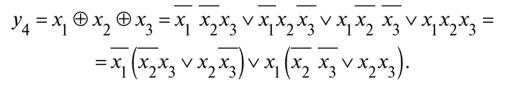

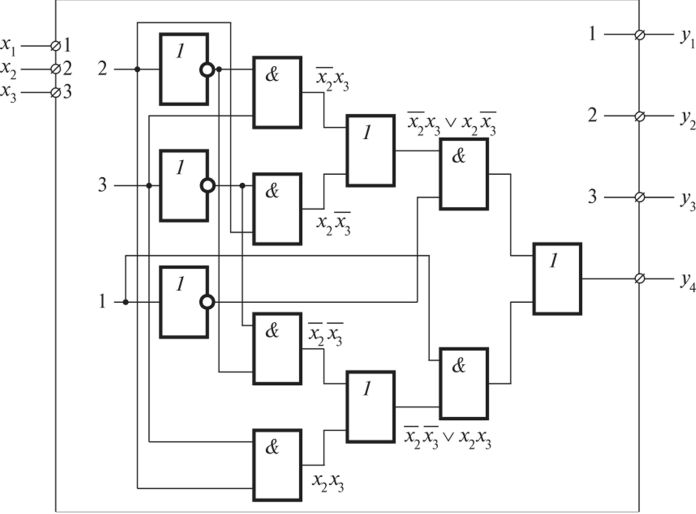

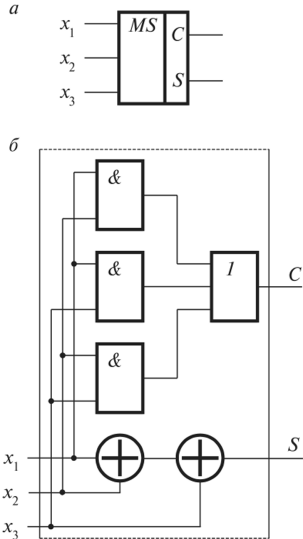

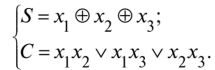

Выходы транслятора у^, у2, у3 полностью повторяют значения входов х{, х2, х2, а выход у4 является реализацией линейной функции (см. п. 3.4). ДСНФ линейной ФАЛ является и ее МДНФ, поэтому можно сразу же переходить к процессу построения самой комбинационной схемы транслятора. Построим ее на двухвходовых логических элементах в основном базисе (рис. 3.36). Выход у4 вычисляется как  Коммутаторы предназначены для избирательного переключения сигналов и классифицируются на мультиплексоры и демультиплексоры. Мультиплексором (коллектором) называется устройство, имеющее несколько информационных и один или несколько управляющих (адресных) входов, снабженное одним выходом, и передающее сигнал с того информационного входа, двоичный номер которого формируется на адресных входах. Рассмотрим работу мультиплексора, имеющего два адресных (обозначим их А) и четыре информационных (обозначим их Dj) входов (рис. 3.37, а). Для трансляции на выход сигнала с некоторого входа Dj следует сформировать на адресных входах двоичное число, соответствующее десятичному номеру входа Dr При этом  Рис. 3.36. Схема транслятора для преобразования натурального двоичного кода в код паритета Рис. 3.37. Мультиплексор: а — обозначение; б — схема мультиплексора  на выходах всех логических элементов И в схеме мультиплексора (рис. 3.37, б), кроме элемента соответствующего кодовой комбинации на адресных входах, формируется сигнал логического нуля; на логическом элементе И, соответствующем выбранному информационному входу, формируется значение этого входа. Все выходы четырех элементов И одновременно являются и входами элемента ИЛИ. Такое устройство мультиплексора обеспечивает передачу сигнала (коммутацию) с выбранного информационного входа />• на выход Q. Пусть на выход мультиплексора Q следует передать сигнал с информационного входа D2. Тогда на адресные входы требуется подать сигналы, соответствующие номеру выбранного информационного разряда, в нашем случае это кодовая комбинация {10}. На рис. 3.37, а и б показаны значения сигналов, формируемые на каждой линии мультиплексора. Отметим, что мультиплексор может снабжаться синхронизирующим входом. Мультиплексоры являются универсальными программируемыми элементами и подходят для реализации любых ФАЛ от п переменных. Особенности синтеза КДУ на мультиплексорах будут рассмотрены в п. 3.7. Рассмотрим устройство, выполняющее обратные мультиплексору функции. Демультиплексором (селектором, распределителем) называется устройство, имеющее несколько выходов, один информационный и один или несколько управляющих (адресных) входов, и передающее сигнал с информационного входа на тот выход, двоичный номер которого формируется на адресных входах. На рис. 3.38 приводится демультиплексор, коммутирующий сигнал с одного информационного входа на четыре выхода. На рис. 3.38, а приведено обозначение демультиплексора, а на рис. 3.38, б — его схема. Благодаря использованию в схеме демультиплексора логических элементов И, сигнал с входа D может быть распределен на тот выход Q0 двоичный номер которого подан на адресные входы. Формируемая на них кодовая комбинация однозначно определяет логический элемент И, соответствующий выбранному выходу. В случае подачи на информационный вход единичного значения, а на адресные входы кодовых комбинаций демультиплексор  Рис. 3.38. Демультиплексор: а — обозначение; б — схема демультиплексора работает, как дешифратор. Совместное использование мультиплексоров и демультиплексоров позволяет строить схемы коммутации с п направлений в т. Сумматором называется логическое устройство, выполняющее арифметические и логические операции над числами, представленными в двоичном, двоично-десятичном и других кодах. Рассмотрим полный одноразрядный сумматор (рис. 3.39), позволяющий складывать разряды трех двоичных чисел. Он имеет три входа х,, х2 и х3, предназначенные для обработки одноименных разрядов  Рис. 3.39. Полный одноразрядный сумматор: а — обозначение; б — схема сумматора двух двоичных чисел, и два выхода — суммы S и переноса С. Выход С предназначен для передачи в следующий (старший) разряд. Процесс функционирования полного одноразрядного сумматора описывается табл. 3.23. Таблица 3.23

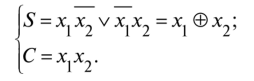

Значения выходов можно задать системой ФАЛ:  Иногда на практике полезно использовать так называемый неполный сумматор (или полусумматор), осуществляющий сложение разрядов двух двоичных чисел. Полусумматор обозначают буквами HS. Данное устройство снабжается двумя входами и двумя выходами, имеющими такое же назначение, как и у полного сумматора. Значения выходов задаются системой ФАЛ:  | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||