тема 10. Тема_10. Тема 10. Набор микроопераций и микроэлементов. Цель

Скачать 60.06 Kb. Скачать 60.06 Kb.

|

|

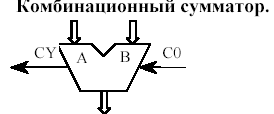

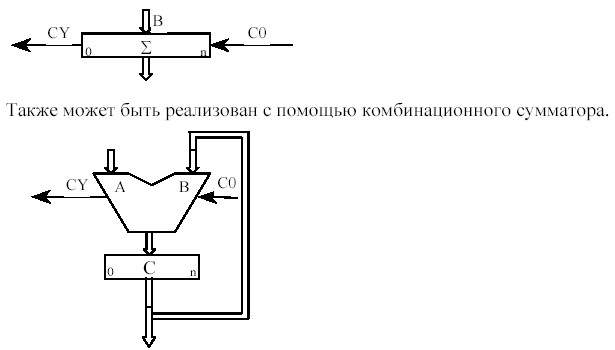

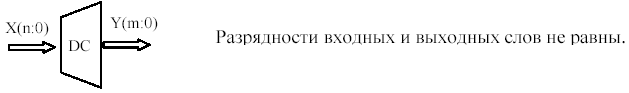

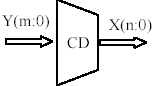

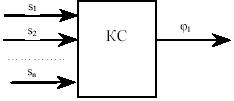

Тема 10. Набор микроопераций и микроэлементов. Цель:Архитектура компьютера является подготовка специалиста к деятельности, связанной с эксплуатацией и обслуживанием аппаратуры и оборудования, содержащего современные средства мыслительной техники. Глоссарий: Адресная шина Архитектура компьютера Базовое программное обеспечение Байт Бит Буфер обмена Видеоадаптер Внедрение Графическая шина Данные Дефрагментация диска Звуковой адаптер Интерфейс Интерфейс пользователя Кодирование Команда Компьютерная программа Конфигурация компьютера Оперативная память Операционная система Основание системы счисления Пиксель Прикладное программное обеспечение Программное обеспечение Процессор Растр Связывание Сетевой адаптер Сжатие данных Сигнал Система счисления Системное программное обеспечение Служебное программное обеспечение Сообщение Структура компьютера Файл Файловая система Шина данных Шина управления Шина устройств Операционный блок процессора представляет собой некоторую композицию так называемых композиционных элементов. Операционный элемент имеет аппаратную реализацию в виде «отдельной» части. Обеспечивает хранение слов, выполнение микроопераций над словами и их полями, а так же вычисление логических условий. Все элементы в операционном автомате (ОП) соединяются между собой с помощью шин, которые обеспечивают передачу слов с выхода одного операционного элемента на вход другого. Все микрооперации разделяются на семь групп: 1. МО установки (А:=0) G:=N 2. МО передачи (А:=В) 3. МО инвертирования (А:=А) . 4. МО сдвига (А:=L1(A).0) – конкатенация. 5. МО счета (С:=С±1) 6. МО сложения (С:= А ± В) 7. МО поразрядные, логические &,, (С:= АВ) В соответствии с выполняемыми МО операционные элементы процессора разделяются на шины, регистры, счетчики, сумматоры (вычитатели), логические устройства, сдвигатели, преобразователи и формирователи кодов, комбинированные операционные элементы. 1°. Шина. Для передачи 1 бита данных требуется 1 сигнальная линия (1 проверка). Совокупность всех цепей, которые обеспечивают одновременную передачу всех битов слова, называется шиной. Шина реализует МО передачи. Шина, по которой передается только прямое или только инверсное значение, называется однофазной. Если по шине одновременно передается и прямое и инверсное значение, то шина называется парафазной. Если по сигнальным линиям информация может передаваться только в одном направлении, то такая сигнальная называется однонапрвленной. Если информация может передаваться в том и другом направлении, то такая шина – двунаправленная. Передача информации происходит по сигналу, который имитирует передачу. Ширина шины – количество одновременно передаваемых данных. 2. Регистры. Регистр – совокупность запоминающих элементов, которые предназначены для приема, хранения и выдачи информации. С помощью регистра выполняются МО установки, инвертирования, сдвига на заданное число разрядов. Любой регистр может подразделяться на подрегистры, которые соответствуют определенным полям слова. Над подрегистрами могут выполняться автономные операции. Выдача информации из регистра производится без потери в источнике. 3. Счетчики. Обеспечивает МО счета (прямого или обратного) Сч:=Сч±const const = 2k – степень двойки. Суммирующие счетчики (прямое) Вычитающие счетчики (обратное) Реверсирующие счетчики (то и другое направление) Счетчики строятся с использованием запоминающих элементов (регистров). Кроме МО счета счетчика можно реализовать все МО, которые характерны для регистров, то есть прием, выдачу, сдвиг кода, хранение. 4°. Сумматоры. Операционный элемент, который реализует МО: 1) С:=А+ В 2) С:=С+В – рекуррентная схема. Различают комбинационные и накапливающие сумматоры, которые реализуют соответственно (1) и (2) .  На самом деле сумматор обрабатывает три операнда: А, В – слова одной разрядности, а третий операнд однобитовый. CY.C(n:0) = A(n:0) + B(n:0)+C0 Обычно используют комбинационный сумматор, т.к. написание упрощенное. Комбинационный сумматор – техническое устройство (схема), в которой результат присутствует на выходе до тех пор, пока на входе присутствуют входные сигналы. Накапливающие сумматоры строятся на основе регистров, поэтому результат суммирования может быть считан из соответствующего выхода регистра в любой момент времени до новой МО.  5. Преобразователи кодов. Обеспечивают перекодировку значений, т.е. преобразование из одного кода в другой. Самые распространенные, преобразуют двоичный позиционный код в унитарный двоичный код – дешифрация. (Знать унитарный и позиционный бинарный код).  Если m= 2n+1–1, то такой дешифратор называется полным. В противном случае – неполным. Эти операционные элементы используются для организации связи между устройствами, в том числе, с памятью ЭВМ. Обратное преобразование (из унитарного кода в позиционный код) реализуется с помощью шифратора.  Более сложные преобразования (избинарного кода в десятичный) требуют более сложных преобразователей. 6. Вычисление значений логических условий. Эти функции операционным элементом в виде булевой функции. l(s1,s2,…,sn) si – некоторые слова, поля слов или отдельные биты слов. Функция вычисления комбинационной схемой:  Наиболее распространенными схемами для вычисления логических условий являются схемы, которые вычисляют отношение 2-хслов А и В:l (А,В) 7. Комбинированные операционные элементы. Комбинированные операционные элементы обеспечивают реализацию нескольких разнотипных МО. Комбинированные операционные элементы строятся на основе регистров, имеющих входную и выходную логику. 3.4. Каноническое построение операционных автоматов. Структура операционного автомата (состав и связь) зависит от алгоритмов выполнения машинных команд. Если структура уже задана, то один и тот же алгоритм может быть реализован по разному. Большинство операционных частей процессоров современных ЭВМ строится по некоторым устоявшимся схемам. Эти схемы называются каноническими. Одним из вариантов канонической схемы является универсальная каноническая структура операционного автомата с общими МО. Она достаточно эффективна с позиций технологического процесса, т.к. обладает высокой однотипностью узлов. В соответствии с канонической структурой, в которой машинная операция описывается в виде набора многодоступных функциональных преобразований данных. C = g(f(A),B)) g – оператор сдвига. f – оператор бинарной арифметико-логических операций h – оператор формирования инверсных кодов (дополнительного, обратного) A,B,C – слова внутри памяти операционного автомата процессора. Логические условия в этом операционном автомате представляются в виде булевой функции (z) от некоторых слов памяти операционного автомата. Каноническая структура напоминает структуру операционного модуля, для примера BC1, если убрать регистр Q. Такое каноническое построение операционного автомата заранее определяет какие МО оказываются совместимыми, т.е. структура автомата определяет состав операционной части микрокоманды. Структура определяет также последовательность выполнения МО операционной части микрокоманды. В большинстве современных процессоров в основе построения операционной части базируется на схеме с общими МО. Вопросы для самоконтроля: Назначение глобальной таблицы дескрипторов GDT. Назначение локальной таблицы дескрипторов LDT. Кэширование дескрипторов текущей задачи. Для чего применяются дескрипторы - псевдонимы. Механизм страничной организации памяти и организация подкачки (свопинга) страниц. Базовый механизм страничного управления. Двухуровневая схема трансляции адреса. Структура элементов PDE/PTE при стандартных 4-х Кб страницах. Литература: 1. В.Б. Бродин, И.И.Шагурин. Микропроцессор i486. Архитектура, программирование, интерфейс- М,: "Диалог-МИФИ", 2000. - 240с. 2. В.Л. Григорьев. Микропроцессор i486. Архитектура и программирование. Кн.1. ТОО "Транал", "Бином", 2000. - 346 с. 3. В.Л. Григорьев. Микропроцессор i486. Архитектура и программирование. Кн.2.3.4. ТОО "Транал", "Бином", 2001. - 382 с. |