КСР по ЭлМк и Т Кудрицкий С.А. Учебнометодический комплекс для обеспечения контролируемой самостоятельной работы студентов (кср) по учебной дисциплине Электроника и микропроцессорная техника

Скачать 0.79 Mb. Скачать 0.79 Mb.

|

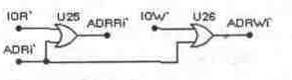

1 2 Тема 3. Регистры параллельные, сдвига, универсальные Цель работы: изучение назначения и функций регистра. Знакомство с принципом работы регистров. Оборудование: Электронная лаборатория Electronics Workbench. Краткая теория Регистры – устройства для временного хранения и преобразования информации в виде много разрядных двоичных чисел. Регистры наряду со счетчиками и запоминающими устройствами являются наиболее распространенными устройствами цифровой техники. При сравнительной простоте регистры обладают большими функциональными возможностями. Они используются в качестве управляющих и запоминающих устройств, генераторов и преобразователей кодов, счетчиков, делителей частоты, узлов временной задержки. Элементами структуры регистров являются триггеры D- или JK- типа с динамическим или статическим управлением. Одиночный триггер может запоминать (регистрировать) один разряд (бит) двоичной информации. Такой триггер можно считать одноразрядным регистром. Занесение информации в регистр называют операцией ввода или записи. Выдача информации к внешним устройствам характеризует операцию вывода или считывания. Запись информации в регистр не требует его предварительного обнуления.  Все регистры в зависимости от функциональных свойств подразделяются на две категории – накопительные (регистры памяти, хранения) и сдвигающие. В свою очередь, сдвигающие регистры делятся по способу ввода и вывода информации на параллельные и последовательно-параллельные и комбинированные, по направлению передачи (сдвига) информации – на однонаправленные и реверсивные. Рисунок 3.1 На рисунке 3.1 показана схема простейшего четырехразрядного регистра на D – триггерах, в котором информация заносится последовательно, начиная с младшего разряда. Контрольные вопросы и задания 1. Что такое регистр, какие функции он может выполнять? 2. Назовите типы регистров и их возможные применения. 3.Смодулируйте приведенную выше схему и проанализируйте работу регистра. Тема 4. Арифметико-логического устройства, аналого-цифровые преобразователи. Цель работы: ознакомление c возможностями моделирования работы арифметико-логического устройства (АЛУ). Исследование работы АЛУ на примере выполнения арифметических и логических операций. Основные понятия. АЛУ предназначено для выполнения арифметических и логических операций над многоразрядными операндами в зависимости от кодов, подавамых на управляющие входы. В вычислительных устройствах АЛУ является базовым узлом и работает в сочетании с ОЗУ, регистрами сдвига, регистрами общего назначения и др. Микросхемы АЛУ, принадлежащие к разным видам логик, функционально во многом совпадают. Так в ТТЛ-логике это микросхема К155ИП3, в К-МОП-логике микросхема 564ИП3. Аналогом микросхемы К155ИП3 в программе EWB имеется микросхема 74181. Она представляет собой четырехразрядное АЛУ. АЛУ работает в режиме выполнения логических операций при значении управляющего сигнала М=1 и в режиме выполнения арифметических операций при значении управляющего сигнала М=0. В приведенной таблице содержатся выполняемые логические и арифметические операции в зависимости от кодовой комбинации на управляющих входах S0, S1,S2, S3.

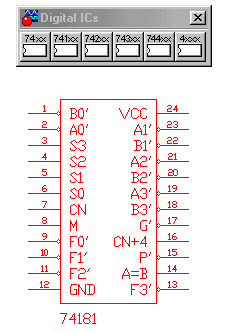

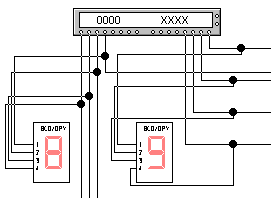

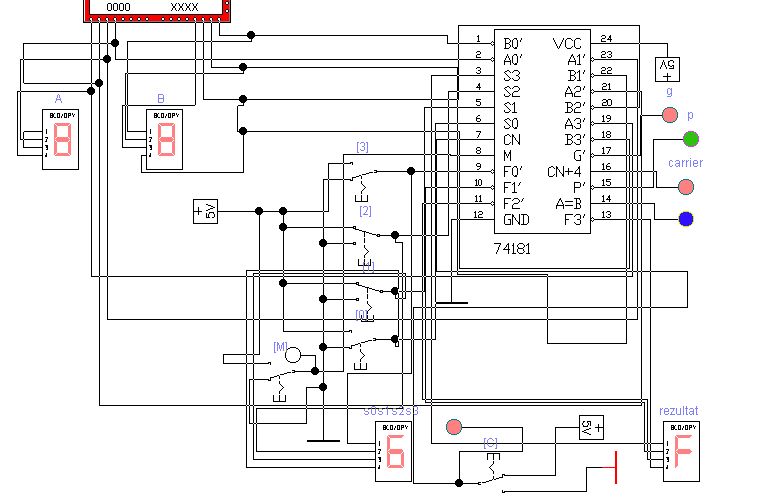

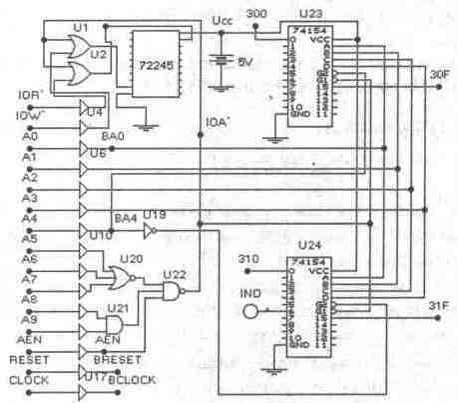

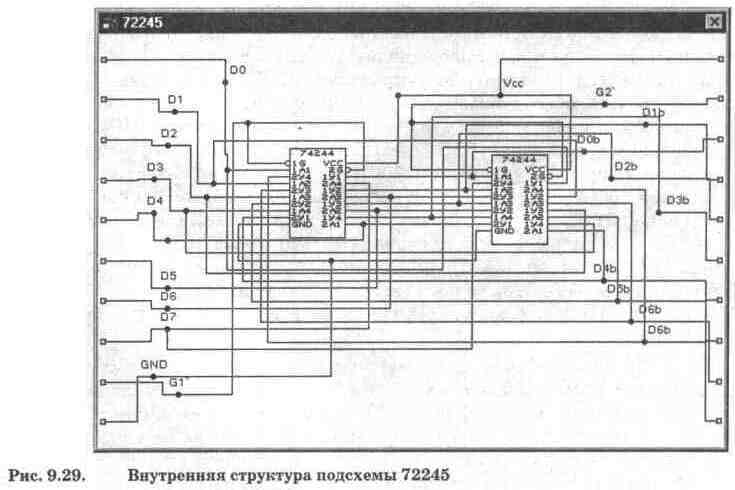

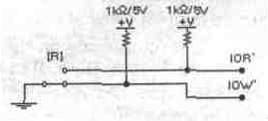

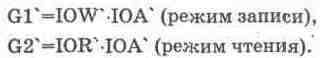

Используемые элементы EWB. На панели Digital ICs выбирается схема из множества 741хх Под номером 74181 - Четырёхразрядное АЛУ.  Задание на выполнение лабораторной работы. Подготовить микросхему АЛУ на рабочем столе. Подготовить 4 переключателя для задания режимов управления. Сигналы S подаются на входы S0.....S3 АЛУ. Ещё один переключатель используется для задания режима М. И в том и другом случае логическая 1 подаётся от 5V источника постоянного тока, логический 0 от заземления. Шестой переключатель осуществляет роль входного переноса и подключается таким же образом к входу CN. Значения четырёхразрядных операндов А и В задаются с помощью генератора слова и в шестнадцатеричном коде отображаются на алфавитно-цифровых индикаторах и подсоединяются к входам А0....А3 и В0.....В3.Н  а выходах F0....F3 формируется результат операции АЛУ. Для отображения результата к выходам F0....F3 присоединяется алфавитно-цифровой индикатор. К выходу VCC присоединить источник 5V. К входу GND подсоединить заземление. При коде 1111 на выходах F и при равенстве операндов выход А=В переводится в единичное состояние. Поскольку этот выход представляет собой каскад с открытым коллектором, то на него подаётся питание +5 вольт через резистор 1 кОм. Выход А=В совместно с выходом переноса CN+4 и выходом Р подтверждения переноса используются для формирования признаков А>B и A Изменяя состояния сигналов на управляющих входах по приведённой таблице, можно промоделировать большинство функций АЛУ, используемых в микропроцессорах.  Проведите моделирование перечисленных в таблице режимов работы АЛУ (по указанию преподавателя). Содержание отчета. Схема АЛУ, собранная в лабораторной работе. Таблица исходных операндов и результат выполнения операций в АЛУ. Тема 5. Проектирование дешифраторов устройств ввода-вывода технологической информации. Использование микропроцессорной техники в системах автоматического управления в первую очередь связано с организацией ввода-вывода. Одним из наиболее распространенных способов ввода-вывода является программно-управляемый, при котором сопряжение с системной шиной управляющей ЭВМ осуществляется набором аппаратных средств, обеспечивающих селекцию устройств ввода-вывода (УВВ) и двухсторонний обмен информацией этих устройств с управляющей ЭВМ. В популярном персональном компьютере (ПК) фирмы IBM в адресном пространстве ввода-вывода зарезервировано 32 адреса (от ЗООН до 31FH) для возможности их использования при проведении различных экспериментов по применению ПК в качестве управляющей ЭВМ. Для таких целей различными фирмами, включая и фирму IBM [18], изготавливаются так называемые макетные платы с ножевым разъемом типа ISA (см. ниже), конструкция которых позволяет размещать на ней ИМС с различным количеством выводов и затем соединять их монтажными проводниками. Некоторые платы содержат буферные элементы, селекторы адреса и шинные формирователи. Схема устройства ввода-вывода, позволяющего организовать двухстороннюю связь с 32-разрядным УВВ, приведена на рисунке 5.1. Схема несколько изменена, поскольку в библиотеке программы EWB отсутствует микросхема шинного формирователя 74245, замененная подсхемой из двух ИМС 74244 (обозначена под номером 72245), в результате чего изменена и схема управления (логические элементы U1, U2). Второе отличие заключается в замене двух ИМС 74244, используемых в оригинале в качестве однонаправленных буферов, на одиночные буферные элементы U3…U17, что вызвано крайне неудачным расположением выводов ИМС 74244. Этот недостаток вообще характерен для всех цифровых ИМС из библиотеки EWB. Достаточно взглянуть на дешифраторы U23, U24 (отечественные аналоги К133ИДЗ, К1533ИДЗ и т.п.), где входы А, В, С, D, Gl, G2 расположены с правой стороны, тогда как общепринято располагать их слева. В других ИМС входы и выходы располагаются вперемежку с обеих сторон (в том числе и в 74244). Третье отличие заключается в замене 8-разрядного компаратора 74688, отсутствующего в библиотеке EWB, на комбинацию логических элементов U20, U21, U22.  Рисунок 5.1  Рисунок 5.2 Рисунок 5.2Схема подсхемы (субблока) 72245 показана на рисунке 5.2. Подсхема 72245 может быть выполнена также на буферных элементах с тремя состояниями. Назначение сигналов системной шины IBM PC следующее: IOW\ IOR' — сигналы записи и чтения с активным низким уровнем для вывода и ввода при обмене с УВВ; АО...А9 — сигналы адресной шины; DO...D7 — сигналы шины данных (в подсхеме 72245). Во время цикла записи в УВВ микропроцессор выдает эти сигналы перед сигналом IOW', во время цикла чтения порт ввода должен обеспечить выдачу сигналов на шину данных перед сигналом IOR'; AEN — сигнал разрешения выбора адреса, вырабатывается контроллером прямого доступа к памяти (ПДП) материнской платы IBM PC; в течение цикла ПДП обращение к портам ввода-вывода запрещено, поскольку в это время возможна активизация сигналов IOW, IOR'; CLOCK (OSC) — системный тактовый сигнал синхронизации, используется по необходимости, на схеме рис. 5.8.1 не задействован; RESET — сигнал установки всех функциональных узлов системы в исходное состояние после включения питания или нажатия кнопки Reset на системном блоке; синхронизируется импульсом OSC. После передачи этих сигналов через буферные элементы к их имени добавляется префикс В, т.е. BIOW...BDO...BRESET. Сигнал IOA' — разрешение выбора адреса порта УВВ — формируется адресным селектором на ИМС U20, U21, U22 при разрешающем состоянии сигнала AEN, для которого активным является низкий уровень сигнала. На выходах О...15 дешифраторов U23, U24 формируются адресные сигналы 32 портов ввода-вывода (от ЗООН до 31FH) с активным низким уровнем. Для индикации состояния выходов в простейшем случае может быть использован светодиод IND (на схеме подключен только к одному выходу). Входы дешифраторов Gl, G2 разрешающие, при подаче на них сигналов низкого уровня (логического нуля) разрешается формирование сигнала на выходе дешифратора, определяемого двоичным кодом на адресных входах А, В, С, D. Работа с УВВ на рис. 9.28 позволяет ознакомиться с аппаратными средствами программного ввода-вывода и отработать навыки по диагностике и локализации неисправностей цифровых систем управления. Приведем примерный перечень таких работ. 1. Исследование цепи формирования сигнала IOA' и выявление (локализация) имеющейся ошибки. Для этого на рабочее поле программы поместите иконку логического преобразователя и к его входам А, В... подключите сигналы А5...А9, AEN соответственно, а к выходу OUT — сигнал IOA' (выход микросхемы U22). Затем двойным щелчком мыши разверните логический преобразователь, последовательным нажатием кнопок  получите таблицу истинности и булево выражение. После этого проанализируйте таблицу истинности, выделив двоичную комбинацию, при которой IOА'=0 (колонка OUT), а в булевом выражении — слагаемое, соответствующее этой комбинации. При этом необходимо учесть, что А=А5, B=A6...F=AEN. Найдите ошибку в схеме и исправьте ее (подсказка — нужно заменить буферный элемент для одного из сигналов). получите таблицу истинности и булево выражение. После этого проанализируйте таблицу истинности, выделив двоичную комбинацию, при которой IOА'=0 (колонка OUT), а в булевом выражении — слагаемое, соответствующее этой комбинации. При этом необходимо учесть, что А=А5, B=A6...F=AEN. Найдите ошибку в схеме и исправьте ее (подсказка — нужно заменить буферный элемент для одного из сигналов).2. Исследование цепей формирования адресов УВВ. В правый верхний угол рабочего поля программы поместите иконку генератора слова и соедините его выходные клеммы-индикаторы, начиная с правого младшего разряда, со входами АО...А7. Проанализируйте адресное пространство в диапазоне ЗООН...31FH и установите требуемое значение сигналов на входах А8, А9 и AEN, после чего подключите к ним элементы заземления или источник +5V из библиотеки Passive, имитирующие источники логического нуля и единицы соответственно. После этого на экране генератора наберите несколько чередующихся комбинаций двоичных кодов, соответствующих адресу 316Н, и в пошаговом режиме, нажимая' клавишу STEP, проверьте факт формирования низкого активного уровня на вы-1 ходе дешифратора U24, к которому подключен индикатор IND; при правильно выбранной двоичной комбинации его свечение прекращается. Аналогичным образом проверяются все остальные выходы дешифраторов. Подскажем, что для определения состояния сигналов на адресных входах А5...А9 в диапазоне адресов 300H...31FH необходимо преобразовать их шестнадца-теричный код в двоичный, заменяя каждую цифру тетрадой с весом разрядов 8-4-2-1, т.е. ЗООН=0011 0000 0000, 31FH=0011 0001 1111, откуда видно, что в указанном диапазоне адресов A9=A8=1 и А7=А6=А5=0 (отсчет адресов начинается с младшего, нулевого разряда). Следовательно, ко входам А8, А9 нужно подключить источник сигнала логической единицы (+5V), а ко входам А5, А6, А7 — заземление. 3. Исследование цепей управления шинным формирователем 72245. Для проверки правильности функционирования этого узла ко входам АО...А9 подключите источники сигналов логического нуля и логической единицы в комбинации, соответствующей адресу 316Н, а вход AEN заземлите, если не была исправлена ошибка в п. 1. При правильной коммутации после включения источника питания индикатор IND должен погаснуть. Для управления входами IOR', IOW воспользуйтесь источником напряжения с заданным внутренним сопротивлением из библиотеки Passive и переключателем из библиотеки Control, управляемого клавишей R (read — читать). Для источника питания необходимо правильно выбрать его ЭДС и внутреннее сопротивление с учетом параметров ИМС серии 155. Подскажем, что схема имитации сигналов IOR'и IOW показана на рис. 9.30. В показанном на нем положении переключателя формируется сигнал записи (чтение запрещено, поскольку на входе IOR' — сигнал логической единицы, запрещающий такой режим). При нажатии на клавишу R формируется сигнал чтения из УВВ, подключенному по адресу 316Н, при этом запись запрещена по указанным выше причинам.  Рисунок 5.3 ЭДС источника напряжения для ИМС серии 155 выбирается равной 5 В, а его внутреннее сопротивление примерно равным выходному сопротивлению базового элемента серии 155. Из рисунка 5.2 видно, что входы управления G1' шинного формирователя 72245 (разрешение записи в УВВ) и G2' (разрешение чтения из УВВ) подключены к выходам двухвходовых логических элементов ИЛИ U1 и U2 соответственно, которые в реализуют функции двухвходовых элементов И для активных инверсных сигналов на входах, т.е.  Для проверки режима записи ко входам DO...D7 формирователя 72245 подключите генератор слова, а к двум его выходам, например BDO и BD7, индикаторы из библиотеки Indie. Задавая соответствующие комбинации восьмиразрядного кода на входе, на выбранных выходах будем наблюдать передачу сигналов через шинный формирователь на УВВ, подключенном по адресу 316Н..Для проверки режима чтения из УВВ генератор слова и индикаторы меняются местами, а переключатель R в схеме на рисунке 5.3 переводится в режим формирования сигнала IOR\ Если одно УВВ работает только на прием информации (например, индикаторное устройство), а второе — только на передачу (например, опрос датчика), то они могут быть подключены к одному адресу, т.е. к одному выходу дешифратора U23 или U24, с помощью схемы на рис. 9.31, в которой расщепление адреса производится за счет селекции сигналами чтение-запись. Элементы ИЛИ U25, U26 работают аналогично U1, U2. На рисунке 5.4 ADRi' — адресный сигнал с дешифратора U23 или U24, ADRRi' — адресный сигнал только передающего УВВ, ADRWi' — только принимающего.  Рисунок 5.4 Описанные выше сигналы системной шины IBM PC относятся к первой модели этих компьютеров — IBM PC XT. Архитектура системной шины такого компьютера называлась XT BUS и в настоящее время является составной частью более совершенных архитектурных решений. Поскольку IBM PC по существу является микроЭВМ, которую можно использовать в микропроцессорных системах управления, представляется целесообразным привести краткие сведения по существующим архитектурным решениям организации внутреннего интерфейса этих микроЭВМ, описания которых заимствованы из обзора, распространяемого по FIDO fileecho XHRDDOCS под именем emhwfaqs.zip. XT-Bus — шина архитектуры XT — первая в семействе IBM PC. Относительно проста, поддерживает обмен 8-разрядными данными внутри 20-разрядного (1 Мбайт) адресного пространства (обозначается как "разрядность 8/20"), работает на частоте 4,77 МГц. Конструктив — 62-контактный разъем (слот). ISA (Industry Standard Architecture — архитектура промышленного стандарта) — основная шина PC AT (другое название — AT-Bus). Является расширением XT-Bus, разрядность — 16/24 (16 Мбайт), тактовая частота — 8 МГц, предельная пропускная способность — 5,55 Мбайт/с. Разделение IRQ (аппаратные прерывания) невозможно. Допускается нестандартная организация Bus Mastering (УВВ с возможностью автономного управления системной шиной микропроцессорной системы), но для этого нужен запрограммированный 16-разрядный канал DMA (прямой доступ к памяти). Конструктив — 62-контактный разъем XT-Bus с прилегающим к нему 36-контактным разъемом расширения. EISA (Enhanced ISA — расширенная ISA) — функциональное и конструктивное расширение ISA. Внешне разъемы имеют такой же вид, как и для ISA, и в них могут вставляться платы ISA, но в глубине разъема находятся дополнительные ряды контактов EISA, причем платы EISA имеют более высокую ножевую часть разъема с дополнительными рядами контактов. Разрядность — 32/32 (адресное пространство — 4 Гбайт), работает на частоте 8 МГц. Предельная пропускная способность — 32 Мбайт/с. Поддерживает Bus Mastering — режим управления шиной со стороны любого из устройств на шине, имеет систему арбитража для управления доступом устройств к шине, позволяет автоматически настраивать параметры устройств, возможно разделение каналов IRQ и DMA. МСА (Micro Channel Architecture — микроканальная архитектура) — шина компьютеров PS/2 фирмы IBM. He совместима ни с одной другой шиной, разрядность — 32/32, (базовая — 8/24, остальные — в качестве расширений). Поддерживает Bus Mastering, имеет арбитраж и автоматическую конфигурацию, синхронная (жестко фиксированная) длительность цикла обмена, предельная пропускная способность — 40 Мбайт/с. Конструктив — 1...3-секционный разъем (такой же, как у VLB). Первая, основная, секция — 8-разрядная (90 контактов), вторая — 16-разрядное расширение (22 контакта), третья — 32-разрядное расширение (52 контакта). В основной секции предусмотрены линии для передачи звуковых сигналов. Дополнительно рядом с одним из разъемов может устанавливаться разъем видеорасширения (20 контактов). EISA и МСА во многом идентичны, появление EISA обусловлено собственностью IBM на архитектуру МСА. VLB (VESA Local Bus — локальная шина стандарта VESA) — 32-разрядное дополнение к шине ISA. Конструктивно представляет собой дополнительный разъем (116-контактный, как у МСА) к разъему ISA. Разрядность — 32/32, тактовая частота — 25...50 МГц, предельная скорость обмена — 130 Мбайт/с; выполнена в виде расширения локальной шины процессора — большинство входных и выходных сигналов процессора передаются непосредственно VLB-платам без промежуточной буферизации. Из-за этого возрастает нагрузка на выходные каскады процессора, ухудшается качество сигналов на локальной шине и снижается надежность обмена по ней. Поэтому VLB имеет жесткое ограничение на количество устанавливаемых устройств: при частоте на шине 33 МГц — три, 40 МГц — два, 50 МГц — одно, причем желательно — интегрированное (встроенное) в системную плату (обычно контроллеры портов и дисков). PCI (Peripheral Component Interconnect — соединение внешних компонентов) — развитие VLB с приближением к EISA/MCA. Не совместима ни с какими другими, разрядность — 32/32 (расширенный вариант — 64/64), тактовая частота — до 33 МГц (PCI 2.1 — до 66 МГц), пропускная способность — до 132 Мбайт/с (264 Мбайт/с для 32/32 на 66 МГц и 528 Мбайт/с для 64/64 на 66 МГц), поддержка Bus Mastering и автоконфигурации. Количество разъемов шины на одном сегменте ограничено четырьмя. Сегментов может быть несколько, они соединяются друг с другом посредством мостов (bridge). Сегменты могут объединяться в различные топологии (дерево, звезда и т.п.). В настоящее время самая популярная шина, используется также на других компьютерах. Разъем похож на MCA/VLB, но чуть длиннее (124 контакта). 64-разрядный разъем имеет дополнительную 64-контактную секцию с собственным ключом. Все разъемы и карты к ним делятся на поддерживающие уровни напряжения питания 5 В, 3,3 В и универсальные; первые два типа должны соответствовать друг другу, универсальные карты вставляются в любой разъем. Существует также расширение MediaBus, введенное фирмой Asustek и содержащее дополнительный разъем с сигналами шины ISA. PCMCIA (Personal Computer Memory Card International Association — ассоциация производителей плат памяти для персональных компьютеров) — внешняя шина компьютеров класса NoteBook. Другое название модуля PCMCIA — PC Card. Предельно проста, разрядность — 16/26 (адресное пространство — 64 Мбайт), поддерживает автоконфигурацию, возможно подключение и отключение устройств в процессе работы компьютера. Конструктив — миниатюрный 68-контактный разъем. Контакты питания сделаны более длинными, что позволяет вставлять и вынимать карту при включенном питании компьютера. Аппаратное обеспечение внутреннего интерфейса выполняется с помощью набора микросхем — чипсетов. Chip Set — набор микросхем (чипсет). Это одна или несколько микросхем, специально разработанных для "обвязки" микропроцессора. Они содержат в себе контроллеры прерываний, прямого доступа к памяти, таймеры, систему управления памятью и шиной — все те компоненты, которые в оригинальной IBM PC собраны на отдельных микросхемах. Обычно в одну из микросхем набора входят также часы реального времени с CMOS-памятью и иногда'— контроллер клавиатуры, однако эти блоки могут присутствовать и в виде отдельных чипов. В последних разработках в состав наборов микросхем для интегрированных плат стали включаться и контроллеры внешних устройств. Внешне микросхемы чипсета выглядят, как самые большие после процессора, с количеством выводов от нескольких десятков до двух сотен. Название набора обычно происходит от маркировки основной микросхемы: OPT1495SLC, S1S471, UMC491, 182C437VX и т.п. При этом используется только код микросхемы внутри серии: например, полное наименование S1S471 — SiS85C471. В последних разработках используются и собственные имена; в ряде случаев это фирменное название (Neptun, Mercury, Triton, Viper) либо собственная маркировка чипов третьих фирм (ExpertChip, PC Chips). Тип набора в основном определяет функциональные возможности платы: типы поддерживаемых процессоров, структура/объем кэша, возможные сочетания типов и объемов модулей памяти, поддержка режимов энергосбережения, возможность программной настройки параметров и т.п. На одном и том же наборе может выпускаться несколько моделей системных (материнских) плат, от простейших до довольно сложных с интегрированными контроллерами портов, дисков, видео и т.п. Контрольные вопросы и задания 1. Можно ли рассматривать дисковод гибких дисков (дискет) как устройство ввода-вывода? Можно ли манипулятор мышь и клавиатуру также отнести к таким устройствам? 2. Что такое адресное пространство компьютера, как оно распределяется в персональном компьютере типа IBM PC XT? 3. Какова роль шинного формирователя в рассмотренном УВВ? 4. Какие сигналы управления системной шины являются основными для схемы УВВ на рисунке 5.1? 5. Проведите все рекомендованные исследования для УВВ на рисунке 5.1. 6. Учитывая стремление разработчиков и изготовителей IBM PC обеспечить их совместимость снизу вверх, можно ли утверждать, что рассмотренное УВВ будет работать в последних модификациях компьютеров? 7. Шины какого типа используются в последних модификациях IBM PC? Тема 6. Программные драйверы устройств ввода-вывода технологической информации. Задание: подготовить реферат на тему: «Программные драйверы устройств ввода-вывода технологической информации». Список литературы 1 Основной 1. Гальперин, М.В. Электронная техника/ М.В. Гальперин. - 2-е изд. - М.: ФОРУМ, 2005. -352с. 2. Гусев, В. Г. Электроника и микропроцессорная техника / В.Г. Гусев, Ю.М. Гусев. - 3-е изд. - М.: Высшая школа, 2004. - 790 с. 3. Забродин, Ю.С. Промышленная электротехника: учебник для вузов / Ю.С. Забродин. -М.: Высшая школа, 1982. - 496 с. 4. Лачин, В. И. Электротехника: учеб. пособие / В.И. Лачин. - Ростов н/Д: Феникс, 2004. -576 с. 5. Воробьев, Н.В. Микропроцессоры. Средства отладки: лабораторный практикум и задачник: учебник для техническиз вузов /Н.В. Воробьев, В.Л. Горбунов, А.В. Гуряев [и др.]; под ред. Л.Н. Преснухина. - Мн.: Выш. шк., 1987. - 287 с. 6. Вернер, Н.В. Микропроцессоры. Средства сопряжения. Контролирующие и информационно-управляющие системы: учебник для технических вузов. / В.Д. Вернер, Н.В. Воробьев, А.В. Горячев[и др.]; под ред. Л.Н. Преснухина. - Мн.: Выш. шк., 1987. -302. 7. Нестеров, П. В. Микропроцессоры. Архитектура и проектирование микро ЭВМ. Организация вычислительных процессов: учебник для вузов / П.В. Нестеров, В.Ф. Шаньгин, В.Г. Горбунов [и др.]; под ред. Л.Н. Приснухина. - Мн.: Выш. шк., 1987. - 414 с. 8. Юров, В.И. А$$етЫег: учебник для вузов / В.И. Юров. - 2-е изд. - СПб: Питер, 2006. -637 с. 9. Васильев, Н.П. Микропроцессоры. Аппаратно-рограммные средства отладки: пособие для студентов вузов / Н.П. Васильев; под ред. Л.И. Пресохина. - М.: Высш. шк., 1984. - 95 с. 10. Андреев, А.В. Основы электроники: учеб. пособие / А.В. Андреев. - Ростов н/Д: Роникс, 2003. - 416 с. Дополнительный 11. Степаненко И. П. Основы микроэлектроники (издание второе) М. Лаборатория базовых знаний, 2003г. 12. Бабаян Р. Р. Микроэлектронные устройства для обработки непрерывной информации. М. : Наука Российская академия наук институт проблем управления 2003. 1 2 |