ЭВМ и ПУ. Вычислительные машины, системы и сети - курс лекций. Вычислительные машины, системы и сети. Курс лекций

Скачать 1.45 Mb. Скачать 1.45 Mb.

|

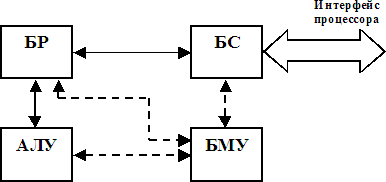

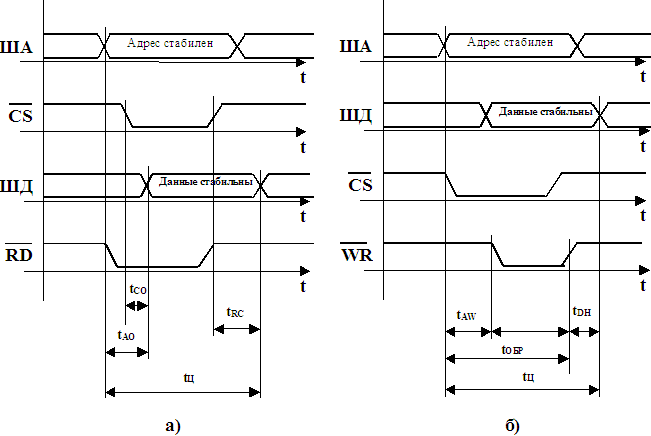

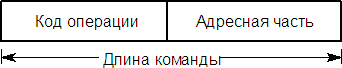

20. Функциональная и структурная организация типового ЦПСхема процессора приведена на рисунке 20.1. Процессор состоит из блока регистров БР, арифметическо-логического устройства АЛУ, блока сопряжения с интерфейсом БС блока микропрограммного управления БМУ.  Рисунок 20.1 - Структура процессора В блоке регистров БР все регистры могут быть разделены на программно-доступные и программно-недоступные. К программно-доступным регистрам относятся регистры, содержимое которых доступно по командам процессора, т. е. может использоваться в операциях, изменяться по операциям, задаваемым командами. Содержимое этих регистров не изменяется от команды к команде. К таким регистрам относятся аккумулятор; регистры базовые и индексные; множителя-частного; указателя стеков, счетчик команд и т. п. В современных процессорах программно-доступные регистры обычно не закрепляют жестко по назначению (за исключением счётчика команд и указателя стека), а предоставляют программисту несколько регистров общего назначения РОН, которые он может использовать в качестве накапливающих, базовых, индексных и т. д. Количество таких регистров колеблется от 8 до нескольких десятков (30-75). Программно-недоступные регистры являются рабочими регистрами процессора и предназначены для хранения разнообразной информации в процессе выполнения одной команды. К таким регистрам относятся в первую очередь регистр команды (РК), буферные регистры адресов (РАП) и слов (РСП), используемые при обращениях к памяти, и другие регистры. Арифметическо-логическое устройство (АЛУ) предназначено для выполнения арифметических и логических операций над словами данных и адресами. В АЛУ вырабатываются и сохраняются признаки результатов. В процессорах ЭВМ общего назначения АЛУ имеет сложную структуру и включает в себя блоки, обрабатывающие числа с фиксированной точкой различной длины, числа с плавающей точкой, десятично-кодированные числа, поля переменной длины. Для вычисления адресов (при индексной и относительной адресации) иногда используется отдельное АЛУ адресов. В мини- ЭВМ в основном АЛУ выполняются арифметические операции над числами с фиксированной точкой и логические операции. Предусматривается возможность подключения дополнительного АЛУ, выполняющего операции с плавающей точкой и другие операции расширенной арифметики. Иногда микроЭВМ дополнительные АЛУ или арифметические расширители не включаются в состав процессора, а подключаются к интерфейсу как периферийные устройства (ПУ). Основное АЛУ процессоров мини- и микроЭВМ обычно комбинированного типа с магистральной структурой. Блок сопряжения с интерфейсом (БС) обеспечивает захват шин интерфейса и выработку всех необходимых сигналов для выполнения обмена по шинам. В состав БС обычно включают контроллер шин всей ЭВМ. Интерфейс процессора включает в себя шины адреса, данных (входные и выходные или двунаправленные) и управления. Если используются одни и те же физические шины для передачи адресов и данных, то предусматриваются обычно сигналы идентификации. В состав шин управления входят шины, задающие операцию ввода или вывода (относительно процессора), и шина синхронизации.  Рисунок 20.2 - Временные диаграммы асинхронного ввода-вывода данных Процессор выполняет две операции с интерфейсом: ввод слова и вывод слова (рисунок 20.2). Для ввода слова устанавливается: на шины управления код операции «ввод», на шины адреса - адрес слова в ОЗУ (или адрес устройства ввода - вывода), затем выдается сигнал синхронизации. Временные интервалы, указанные на рис.14 нормируются и служат техническими характеристиками процессоров. В синхронных интерфейсах с постоянной задержкой относительно синхроимпульса, а в асинхронных по ответному синхроимпульсу от ОЗУ (или УВВ) осуществляется ввод информации с шины данных. Для вывода слова устанавливается: на шины управления код операции «вывод», на шины адреса - адрес слова в ОЗУ, на шины данных -данные и выдается сигнал синхронизации. Информация на шинах удерживается в течение определенного времени или до получения ответного синхроимпульса. Блок управления обеспечивает реализацию алгоритма работы процессора, выдавая последовательности управляющих сигналов в БР, АЛУ и БС и анализируя ответные осведомительные сигналы из этих блоков. 21. Понятие машинного такта, машинного цикла ЭВМ.Понятие машинной команды. Понятие кода операции.Способы адресации операндов в машинных командах.Машинный цикл: Процессор выставляет число, хранящееся в регистре счётчика команд, на шину адреса, и отдаёт памяти команду чтения Выставленное число является для памяти адресом; память, получив адрес и команду чтения, выставляет содержимое, хранящееся по этому адресу, на шину данных, и сообщает о готовности Процессор получает число с шины данных, интерпретирует его как команду (машинную инструкцию) из своей системы команд и исполняет её Если последняя команда не является командой перехода, процессор увеличивает на единицу (в предположении, что длина каждой команды равна единице) число, хранящееся в счётчике команд; в результате там образуется адрес следующей команды Снова выполняется п. 1 Данный цикл выполняется неизменно и бесконечно, и именно он называется процессом (откуда и произошло название устройства). Во время процесса процессор считывает последовательность команд, содержащихся в памяти, и исполняет их. Такая последовательность команд называется программой и представляет алгоритм полезной работы процессора. Скорость перехода от одного этапа цикла к другому определяется тактовым генератором. Тактовый генератор вырабатывает импульсы, служащие ритмом для центрального процессора. Частота тактовых импульсов называется тактовой частотой. Машинная команда представляет собой код, определяющий операцию вычислительной машины и данные, участвующие в операции. В общем случае команда должна содержать также в явной или неявной форме информацию об адресе, по которому помещается результат операции, и об адресе следующей команды. Машинная операция – это действия машины по преобразованию информации, выполняемые под воздействием одной команды. В общем виде машинная команда имеет структуру, изображенную на рис. 5.1.  Рисунок 21.1 - Общая структура Операционная часть – содержит код, который задает вид операции (сложение, умножение, передача и т.д.). Адресная часть – содержит информацию об адресах операндов и результата операции, а в некоторых случаях и следующей команды. Все машинные команды можно разделить на группы по видам выполняемых операций: операции пересылки информации внутри компьютера; арифметические операции над информацией; логические операции над информацией; операции над строками (текстовой информацией); операции обращения к внешним устройствам компьютера; операции передачи управления; обслуживающие и вспомогательные операции. Адресный код (АК) – это информация об адресе операнда, содержащаяся в команде. Исполнительный адрес (АИ) – это номер ячейки ОП, к которой производится фактическое обращение. Подразумеваемый операнд. В команде не содержится явных указаний о самом операнде или его адресе. Операнд подразумевается и фактически задается кодом операции команды. Этот метод используется редко, но иногда бывает очень удобен, например, в командах подсчета, когда к содержимому счетчика необходимо добавить фиксированное приращение. Это касается и других операций, связанных с добавлением (вычитанием) константы. Подразумеваемый адрес. В команде не содержится явных указаний об адресе участвующего в операции операнда или адресе результата операции. Так, например, при выполнении данной операции результат всегда засылается по адресу второго операнда или в другой, заранее определенный, регистр. В простейших микропроцессорах результат всегда помещается в аккумулятор. Непосредственная адресация. В команде содержится не адрес операнда, а непосредственно сам операнд. Относительная адресация, или базирование. Исполнительный адрес (АИ) определяется как сумма адресного кода команды (АК) и некоторого числа АБ, называемого базовым адресом. АИ = АБ + АК. Регистровая адресация. Это частный случай так называемой укороченной адресации, суть которой сводится к тому, что используется только небольшая группа фиксированных ячеек памяти с начальными (короткими) адресами (0000001, 0000010, 0000011 и т.д.). Такая адресация используется только совместно с другими типами адресации. Косвенная адресация. Адресный код (АК) команды указывает адрес ячейки ОП, в которой находится исполнительный адрес (АИ) операнда или команды. Автоинкрементная адресация – сначала (при каждом обращении) содержимое регистра используется как адрес операнда, а затем получает приращение, равное числу байт в элементе массива, т.е. формируется адрес следующего элемента. Автодекрементная адресация – сначала содержимое соответствующего регистра уменьшается на число, равное числу байт в элементе массива, а затем используется как адрес операнда. Стековая адресация. При рассмотрении устройств памяти отмечалось, что основной принцип работы стекового ЗУ соответствует правилу: "последний пришел – первый ушел" (имеется в виду стек LIFO). Это правило реализуется автоматически. Поэтому при операциях со стеком возможно безадресное задание операнда – команда не содержит адреса ячейки стека, а содержит только адрес (или он подразумевается) регистра или ячейки ОП, откуда слово загружается в стек или куда выгружается из стека. |