ЭВМ и ПУ. Вычислительные машины, системы и сети - курс лекций. Вычислительные машины, системы и сети. Курс лекций

Скачать 1.45 Mb. Скачать 1.45 Mb.

|

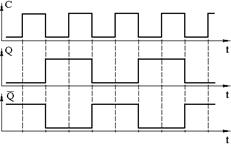

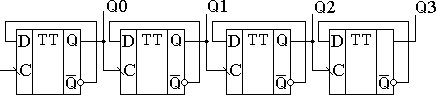

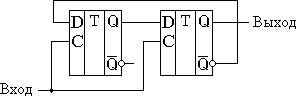

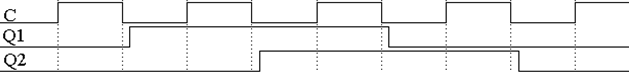

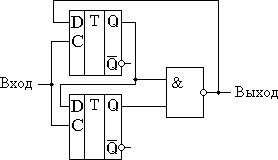

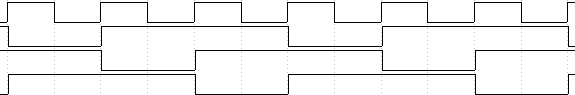

13. СчетчикОперационный узел состоит из устройств, в которых обрабатывается и хранится информация, а именно: счетчиков, регистров, шифраторов, дешифраторов, сумматоров, схем сравнения, блоков памяти и т. п. Используя набор этих устройств, можно производить обработку поступающей информации. Результатом ее обработки является выходная информация. Счётчиком называется цифровой автомат, служащий для формирования многоразрядных двоичных слов (кодов) соответствующих количеству входных импульсов. По мере поступления входных импульсов счётчик последовательно перебирает свои состояния в определённом для данной схемы порядке. Длина списка используемых состояний называется модулем пересчёта М, основанием пересчёта или ёмкостью счётчика. Одно из возможных состояний счётчика принимается как начальное или нулевое. Если счётчик начал считать с начального состояния и через каждые М входных сигналов в нём снова устанавливается начальное состояние, а на выходе счётчика формируется сигнал М–ичного переноса P, то такой счётчик называется счётчиком–делителем частоты. Частота следования М-ичного переноса P в таком счётчике меньше частоты входных импульсов ровно в M раз. Различные схемы счётчиков могут перебирать свои состояния в самом различном порядке. Порядок перебора кодов состояний счётчика определяется системой кодирования состояний счётчика как цифрового автомата. Чаще всего применяются двоичные счётчики, у которых порядок смены состояний триггеров соответствует последовательности двоичных чисел. Счетчик может перебирать свои состояния в возрастающем порядке чисел и тогда он называется суммирующим. Если счётчик перебирает свои состояния в порядке убывания двоичных чисел, то он называется вычитающим. Если под действием сигналов управления порядок перебора может изменяться на противоположный, то счётчик называется реверсивным. Счётчики строятся с использованием синхронизированных триггеров. Если несколько триггеров блока памяти имеют общий синхросигнал, то они образуют синхронный счётчик. Несколько синхронных счётчиков соединённых по схеме подачи синхросигналов последовательно образуют асинхронный счётчик. В этом случае сигнал выходного переноса предыдущего счётчика используется как сигнал синхронизации последующего счётчика. Асинхронные счетчики. Простейший вид счётчика - двоичный может быть построен на основе T-триггера. T-триггер изменяет своё состояние на прямо противоположное при поступлении на его вход синхронизации импульсов. Для реализации T-триггера воспользуемся универсальным D-триггером с обратной связью, как это показано на рисунке 13.1.  Рисунок 13.1 Реализация счетного T-триггера на универсальном D-триггере. Так как эта схема, как мы уже рассматривали ранее, при поступлении на вход импульсов меняет свое состояние на противоположное, то её можно рассматривать как счётчик, считающий до двух. Временные диаграммы сигналов на входе и выходах T-триггера приведены на рисунке 13.2.  Рисунок 13.2 Временные диаграммы сигналов на входе и выходах T-триггера. Обычно требуется посчитать большее количество импульсов. В этом случае можно использовать выходной сигнал первого счетного триггера как входной сигнал для следующего триггера, то есть соединить триггеры последовательно. Так можно построить любой счётчик, считающий до максимального числа, кратного степени два. Схема счётчика, позволяющего посчитать любое количество импульсов, меньшее шестнадцати, приведена на рисунке 13.3. Количество поступивших на вход импульсов можно узнать, подключившись к выходам счётчика Q0 … Q3. Это число будет представлено в двоичном коде.  Рисунок 13.3 Схема четырёхразрядного счётчика, построенного на универсальных D-триггерах. Синхронные счётчики. В рассмотренных схемах делителей частоты быстродействие всей схемы определяется временем распространения сигнала от входа до выхода самого старшего разряда. При этом получается, что чем больше требуемый коэффициент деления, тем больше двоичных разрядов счётчика требуется для реализации этого делителя. Тем большее время требуется для распространения сигнала от входа синхронизации счётчика, до его выхода, и тем меньше будет предельная частота, которую можно подавать на вход этого делителя. Первая схема, которую мы рассмотрим - это схема кольцевого счётчика. Такой счётчик можно построить на основе сдвигового регистра. Схема кольцевого счётчика приведена на рисунке 13.4.  Рисунок 13.4 Схема кольцевого счетчика. Рассмотрим работу этой схемы. Пусть первоначально в счетчике записано число 002. После первого же тактового импульса состояние счётчика станет равным 102, после второго - 112. Временные диаграммы этой схемы приведены на рисунке 13.5.  13.5 - Временные диаграммы к кольцевому счетчику. В результате анализа временных диаграмм можно определить, что коэффициент деления схемы кольцевого счётчика будет равен: Кд = 2*n. Для того чтобы избежать неправильной работы счётчика в этот счётчик можно ввести схему контроля правильной работы. В простейшем случае это может быть обычный логический элемент “И-НЕ”. Этот элемент будет контролировать состояние счётчика, соответствующее единицам во всех его разрядах. Схема 2-разрядного счётчика со схемой проверки правильности его работы приведена на рисунке 13.6.  Рисунок 13.6 - Схема 2-разрядного счетчика с проверкой правильности его работы. В этой схеме триггеры счётчика при поступлении импульсов на тактовый вход последовательно заполняются единицами. Как только все триггеры будут заполнены единицами, на выходе логического элемента “2И-НЕ” появится уровень логического нуля. При поступлении следующего тактового импульса этот ноль будет записан в первый триггер счётчика. В дальнейшем работа счётчика повторяется. Временные диаграммы сигналов на выходах этого счётчика приведены на рисунке 13.7.  Рисунок 13.7 – Временные диаграммы. |