ЭВМ и ПУ. Вычислительные машины, системы и сети - курс лекций. Вычислительные машины, системы и сети. Курс лекций

Скачать 1.45 Mb. Скачать 1.45 Mb.

|

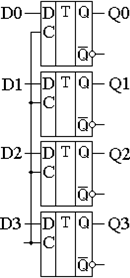

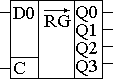

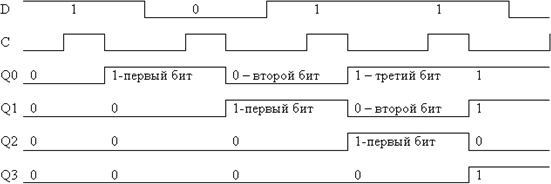

11. ДемультиплексорОперационный узел состоит из устройств, в которых обрабатывается и хранится информация, а именно: счетчиков, регистров, шифраторов, дешифраторов, сумматоров, схем сравнения, блоков памяти и т. п. Используя набор этих устройств, можно производить обработку поступающей информации. Результатом ее обработки является выходная информация. Демультиплексорами называются устройства, которые позволяют подключать один вход к нескольким выходам. Демультиплексор можно построить на основе точно таких же схем логического "И", как и при построении мультиплексора. Существенным отличием от мультиплексора является возможность объединения нескольких входов в один без дополнительных схем. Однако для увеличения нагрузочной способности микросхемы, на входе демультиплексора для усиления входного сигнала лучше поставить инвертор. Схема демультиплексора приведена на рисунке 1.1. В этой схеме для выбора конкретного выхода демультиплексора, как и в мультиплексоре, используется двоичный дешифратор.  Рисунок 11.1 – Схема демультиплексора Однако, если рассмотреть принципиальную схему самого дешифратора, то можно значительно упростить демультиплексор. Достаточно просто к каждому логическому элементу 'И', входящему в состав дешифратора просто добавить ещё один вход – In. Такую схему часто называют дешифратором с входом разрешения работы. Условно-графическое изображение демультиплексора приведено на рисунке 11.2.  Рисунок 11.2 Условно графическое обозначение демультиплексора с четырьмя выходами. В этом обозначении вход In обозначен как вход E, а выходы не названы никак, оставлены только их номера. 12. РегистрОперационный узел состоит из устройств, в которых обрабатывается и хранится информация, а именно: счетчиков, регистров, шифраторов, дешифраторов, сумматоров, схем сравнения, блоков памяти и т. п. Используя набор этих устройств, можно производить обработку поступающей информации. Результатом ее обработки является выходная информация. Регистром называется схема, служащая для запоминания многоразрядных двоичных слов (кодов) и состоящая из необходимого количества триггеров. Различают: Параллельные регистры Последовательные регистры Универсальные регистры Параллельный регистр служит для запоминания многоразрядного двоичного (или недвоичного) слова. Количество триггеров, входящее в состав параллельного регистра определяет его разрядность. Схема четырёхразрядного параллельного регистра приведена на рисунке 12.1, а его условно-графическое обозначение - на рисунке 12.2.  Рисунок 12.1 - Схема параллельного регистра. В условно-графическом обозначении возле каждого входа D указывается степень двоичного разряда, который должен быть запомнен в этом триггере регистра. Точно таким же образом обозначаются и выходы регистра. То, что микросхема является регистром, указывается в центральном поле условно-графического обозначения символами RG. В приведённом на рисунке 12.2 условно-графическом обозначении параллельного регистра инверсные выходы триггеров не показаны. В микросхемах регистров инверсные выходы триггеров часто не выводятся наружу для экономии количества выводов корпуса.  Рисунок 12.2 - Условно-графическое обозначение параллельного регистра. При записи информации в параллельный регистр все биты (двоичные разряды) должны быть записаны одновременно. Поэтому все тактовые входы триггеров, входящих в состав регистра, объединяются параллельно. Для уменьшения входного тока вывода синхронизации C на этом входе в качестве усилителя часто ставится инвертор. Следует помнить, что назначение разрядов является условным. Если по каким либо причинам (например, с точки зрения разводки печатной платы) удобно изменить нумерацию разрядов, то это можно свободно сделать. При перенумерации входов регистров нужно не забывать, точно таким же образом, изменить номера выходов параллельного регистра. Для реализации параллельного регистра можно использовать как триггеры с статическим, так и с динамическим входом синхронизации. В переводной литературе при использовании для построения параллельного регистра триггеров-защелок этот регистр, в свою очередь, называют регистром-защелкой. При использовании регистров со статическим входом тактирования следует соблюдать осторожность, так как при единичном потенциале на входе синхронизации C. сигналы с входов регистра будут свободно проходить на его выходы. В таких случаях обычно используется двухтактная синхронизация, подобная рассмотренной в главе, посвященной использованию одновибраторов. Последовательные регистры Кроме параллельного соединения триггеров для построения регистров используются последовательное соединение этих элементов. Последовательный регистр (регистр сдвига) обычно служит для преобразования последовательного кода в параллельный и наоборот. Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется большое количество соединительных проводников. Если двоичные разряды последовательно бит за битом передавать по одному проводнику, то можно значительно сократить размеры соединительных линий на плате (и размеры корпусов микросхем). Принципиальная схема последовательного регистра, собранного на основе D?триггеров и позволяющего осуществить преобразование последовательного кода в параллельный, приведена на рисунке 12.3.  Рисунок 12.3 - Схема последовательного регистра В этом регистре триггеры соединены последовательно, то есть выход первого соединён с входом второго и т.д. Условно-графическое изображение рассмотренного последовательного регистра приведено на рисунке 12.4.  Рисунок 12.4. Обозначение последовательного регистра на принципиальных схемах. Входы синхронизации в последовательных регистрах, как и в параллельных, объединяются. Это обеспечивает одновременность смены состояния всех триггеров, входящих в состав последовательного регистра. Преобразование последовательного кода в параллельный производится следующим образом. Отдельные биты двоичной информации последовательно подаются на вход D0. Каждый бит сопровождается отдельным тактовым импульсом, который поступает на вход синхронизации C. После поступления первого тактового импульса логический уровень, присутствующий на входе D0, запоминается в первом триггере и поступает на его выход, а так как он соединён с входом второго триггера, то и на его вход. После поступления второго тактового импульса логический уровень, присутствующий на входе второго триггера, запоминается в нем и поступает на его выход, а так как он соединён с входом третьего триггера, то и на его вход. Одновременно следующий бит запоминается в первом триггере. После поступления четвертого тактового импульса в триггерах регистра будут записаны уровни бит, которые последовательно присутствовали на входе D0. Теперь этими битами можно воспользоваться, например, для отображения на индикаторах. Пусть на вход регистра поступает сигнал, временная диаграмма которого изображена на рисунке 12.5, тогда состояние выходов этого регистра будет последовательно принимать значения, записанные в таблице 12.1.  Рисунок 12.5 - Временная диаграмма работы сдвигового регистра. На рисунке 12.5 вместе с логическими уровнями записываются значения бит, которые передаются по соединительной линии или присутствуют на выходах сдвигового регистра.  Таблица 12.1 Универсальные регистры Регистры сдвига выполняют обычно как универсальные последовательно-параллельные микросхемы. Это связано с необходимостью записи в регистр параллельного двоичного кода при преобразовании параллельного кода в последовательный. Переключение регистра из параллельного режима работы в последовательный и наоборот осуществляется при помощи мультиплексора (коммутатора). Использование коммутатора позволяет входы триггеров регистра либо подключать к внешним выводам микросхемы, либо подключать к выходу предыдущего триггера. |