ЭВМ и ПУ. Вычислительные машины, системы и сети - курс лекций. Вычислительные машины, системы и сети. Курс лекций

Скачать 1.45 Mb. Скачать 1.45 Mb.

|

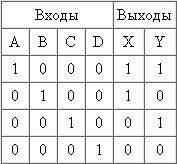

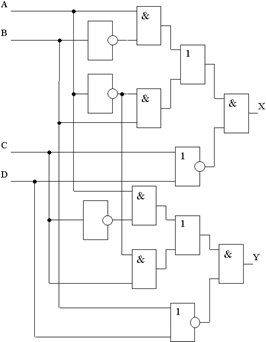

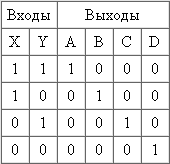

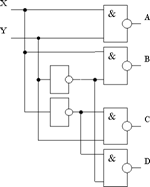

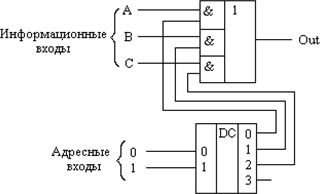

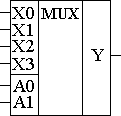

8. ШифраторыОперационный узел состоит из устройств, в которых обрабатывается и хранится информация, а именно: счетчиков, регистров, шифраторов, дешифраторов, сумматоров, схем сравнения, блоков памяти и т. п. Используя набор этих устройств, можно производить обработку поступающей информации. Результатом ее обработки является выходная информация. Шифратор - это логическая схема с N входами и М выходами (М Назначение шифратора - выдавать на выходе информацию о том, на какой из входов подан сигнал, используя при этом кодовое слово, содержащее минимум двоичных разрядов, требующееся для этого задания. Один из простейших примеров шифратора является шифратор, имеющий четыре входа и два выхода. Этот пример мы и рассмотрим. Составим таблицу, в которой каждому входному сигналу сопоставим последовательность из двух выходных сигналов.  Рисунок 8.1 – Таблица истинности На основании данной таблицы истинности составим формулу для функций X и Y: На основании полученных функций построим логическую схему. Схема должна иметь четыре входа для переменных А, В, C, D и два выхода для функций X, Y. Схема должна иметь четыре входа и два выхода.  Рисунок 8.2 – Логическая схема шифратора 9. ДешифраторОперационный узел состоит из устройств, в которых обрабатывается и хранится информация, а именно: счетчиков, регистров, шифраторов, дешифраторов, сумматоров, схем сравнения, блоков памяти и т. п. Используя набор этих устройств, можно производить обработку поступающей информации. Результатом ее обработки является выходная информация. Дешифратор - преобразователь кодов, выполняющий преобразование входных двоичных кодов в выходной унитарный код. Унитарный код двоичного n – разрядного числа представляется 2n разрядами, только один из разрядов которого равен 1 (или 0). Условное описание дешифратора задаётся формулой nxm (n на m), для полного дешифратора это формула nx2n. Примерами полных являются дешифраторы: 1x2, 2x4, 3x8, 4x16. Рассмотрим пример. Составим таблицу, в которой каждому выходному сигналу сопоставляется последовательность из двух входных сигналов.  Рисунок 9.1 – Таблица истинности На основании данной таблицы истинности составим формулу для функций A, B, C и D:  На основании полученных функций построим логическую схему. Схема должна иметь два входа и четыре выхода.  Рисунок 9.2 – Логическая схема дешифратора 10. МультиплексорОперационный узел состоит из устройств, в которых обрабатывается и хранится информация, а именно: счетчиков, регистров, шифраторов, дешифраторов, сумматоров, схем сравнения, блоков памяти и т. п. Используя набор этих устройств, можно производить обработку поступающей информации. Результатом ее обработки является выходная информация. Мультиплексором называется комбинационная схема, имеющая m+2m входов и один выход, где m – количество адресных входов, а 2m – количество информационных входов мультиплексора. Адреса представляются в двоичном коде и им присваивается номер j. Каждому адресу с номером j соответствует свой информационный вход Aj , сигнал с которого при данном адресе проходит на выход. Основным назначением мультиплексора является коммутация 2m входных сигналов на один выход. Таким образом, мультиплексор выполняет функцию где X – двоичный код адреса; Aj – входные информационные сигналы мультиплексора; Kj(X) – конституенты 1, принимающие значения, равные 1 на единственном наборе переменных X = j. Условное описание мультиплексора задаётся формулой 2mx1. Примерами являются мультиплексоры: 2x1, 4x1, 8x1, 16x1. В состав мультиплексора обычно включают двоичный дешифратор, как показано на рисунке 10.1. Это позволяет управлять переключением информационных входов при помощи двоичных кодов, подаваемых на управляющие входы. Количество информационных входов в таких схемах выбирают кратным степени числа два.  Рисунок 10.1 – Схема подключения мультиплексора с дешифратором Условно графическое обозначение четырёхвходового мультиплексора с двоичным управлением приведено на рисунке 10.2. Входы A0 и A1 являются управляющими входами мультиплексора, определяющими адрес входного сигнала, который будет соединён с выходным выводом мультиплексора Y. Сами входные сигналы обозначены как X0, X1, X2 и X3.  Рисунок 10.2 - Четырёхвходовой мультиплексор |