Электротехника 3збАСУп. Запоминающие элементы

Скачать 282.88 Kb. Скачать 282.88 Kb.

|

|

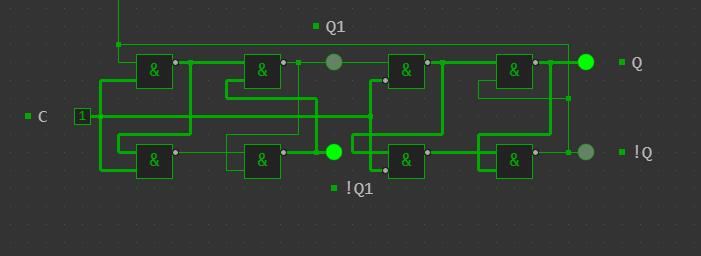

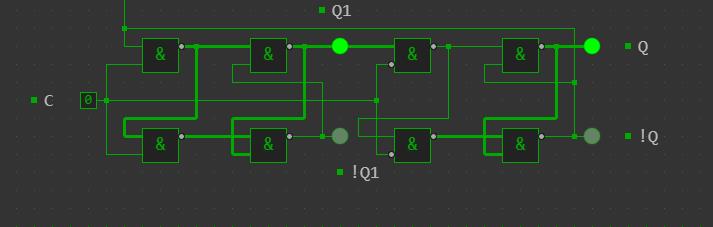

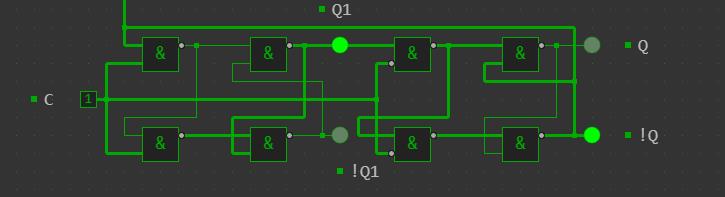

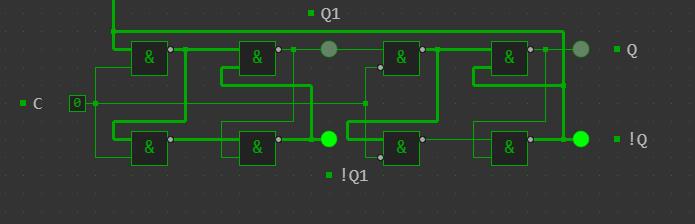

М  ОСКОВСКИЙ АВТОМОБИЛЬНО-ДОРОЖНЫЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ ОСКОВСКИЙ АВТОМОБИЛЬНО-ДОРОЖНЫЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙУНИВЕРСИТЕТ (МАДИ) Кафедра «АСУ» РАСЧЕТНО-ГРАФИЧЕСКАЯ РАБОТА по дисциплине «Электроника» на тему «Запоминающие элементы» Выполнил студент группы 3ЗбАСУп Ганиев А.Н Проверил доцент, к.т.н. Матюхина Е.Н. Москва 2019 Содержание. Введение 3 Условие задания 4 Логическая схема 5 Таблица переходов 5 Временная диаграмма 6 Моделирование работы 6 Заключение 8 Список литературы 9 Введение. В состав всех интегральных систем цифровых элементов входят микросхемы, на которых реализованы различные типы триггеров. Триггер — это запоминающий элемент с двумя (или более) устойчивыми состояниями, изменение которых происходит под действием входных сигналов и предназначен для хранения одного бита информации. Работа любого триггера описывается в виде таблицы переходов, которая отражает зависимость состояния триггера от логических сигналов на его входах. RS-триггер является запоминающим элементом, который хранит один двоичный разряд информации. RS-триггер получил название по названию своих входов. Вход S (Set — установить англ.) позволяет устанавливать выход триггера Q в единичное состояние (записывать единицу). Вход R (Reset — сбросить англ.) позволяет сбрасывать выход триггера Q (Quit — выход англ.) в нулевое состояние (записывать ноль). Различают асинхронные и синхронизируемые RS-триггеры по способу управления, а так же однотактные и двухтактные по структуре. Работа любого триггера описывается в виде таблицы переходов, которая отражает зависимость состояния триггера от логических сигналов на его входах. Условие задания. 1. Построить логическую схему двухтактного триггера с дополнительными асинхронными входами установки в «0» и/или в «1» в заданной элементной базе. 2. Построить таблицу переходов с указанием всех возможных режимов работы триггера. 3. Построить временную диаграмму работы триггера, в которой отразить все возможные режимы и вписать в таблицу переходов № машинных тактов, соответствующих каждому режиму. 4. Правильность построения логической схемы проверить путем моделирования. Вариант 3-А, элементный базис «И-НЕ»      Q TT         T Логическая схема. Построим логическую схему двухтактного асихронный Т-триггер на основе Д-триггера в электрическом базисе «И-НЕ».                 Q Q1 & & & & &                                   C               & & & & 1                    Q Q1 Таблица переходов. Построим таблицу переходов двухтактного асинхронного Т-тригера

Временная диаграмма. Построим временную диаграмму работы двухтактного асихронный Т-триггер на основе Д-триггера.        0 1

Моделирование работы. Выполним моделирование работы двухтактного двухтактного асихронный Т-триггер на основе Д-триггера. https://simulator.io/board/4yzMzdElVc/2 Такт №0   Такт №1   Заключение. RS-триггеры могут быть реализованы на различных логических элементах. При этом их логика работы не изменяется. В то же самое время триггеры часто выпускаются в виде готовых микросхем (или реализуются внутри блоков интегральных схем в виде готовых модулей. При выполнении данной работы был изучен двухтактный синхронный RS-триггер с асинхронными установочными входами: Была построена его логическая схема в элементом базисе «И-НЕ». Построена таблица переходов данного триггера Построена временная диаграмма работы данного триггера Работа триггера была смоделирована на сайте http://simulator.io Список литературы. 1. Александриди Т.М., Матюхин Б.Н., Матюхина Е.Н. Организация ЭВМ и систем. М.: МАДИ, 2010 г. 2. Микушин А.В., Сажнев А.М., Сединин В.И. Цифровые устройства и микропроцессоры. СПб, БХВ-Петербург, 2010. 3. Угрюмов Е. П. Цифровая схемотехника. СПб, БХВ-Петербург, 2010. 4. Дж. Ф. Уэкерли Проектирование цифровых устройств. М, Постмаркет, 2002. |

C

C

Q1

Q1

Q

Q

Q

Q

Q

Q