Логические элементы. логические элементы ЭВМ. Базовые логические операции и схемы конъюнкция, дизъюнкция, отрицание. Таблицы истинности. Схемные логические элементы регистры, триггеры, сумматоры, мультиплексор, демультиплексор, шифратор, дешифратор, компаратор.

Скачать 0.8 Mb. Скачать 0.8 Mb.

|

|

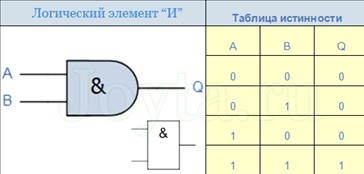

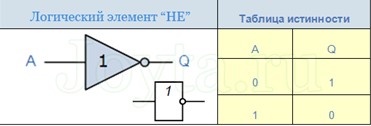

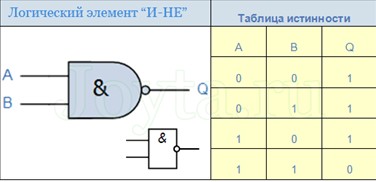

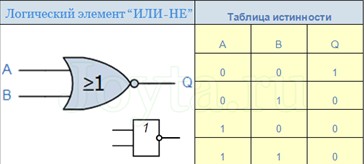

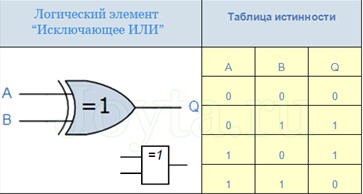

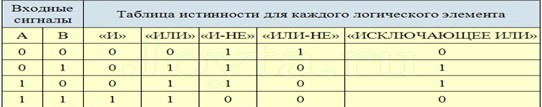

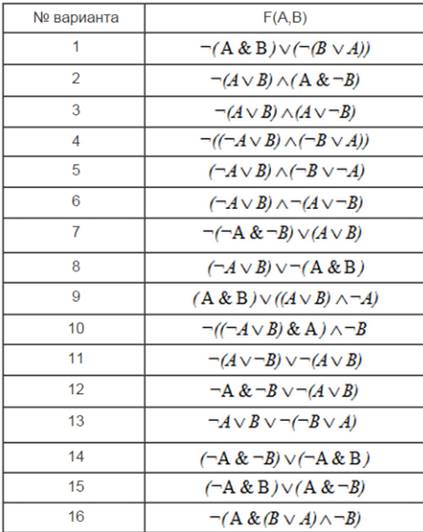

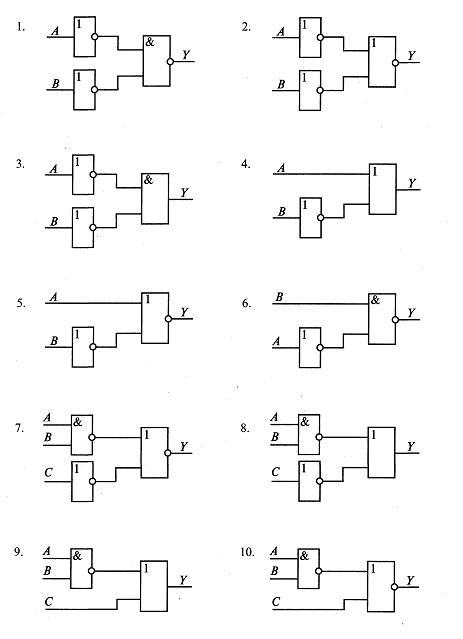

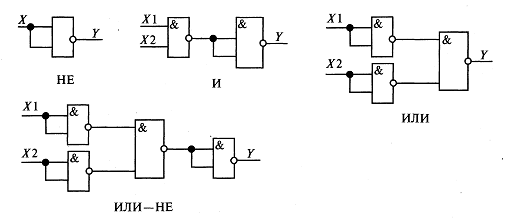

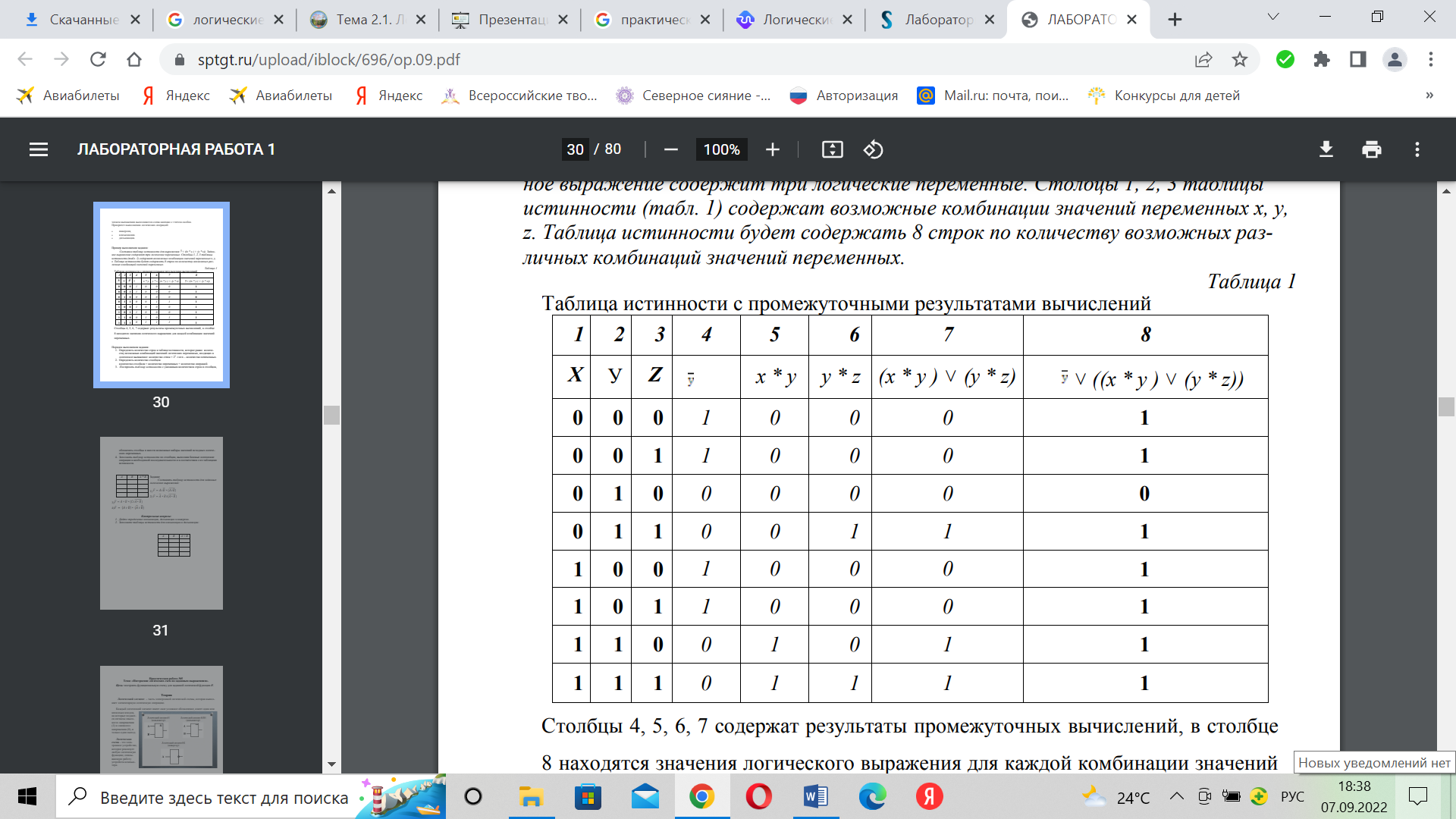

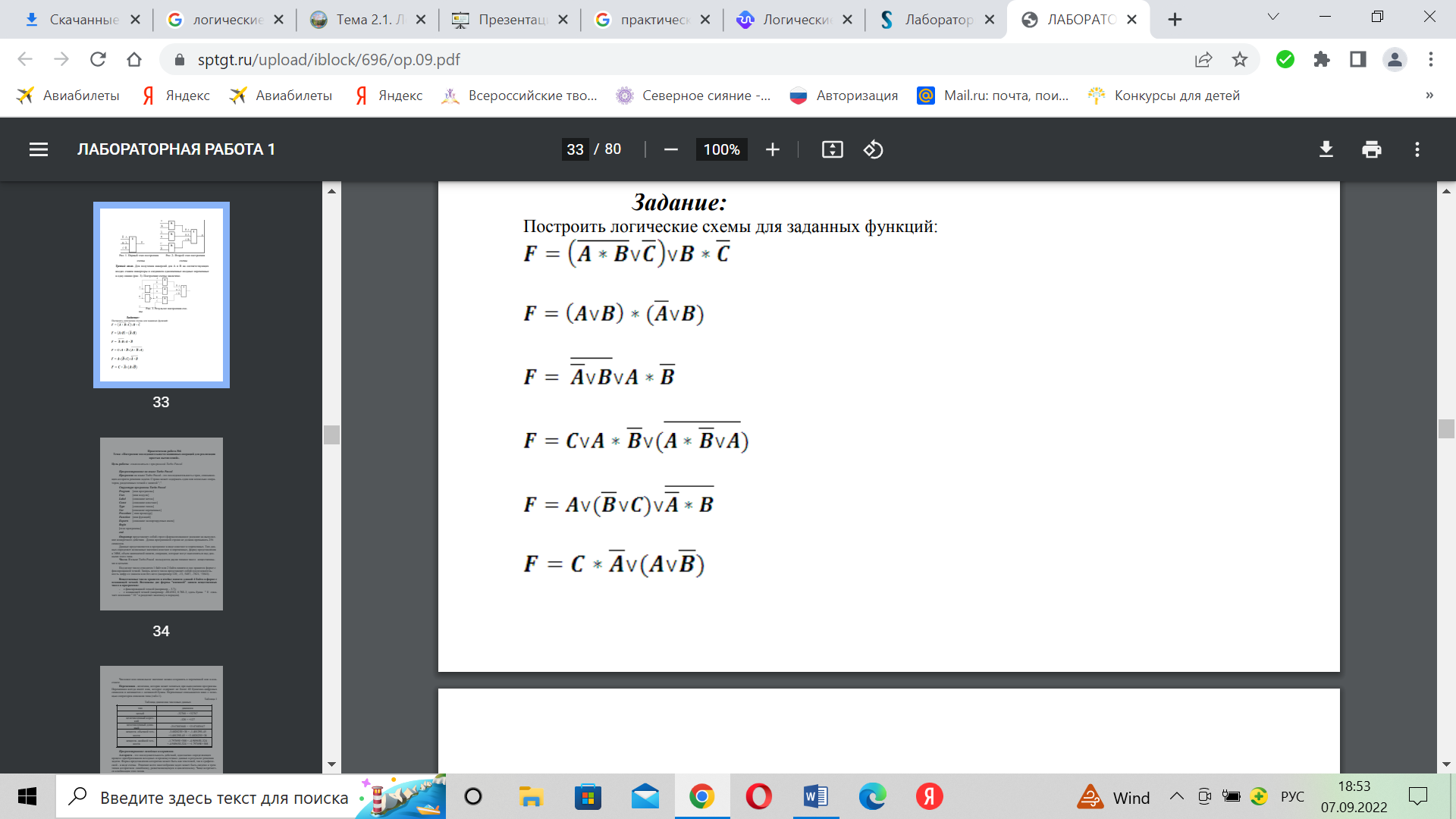

Тема 2.1. Логические основы ЭВМ, элементы и узлы Базовые логические операции и схемы: конъюнкция, дизъюнкция, отрицание. Таблицы истинности. Схемные логические элементы: регистры, триггеры, сумматоры, мультиплексор, демультиплексор, шифратор, дешифратор, компаратор. Принципы работы, таблица истинности, логические выражения, схема. Каждая логическая связка рассматривается как операция над логическими высказываниями и имеет свое название и обозначение: НЕ- Операция, выражаемая словом "не", называется отрицанием и обозначается чертой над высказыванием (или знаком). Высказывание истинно, когда A ложно, и ложно, когда A истинно. Пример. "Луна — спутник Земли" (А); "Луна — не спутник Земли" (A). И Операция, выражаемая связкой "и", называется конъюнкцией (лат. Conjunctio — соединение) или логическим умножением и обозначается точкой " . " (может также обозначаться знаками или &). Высказывание А . В истинно тогда и только тогда, когда оба высказывания А и В истинны. Например, высказывание "10 делится на 2 и 5 больше 3" истинно, а высказывания "10 делится на 2 и 5 не больше 3", "10 не делится на 2 и 5 больше 3", "10 не делится на 2 и 5 не больше 3" — ложны. ИЛИ Операция, выражаемая связкой "или" (в неисключающем смысле этого слова), называется дизъюнкцией (лат. disjunctio — разделение) или логическим сложением и обозначается знаком v (или плюсом). Высказывание А v В ложно тогда и только тогда, когда оба высказывания А и В ложны. Например, высказывание "10 не делится на 2 или 5 не больше 3" ложно, а высказывания "10 делится на 2 или 5 больше 3", "10 делится на 2 или 5 не больше 3", "10 не делится на 2 или 5 больше 3" —истинны. Элемент «И» Для логического элемента «И» выход Q будет содержать лог.1, только если на оба входа («А» и «В») будет подан сигнал лог.1   Элемент «ИЛИ» Выход Q, элемента «ИЛИ», будет иметь лог.1, если на любой из двух входов или же на оба входа сразу подать лог.1   Элемент «НЕ» В данном случае выход Q, логического элемента «НЕ», будет иметь сигнал противоположный входному сигналу.   Элемент «И-НЕ» На выходе Q элемента «И-НЕ» будет лог.1 если на обоих входах одновременно отсутствует сигнал лог.1   Элемент «ИЛИ-НЕ» Только если на оба входа логического элемента «ИЛИ-НЕ» подать лог.0 мы получим на его выходе Q сигнал соответствующий лог.1   Элемент «Исключающее ИЛИ» В данном случае выход Q будет содержать лог.1, если на вход элемента «Исключающее ИЛИ» поданы два противоположных друг другу сигнала.   Подведем итог, собрав все полученные ранее результаты работы логических элементов в единую таблицу истинности:   Триггером называют устройство, имеющее два устойчивых состояния, способное под воздействием внешних сигналов переходить из одного состояния в другое. Свое состояние триггер может сохранять сколь угодно долго. Поэтому он может использоваться в качестве элемента памяти ёмкостью 1 бит. Схему с двумя состояниями можно легко построить на основе усилителя с глубокой положительной обратной связью аналогично автогенератору. Автогенераторы гармонических колебаний имеют узкополосную функцию передачи в петле обратной связи. В результате условие баланса фаз и амплитуд выполняется только на одной частоте, на которой и возникают колебания. В триггерах используют петлю с широкой полосой, начинающуюся с нулевой частоты. Это легко получить, если использовать усилитель постоянного тока или логический элемент. Усилители образуют регенеративное кольцо из двух инверторов, охваченных глубокой положительной обратной связью. Поэтому переход из одного состояния в другое происходит лавинообразно за очень короткое время. Триггер имеет два выхода: прямой Q и инверсный Q-. Состояние триггера определяют по значению сигнала на прямом выходе Q. Значения сигналов на прямом и инверсном выходах всегда противоположны. Реальные логические элементы практически всегда обладают значительным усилением триггеры очень удобно строить на основе схем И-НЕ или ИЛИ-НЕ. Регистрами называют устройства, предназначенные для приема, хранения и передачи информации. Последняя в регистре хранится в виде двоичного кода, каждому разряду которого соответствует свой элемент памяти (разряд регистра), выполненный на основе триггеров RS-, JK-, или D-типа. Классификацию регистров можно провести по различным признакам, важнейшими из которых являются способ ввода-вывода информации и характер представления вводимой и выводимой информации. По способу ввода-вывода информации различают параллельные, последовательные и параллельно-последовательные регистры. В регистрах памяти и ввод информации и ее вывод осуществляются в параллельном коде. При этом время ввода (вывода) всего числа равно времени ввода (вывода) одного разряда. В регистрах сдвига число вводится и выводится последовательно разряд за разрядом. Время ввода (вывода) m-разрядного двоичного числа в таких регистрах определяется величиной mTc, где Tc- период следования тактовых импульсов, осуществляющих ввод (вывод) информации. В параллельно-последовательном регистре ввод числа может осуществляться в параллельном коде, а вывод - в последовательном или наоборот. По характеру представления вводимой и выводимой информации различают регистры однофазного и парафазного типов. В однофазных регистрах информация вводится в прямом либо в обратном кодах, а в парафазных - одновременно и в прямом и в обратном. Регистры первого типа строятся на основе D-триггеров, второго - на основе RS- или JK-триггеров. Вывод информации из регистров обоих типов может осуществляться в прямом и в обратном кодах. Сумматоромназывается узел ЭВМ, предназначенный для арифметического сложения кодов. Сумматоры в зависимости от используемых логических схем различаются на комбинационные и накапливающие. Комбинационный сумматор представляет собой комбинационную схему, которая формирует суммы слагаемых, подаваемых одновременно на входы схемы, и не имеет в своем составе элементов памяти. Накапливающие сумматоры имеют память, в которой накапливают результаты суммирования. По числу входов различают полусумматоры, одно и многоразрядные (параллельные) сумматоры. В зависимости от того, как организованы межразрядные переносы, сумматоры делятся на сумматоры с последовательным, параллельным и групповыми переносами. В зависимости от системы счисления, сумматоры бывают двоичные, десятичные и прочие. Основу всех сумматоров составляют одноразрядные сумматоры. Причем, сложение n-разрядных чисел осуществляется с помощью n одноразрядных сумматоров коммутацией цепей их переноса. Одноразрядные сумматоры. Одноразрядные сумматоры предназначены для сложения одноименных разрядов двух слагаемых (хiи уi) с учетом переноса из предыдущего разряда (Рi-1) и вырабатывают в том же машинном такте значения суммы (Si) и переноса в следующий разряд (Pi). Другими словами одноразрядный сумматор складывает три бита xi, yiи Рi-1и формирует Siи Рi. Сумматоры, в которых при сложении двух слагаемых (х и у) не учитывается перенос из младшего разряда, называютполусумматорами. Полусумматор имеет два входа (xiи yi) и два выхода Рiи Si. Мультиплексор - это устройство, которое осуществляет выборку одного из нескольких входов и подключает его к своему единственному выходу, в зависимости от состояния двоичного кода. Другими словами, мультиплексор - переключатель сигналов, управляемый двоичным кодом и имеющий несколько входов и один выход. К выходу подключается тот вход, чей номер соответствует управляющему двоичному коду. Ну и частное определение: мультиплексор - это устройство, преобразующее параллельный код в последовательный. Самый большой элемент здесь это элемент И-ИЛИ на четыре входа. Квадратики с единичками - инверторы. Разберем выводы. Те, что слева, а именно D0-D3, называются информационными входами. На них подают информацию, которую предстоит выбрать. Входы А0-А1 называются адресными входами. Сюда и подается двоичный код, от которого зависит, какой из входов D0-D3 будет подключен к выходу, на этой схеме обозначенному как Y. Вход С – синхронизация, разрешение работы. Демультиплексор - устройство, обратное мультиплексору. Т. е., у демультиплексора один вход и много выходов. Двоичный код определяет, какой выход будет подключен ко входу. Другими словами, демультиплексор - это устройство, которое осуществляет выборку одного из нескольких своих выходов и подключает его к своему входу или, ещё, это переключатель сигналов, управляемый двоичным кодом и имеющий один вход и несколько выходов. К входу подключается тот выход, чей номер соответствует состоянию двоичного кода. И частное определение: демультиплексор - это устройство, которое преобразует последовательный код в параллельный. Обычно в качестве демультиплексора используют дешифраторы двоичного кода в позиционный, в которых вводят дополнительный вход стробирования. Из-за сходства схем мультиплексора и демультиплексора в КМОП сериях есть микросхемы, которые одновременно являются мультиплексором и демультиплексором, смотря с какой стороны подавать сигналы. Например, К561КП1, работающая как переключатель 8х1 и переключатель 1х8 (то есть, как мультиплексор и демультиплексор с восемью входами или выходами). Кроме того, в КМОП микросхемах помимо переключения цифровых сигналов (логических 0 или 1) существует возможность переключения аналоговых. Шифратор— это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причем каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логическихсигналов соответствует определенному двоичному коду. Если количество входов настолько велико, что в шифраторе используются все возможные комбинации сигналов на выходе, то такой шифратор называется полным, если не все, то неполным. Число входов и выходов в полном шифраторе связано соотношением п = 2т, где п — число входов, т — число выходов. Дешифратором называется комбинационное устройство, преобразующее n-разрядный двоичный код в логический сигнал, появляющийся на том выходе, десятичный номер которого соответствует двоичному коду. Число входов и выходов в так называемом полном дешифраторе связано соотношением т = 2n, где п — число входов, а т — число выходов. Компаратор - это операционный усилитель, сравнивающий сигналы на прямом и инверсном входах. Используется обычно в схемах автоматизации каких-то процессов. Построить логическую схему функции F(A,B) и таблицу истинности.  Задание 2. По заданной логической схеме (рис.4.2) составить логическое выражение и выполнить для него таблицу истинности.  Задание 4. Логические элементы И—HE и ИЛИ—НЕ называют базовыми, поскольку любой из перечисленных на рис. 4.1 логических элементов можно выразить только через И—НЕ (или ИЛИ—НЕ). Соответствующие схемы для одного из этих случаев приведены на рис. 8.3.    |