Исследование дешифратора. Лабораторная работа 2 Исследование работы дешифратора

Скачать 4.08 Mb. Скачать 4.08 Mb.

|

|

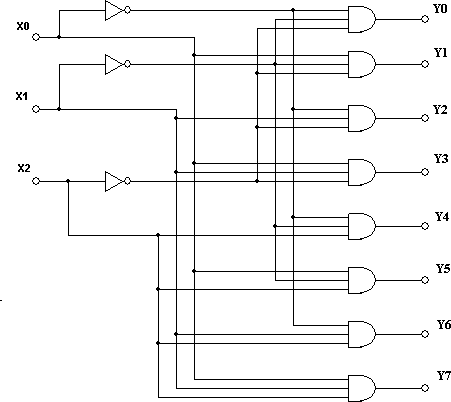

Лабораторная работа № 2 Исследование работы дешифратора Комбинационной схемой называется логическая схема, реализующая однозначное соответствие между значениями входных и выходных сигналов. Дешифратор – логическая комбинационная схема, которая имеет n информационных входов и 2nвыходов и преобразует один код в другой. Каждой комбинации логических уровней на входах будет соответствовать активный уровень на одном из 2nвыходов. Как любая логическая схема, дешифратор может быть задан таблицей истинности. В табл. 1 представлена таблица истинности дешифратора 3 Х 8. Эта таблица имеет три столбца, соответствующих входным сигналам: Х0, Х1, Х2, и восемь столбцов, соответствующих выходным сигналам: Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7. В первых слева трех столбцах расположены все возможные комбинации входных сигналов, а в последних восьми столбцах – соответствующие им комбинации выходных сигналов. Таблица 9

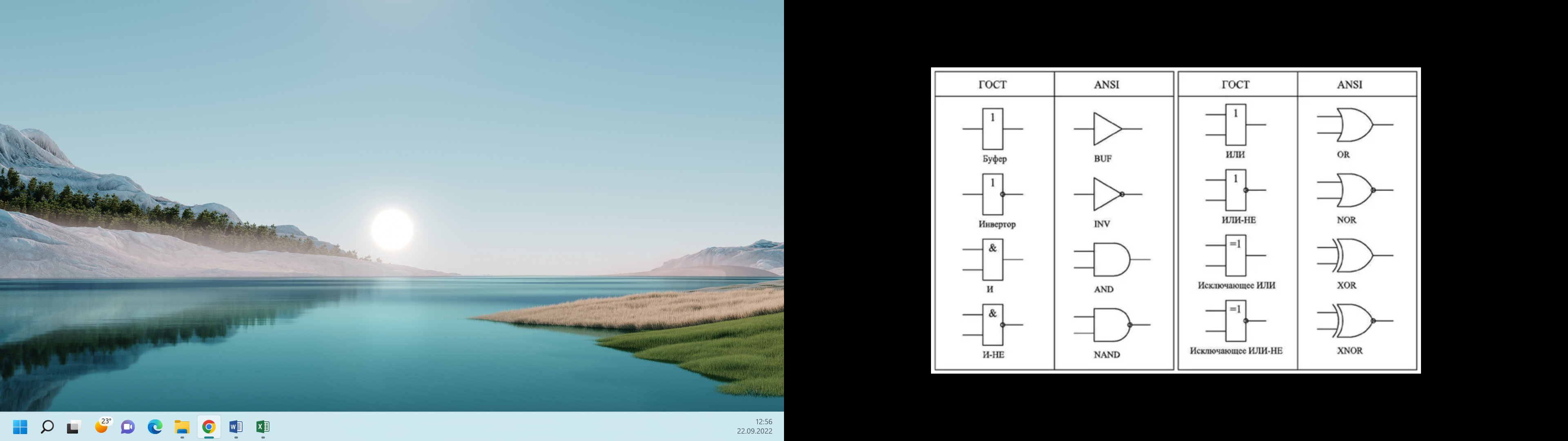

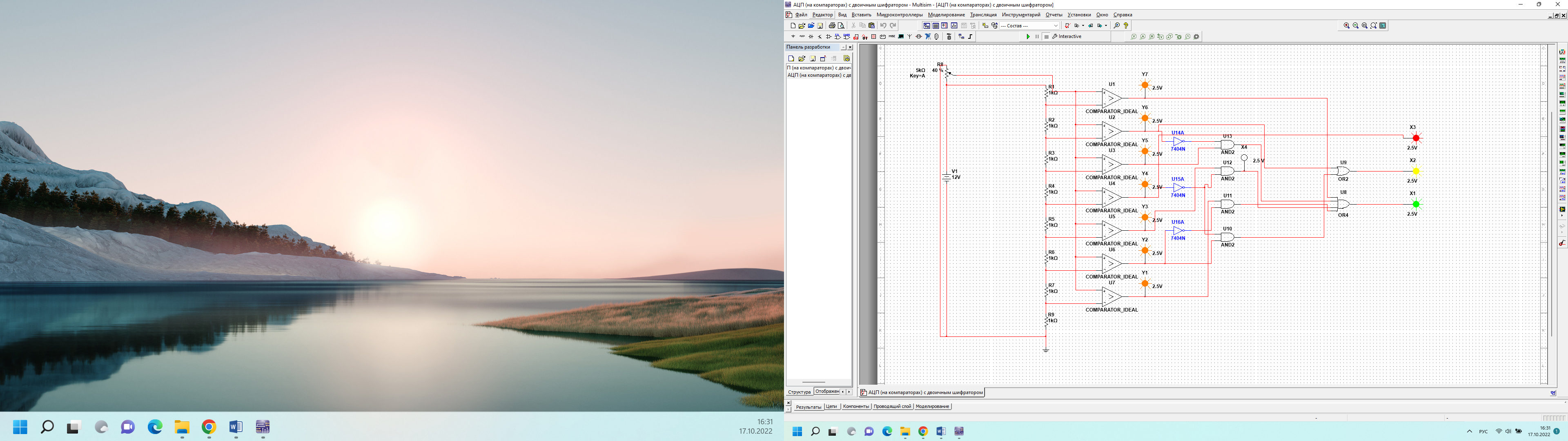

Из таблицы видно, что схема имеет восемь выходов, на одном из которых потенциал высокий, на остальных низкий. Номер единственного выхода, на котором формируется высокий потенциал, соответствует двоичному числу, формируемому состояниями входных сигналов. Этот принцип формирования выходного сигнала можно описать следующим образом: Yi= 0, если i равно k; Yi= 1, если iне равно k, здесь I– номер разряда, k = 22 X2 + 21X1 + 20X0. Выражения для каждого выхода дешифратора: Y0 =/X2 /X1 /X0, Y4 = X2 /X1 /X0, Y1 = /X2 /X1 X0, Y5 = X2 /X1 X0, Y2 = /X2 X1 /X0, Y6 = /X2 X1 X0, Y3 = X2 X1/X0, Y7 =X2 X1 X0, здесь / означает инвертирование. Таким образом, схема дешифратора должна содержать три схемы НЕ и восемь схем 3И (рис. 1).  Рис. 1. Схема дешифратора 3 Х 8  Рис.2. Графическое обозначение логических элементов согласно ГОСТ и международной системы ANSI Последовательность выполнение работы Составить таблицу истинности для дешифратора 3 Х 8. Используя программные средства Multisim 14 собрать схему дешифратора 3Х8. Для этого поместить на схему восемь логических схем 3И, восемь светодиодов (пробников), три логические схемы НЕ (инверторы). Для проверки работоспособности схемы собрать комбинацию из реализованных вами ранее схемы ЦАП резистивного вида (рисунок 3), АЦП параллельного преобразования (рисунок 4) и дешифратора. С помощью переключателей ЦАП подать на вход дешифратора все возможные комбинации сигналов и записать для каждого входного сигнала выходной сигнал (восьмиразрядную комбинацию), т.е. проверить таблицу истинности. Оценить работоспособность собранной схемы.

Содержание отчёта Текстовая часть отчета о выполнении лабораторной работе должна содержать: Описание дешифратора Составленную вами таблицу истинности для дешифратора 3 Х 8. Сконструированную вами схему дешифратора 3 Х 8 (рисунок). Скан экрана программы симулятора Multisim с реализованной вами схемой дешифратора. Скан экрана программы симулятора Multisim со сборкой ЦАП, АЦП и дешифратора. Выводы о соответствии или несоответствии таблице истинности значений на входах выходах дешифратора 3 Х 8 полученных экспериментальным путем. Вместе с текстовым отчетом прикрепить рабочий файл Multisim с реализованной вами схемой ЦАП, АЦП и дешифратора |