РГР. Микропрограммирование

Скачать 39.19 Kb. Скачать 39.19 Kb.

|

|

МИНОБРНАУКИ РОССИИ Федеральное государственное бюджетное образовательное учреждение высшего образования «Ухтинский государственный технический университет» (УГТУ) Кафедра вычислительной техники, информационных систем и технологий РАСЧЁТНО-ГРАФИЧЕСКАЯ РАБОТА Дисциплина: «Архитектура ЭВМ» Тема: «Микропрограммирование» Шифр 211395 Группа ИСТ-20з Курс 3 Вариант 5 Авилкин Дмитрий Ильич Проверил: доцент кафедры ВТИСиТ И. А. Базарова Ухта 2021 Содержание

Введение Компьютер представляет собой программируемое электронное устройство, способное обрабатывать данные и производить вычисления, а также выполнять другие задачи манипулирования символами. Существует два основных класса компьютеров: цифровые компьютеры, обрабатывающие данные в виде числовых двоичных кодов; аналоговые компьютеры, обрабатывающие непрерывно меняющиеся физические величины (электрическое напряжение, время и т.д.), которые являются аналогами вычисляемых величин. Под архитектурой компьютера понимается его логическая организация, структура и ресурсы, т.е. средства вычислительной системы, которые могут быть выделены процессу обработки данных на определенный интервал времени. Архитектура ПК определяет принцип действия, информационные связи и взаимное соединение основных логических узлов компьютера: центрального процессора; основной памяти; внешней памяти; периферийных устройств. Создание персонального компьютера можно отнести к одному из самых значительных изобретений 20 века. ПК существенно изменил роль и значение вычислительной техники в жизни человека. Современные ЭВМ бывают самыми разными: от больших, занимающих целый зал, до маленьких, помещающихся на столе, в портфеле и даже в кармане. Сегодня самым массовым видом ЭВМ являются персональные компьютеры. Но для нормальной работы необходимо чётко и ясно представлять, из чего компьютер состоит, т.е. знать его архитектуру. В этом и заключается цель данной РГР. Задание 1Архитектура МП предполагает следующие регистры процессора и для работы с памятью: MAR – регистр адреса памяти, PC – программный счетчик, IR – регистр команд, MBR – регистр данных памяти. Запишите фазу извлечения операндов при косвенной адресации. Решение Таблица 1 – Фаза извлечения операндов при косвенной адресации

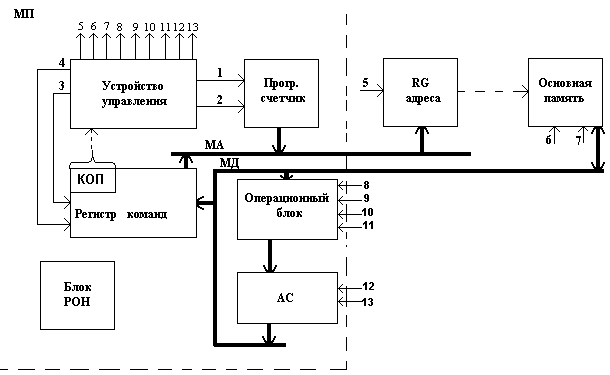

Рассмотрим представленные в таблице 1 микрооперации. На такте 1 значение поля адреса команды из регистра команд IR сначала считывается на магистраль адреса (МА), а затем записывается с МА в регистр адреса памяти MAR. На такте 2 содержимое ячейки памяти по адресу, который записан в MAR, сначала считывается в буферный регистр MBR, а затем записывается в него. В результате MBR содержит в себе фактический адрес операнда. На такте 3 содержимое регистра MBR сначала считывается на магистраль данных (МД), а затем записывается с МД в поле адреса регистра IR. В результате в нем оказывается код адреса операнда. Таким образом, на данном этапе в регистре команд IR будет такой же код, как в случае использования прямой, а не косвенной адресации. На такте 4 значение поля адреса команды из регистра команд IR сначала считывается на магистраль адреса, а затем записывается с МА в регистр адреса памяти MAR. На такте 5 содержимое ячейки памяти по адресу, который записан в MAR, сначала считывается в буферный регистр MBR, а затем записывается в него. Буферный регистр MBR содержит в себе уже сам операнд. Задание 2Немаскируемые прерывания. Решение Аппаратные прерывания обеспечивают ответные шаги микропроцессора на события, которые происходят по отношению к исполняемому на данный момент программному коду асинхронно. Можно выделить четыре типа (источника) прерываний: внутренние прерывания процессора и сопроцессора (исключения); немаскируемые внешние прерывания; маскируемые внешние прерывания; программно вызываемые прерывания. Условие возможного возникновения аппаратных прерываний проверяется микропроцессором на границе инструкций. Немаскируемые прерывания обладают наивысшим приоритетом, и обрабатываются процессором независимо от состояния флага разрешения прерывания IF. Источники немаскируемых прерываний: 1. Сигнал по линии NMI - приходит от схем контроля паритета памяти, от линии SERR# (System Error, системная ошибка) шины PCI, от линии IOCHK (контроль канала) шины ISA. Если во время обработки немаскируемого прерывания снова возникнет сигнал NMI, то вложенного прерывания не будет повторный вызов обработчика NMI возможен только после выполнения инструкции IRET. 2. Прерывание по линии SMI# - прерывание SMI возникает от схем чипсета, участвующих в управлении энергопотреблением. Это прерывание обладает наивысшим приоритетом и обслуживается не так, как все остальные прерывания в системе. Задание 3Условия. Архитектура МП предполагает наличие программного счетчика (PC), регистра команд (IR), регистра-аккумулятора (AC), операционного блока (ОБ), устройства управления; а также регистр адреса памяти (MAR) для работы с основной памятью. Записать последовательность микрокоманд МП при выполнении следующей инструкции: А+1+В+1. Адресация – прямая. А=10112.Адрес числа B7F5h. В=10112. Адрес числа B7F7h. Состояние программного счетчика на момент выполнения программы 41310. Сохранить результат по адресу B7F7h. Решение. Для наглядности приведем укрупненную структурную схему процессора с обращением к основной памяти ( Рисунок 1).  Рисунок 1 – Укрупненная структурная схема процессорной системы Предположим, что управляющие сигналы устройства управления соответствуют таблице 1. Таблица 1. Управляющие сигналы устройства управления

Запишем последовательность микрокоманд МП при выполнении следующей инструкции (адресация – прямая): А+1+В+1 (таблица 2). Таблица 2 – Этапы выполнения инструкции А+1+В+1

ЗаключениеВ ходе выполнения данной работы были изучены принципы функционирования МП, закреплены теоретические основы по дисциплине Архитектура ЭВМТаким образом, цель работы, заключающаяся в рассмотрении и анализе состава и назначения основных блоков компьютера достигнута, задачи выполненыСписок литературыБазарова, И. А. Архитектура ЭВМ [Текст]: методические указания к выполнению расчетно-графической работы для студентов заочной формы обучения для направления 09.03.02 ИСТ квалификации бакалавр / И. А. Базарова. – Ухта: УГТУ, 2022 - 17с. Материалы лекционного курса Базаровой И.А. по дисциплине «Архитектура ЭВМ» для подготовки к сдаче зачёта основы структурной организации компьютерных систем. Основные понятия и определения. Классификация микропроцессорных систем. / И. А. Базарова. – Ухта: УГТУ – 45с. |