Электроника ЛР. ЛР по электронике №90. Не является запрещенной, а приводит к переходу триггера в инверсное состояние

Скачать 270.91 Kb. Скачать 270.91 Kb.

|

|

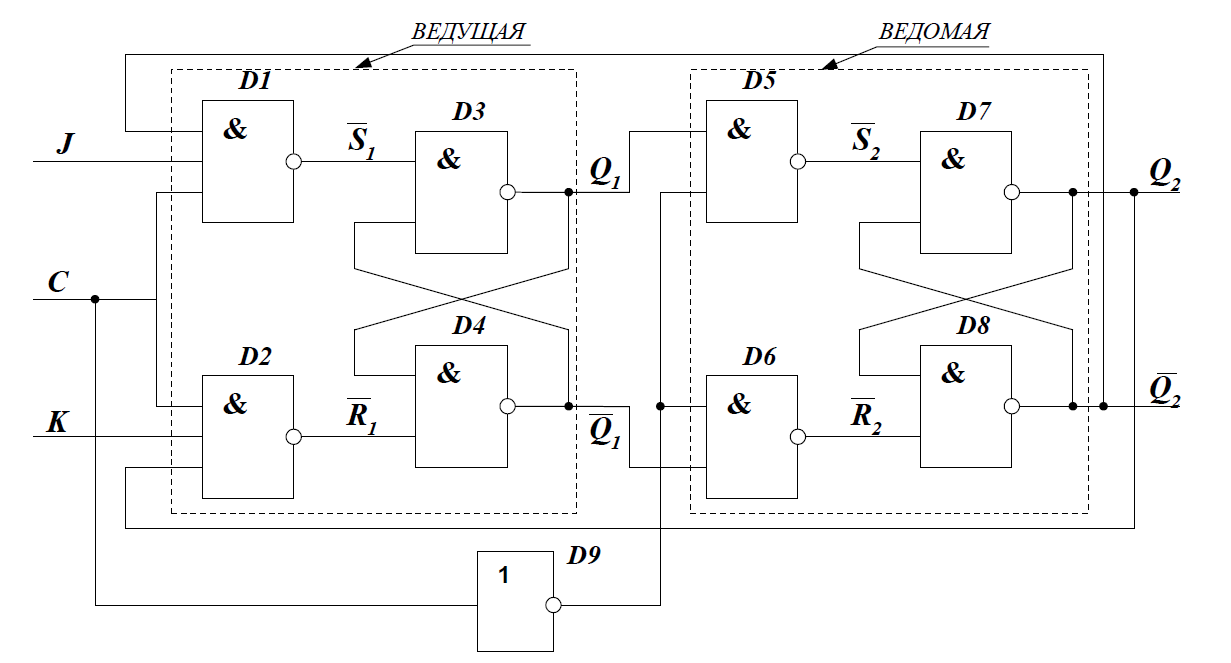

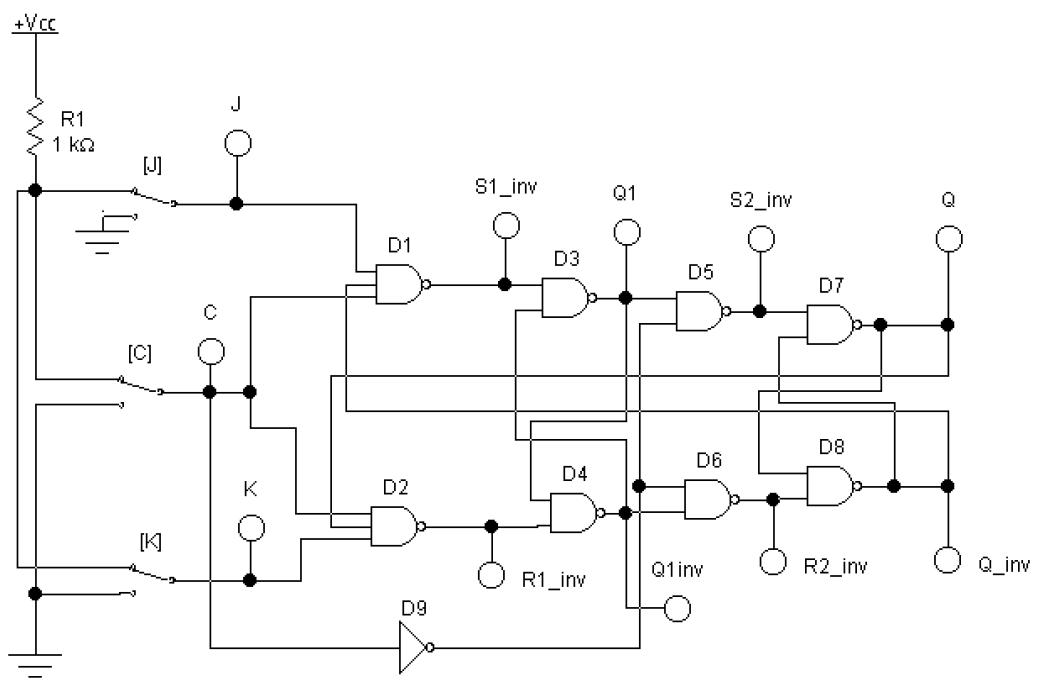

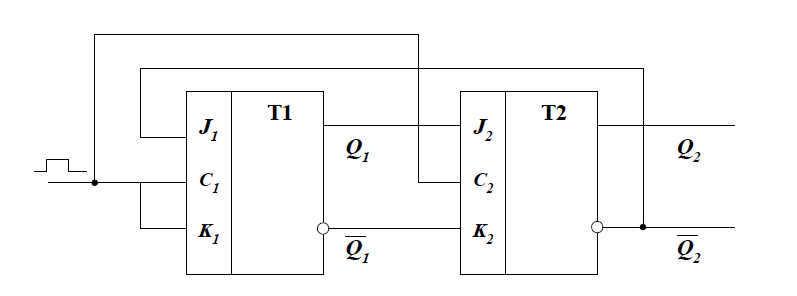

Цель работы: изучение принципа действия JK-триггера, а также схем делителей частоты следования импульсов, реализованных на базе JK-триггеров. JK-триггер является универсальным типом триггера, способным работать в режимах RS-, T- и D-триггера. JK-триггер имеет два информационных входа и вход подачи тактовых импульсов. Вход J («jump» - скачок) устанавливает триггер в состояние логической единицы, а вход K(«keep» - сохранять) - сбрасывает триггер в 0. При комбинациях J=K=0; J=1, K=0 и J=0, K=1 триггер работает как RST-триггер, причем вход J эквивалентен входу S, а вход K – входу R. Но в отличие от RS-триггера комбинация J=K=1 не является запрещенной, а приводит к переходу триггера в инверсное состояние. Структурно JK-триггер состоит из двух последовательно соединенных RST-триггеров, связанных обратной связью: так называемой, ведущей части (D1, D2, D3, D4), ведомой части (D5, D6, D7, D8) и инвертора (D9). При поступлении на вход триггера тактового импульса (перепад 0/1) срабатывает и изменяет свое состояние согласно входной комбинации J и K ведущая часть, в то время как на ведомой части тактовый импульс отсутствует, следовательно, на выходе ведомой части состояние не изменяется. По окончании тактового импульса (перепад 1/0) состояние ведущей части переписывается в ведомую. Таким образом, входная комбинация JK-триггера, определяющая состояние на выходе триггера, фиксируется по переднему фронту тактового импульса (перепад 0/1), а изменение выходного состояние происходит по заднему фронту тактового импульса. Необходимость такой работы триггера вызвана тем, что входное состояние триггера определяется не только значениями J и K, но и предыдущим состоянием триггера  Рис.1 Схема JK триггера  Рис. 2 Исследуемая схема JK триггера Необходимо установить на выходе Q триггера состояние, указанное в столбце Состояния на входах и выходах определяются по состоянию соответствующих светодиодов: “красный” соответствует уровню логической единицы. Далее с помощью ключей J, K и C, подключаемых либо к источнику питания (уровень логической единицы), либо к шине «земля» (уровень логического нуля), подать на входы триггера состояние, указанное для них в заполняемой строке таблицы 1 («Устанавливаемые значения»). Для тактовых импульсов перепад 1/0 соответствует переходу в состояние логического нуля, а перепад 0/1 – в состояние логической единицы. Записать выходное состояние триггера после установки входной комбинации в графы «Наблюдаемые значения»: S1, R1, Q1, S2, R2, Q2. При исследовании делителей частоты следования импульсов после загрузки соответствующих файлов необходимо запустить процесс моделирования и зарисовать осциллограммы на всех выходах исследуемой схемы.

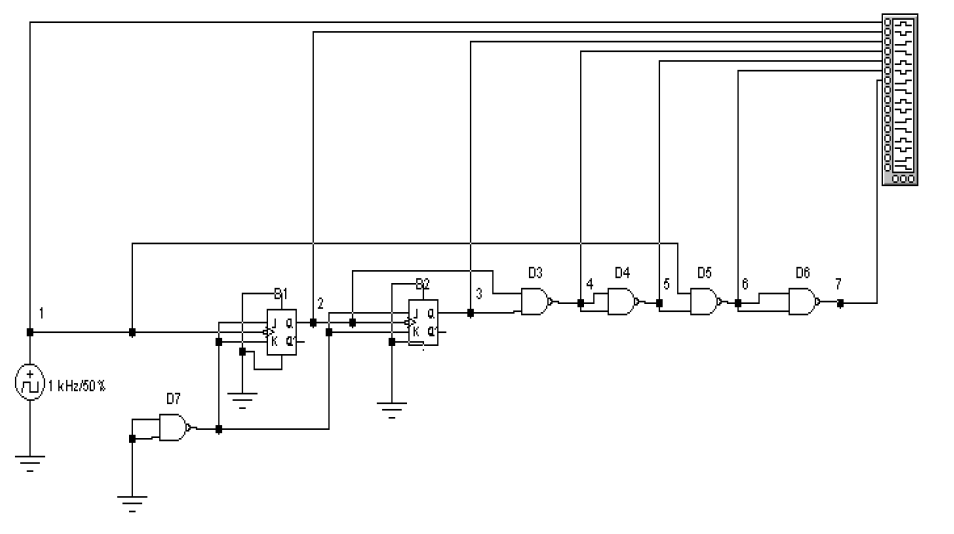

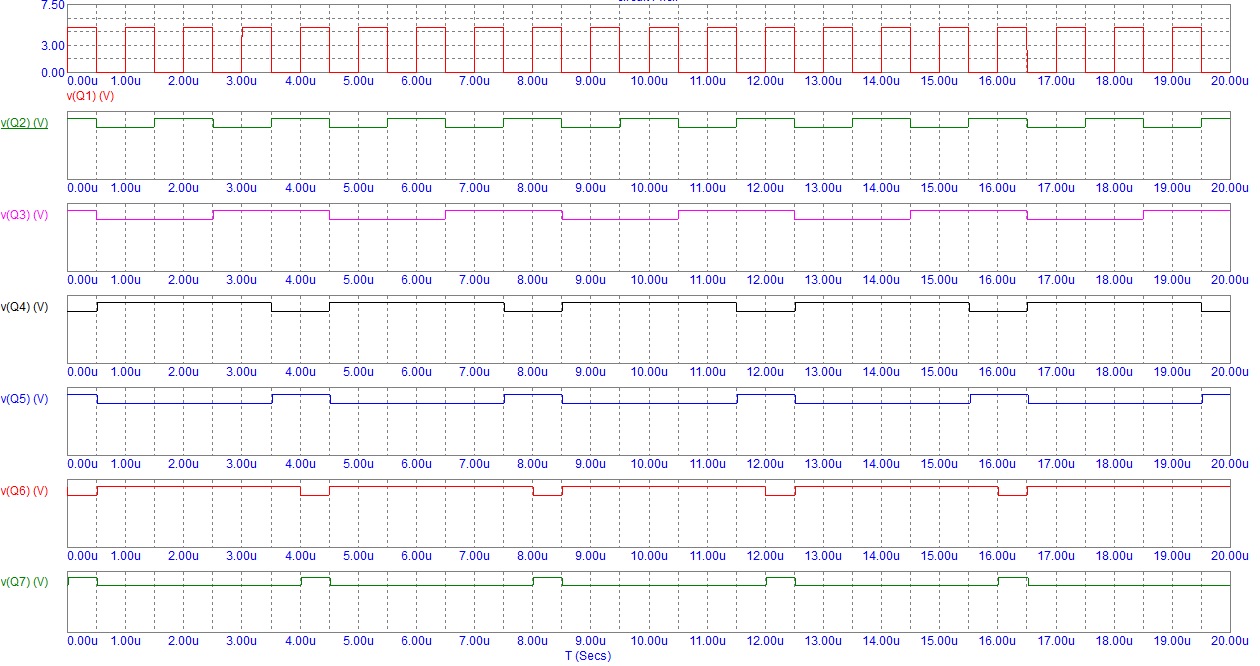

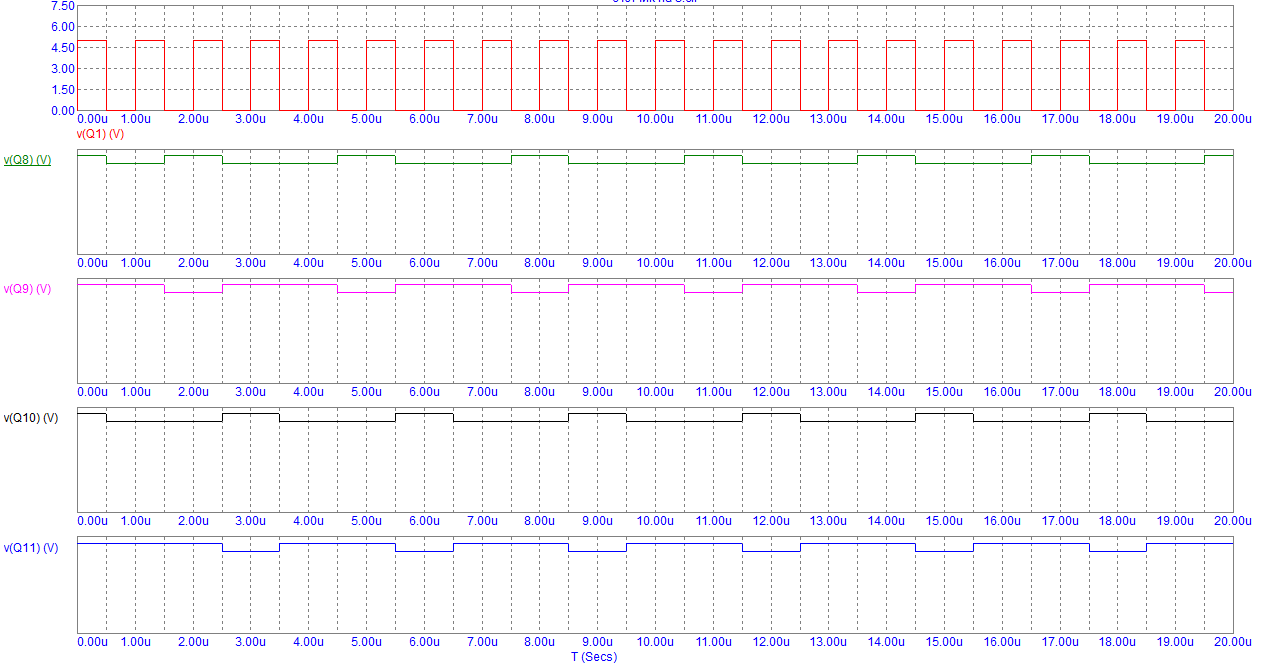

Таблица 1. Состояния JK-триггера В результате исследования на практике узнали работу JK триггера и составили таблицу истинности с помощью средств моделирования. Схема делителя частоты следования импульсов на 4 на базе JK-триггеров состоит из: «1» - входные тактовые импульсы; «2» - выход первого JK-триггера (делитель на 2); «3» - выход второго JK-триггера (делитель на 4); «4» «5» «6» «7» - выходы логических элементов D3¸D6, позволяющих изменять длительность выходных импульсов.  Рис. 3 Исследуемая схема делителя импульсов на 4 на базе JK-триггеров  Рис. 4 Осциллограммы контрольных точек схемы Видно деление частоты в толчках 2 и 3. В точке 2 деление на 2, в точке 3 деление частоты на 4.  Рис. 5 Исследуемая схема делителя импульсов на 3 на базе JK-триггеров  Рис. 6. Осциллограммы контрольных точек схемы Вывод: JK-триггеры подразделяются на универсальные и комбинированные. Универсальный JK-триггер имеет два информационных входа J и K. По входу J триггер устанавливается в состояние Q=1, /Q=0, а по входу K-в состояние Q=0, /Q=1. JK-триггер отличается от RS-триггера прежде всего тем что в нем устранена неопределенность, которая возникает в RS-триггере при определенной комбинации входных сигналов. Универсальность JK-триггера состоит в том, что он может выполнять функции RS-, Т- и D-триггеров. Комбинированный JK-триггер отличается от универсального наличия дополнительных асинхронных входов S и R для предварительной установки триггера в определенное состояние (логической 1 или 0). Простейший JK-триггер можно получить из синхронного RS-триггера с динамическим управлением, если ввести дополнительные обратные связи с выходов триггера на входы, которые позволяют устранить неопределенность в таблице состоянии Устройство двоичного суммирующего счетчика, выполненного на базе JK-триггеров Синхронизирующие входы всех триггеров, кроме крайнего левого (Т1), соединены с выходами предыдущих триггеров. Поэтому состояние триггера меняется в ответ на изменение состояния предыдущего триггера. Так получаем делитель частоты на 2,4 и так далее. В исследуемом делителе на 3, необходимо сбросить счет при достижении определенного счета, а конкретно 10, при достижении этого значения сбрасывается счет и снова начинается сначала. В схеме это реализовано подаче с инверсного выхода второго триггера на вход J первого триггера. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||