Лб4. Лабораторная 4. Отчет по лабораторной работе 4 по теме Активные элементы радиоэлектронных устройств

Скачать 427.73 Kb. Скачать 427.73 Kb.

|

|

МИНИСТЕРСТВО ЦИФРОВОГО РАЗВИТИЯ, СВЯЗИ И МАССОВЫХ КОММУНИКАЦИЙ РОССИЙСКОЙ ФЕРЕРАЦИИ ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ «САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ТЕЛЕКОММУНИКАЦИЙ ИМ. ПРОФ. М.А. БОНЧ-БРУЕВИЧА» (СПбГУТ) Кафедра конструирования и производства радиоэлектронных средств Отчет по лабораторной работе 4 по теме «Активные элементы радиоэлектронных устройств» Выполнила студентка группы РТ-01 Чихунова А.С. Принял: ассистент каф. КПРЭС Горобцов И.А. Санкт-Петербург 2021

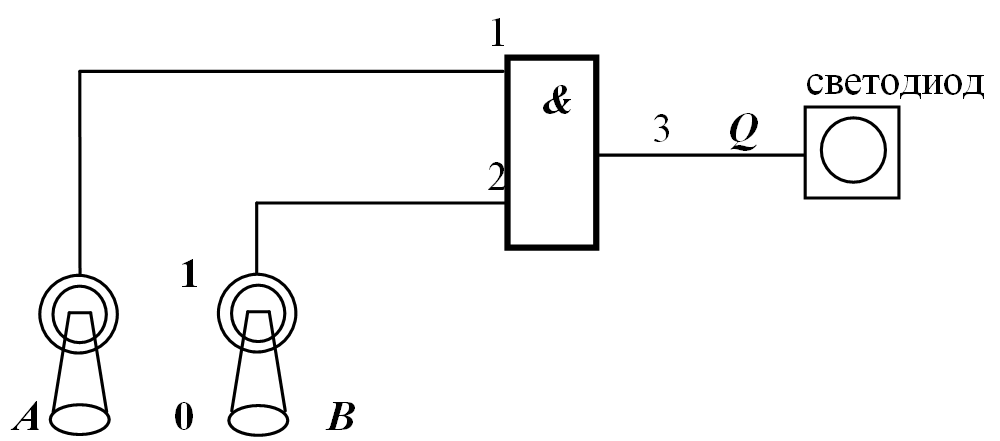

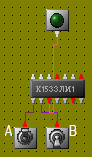

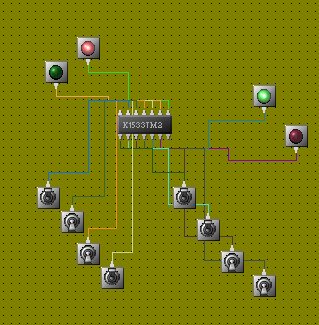

1. Ознакомление с работой программы ICBuilder. 1.1Внимательно изучить раздел ПРИЛОЖЕНИЕ и проделать все действия, предусмотренные в данном разделе. 1). Осуществить вызов в рабочее поле самых различных объектов (микросхем, переключателей, кнопок, подписей, логических нулей и единиц). 2). Случайным образом соединить несколько микросхем и убедиться, что виртуальный проводник может вестись лишь от выхода ко входу. Произвести соединение выключателя и кнопки с различными светодиодами. Убедиться в возможности индикации (подсветки красным цветом) выходов микросхем. 3). Произвести перемещение и удаление вызванных объектов и надписей. 1.2. Вызвав одну из микросхем на экран и, удобно расположив её (например, микросхему 1533ЛИ1 – 2И), «собрать» на экране схему включения логического элемента (рис. 1.1):   Рис.1.1. Схема включения логического элемента И (пример). 1.3. Продемонстрировать преподавателю работу данной схемы. 1.4. Составить таблицу истинности рассмотренного логического вентиля (табл. 1.1): Таблица 1.1.

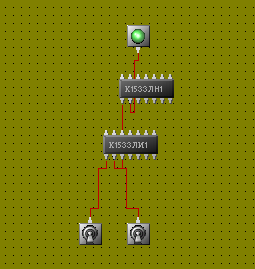

1.5. Собрать схему включения и занести скриншот в отчёт. 2. Исследование логического вентиля 2.1Добавив к вентилю микросхемы 1533ЛИ1 логический инвертор (микросхема 1533ЛН1), построить схему инвертирующего логического вентиля (рис. 1.2):  A 1 3 1 2 Q B 2 Рис.1.2. 2.2. Продемонстрировать преподавателю работу данной схемы.  2.3. Составить аналогичную п. 1.1. таблицу истинности 1.2 и занести схему и таблицу в отчёт.

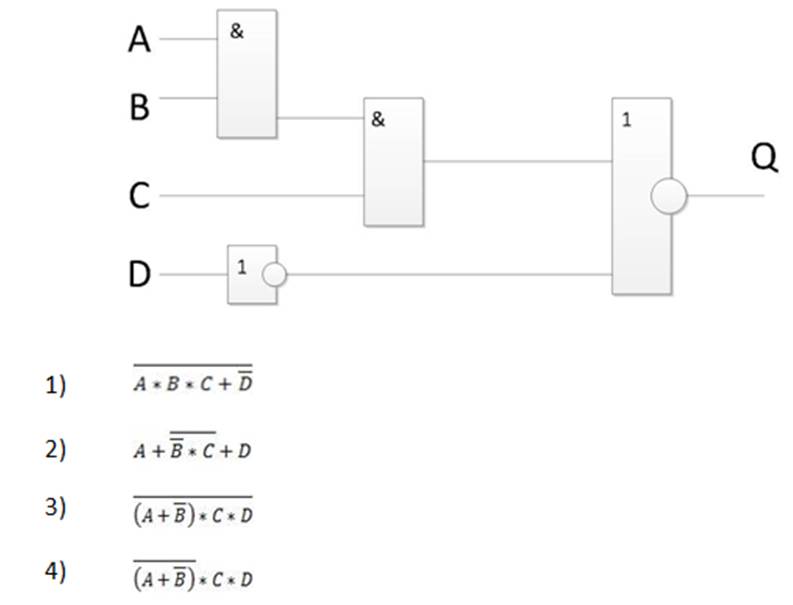

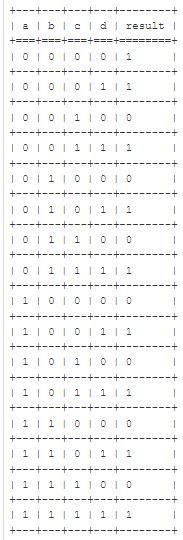

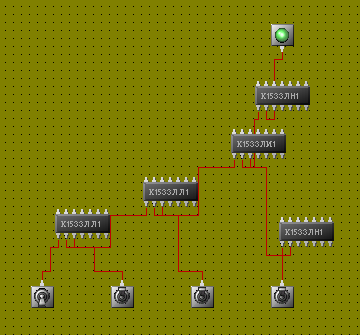

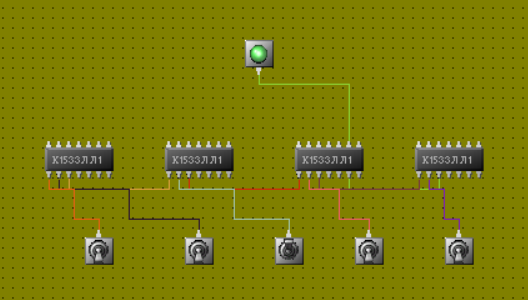

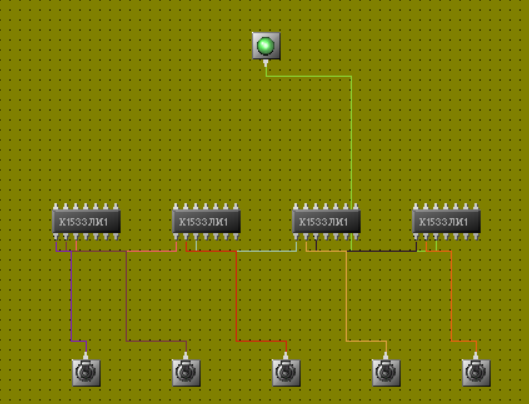

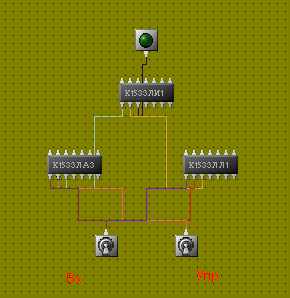

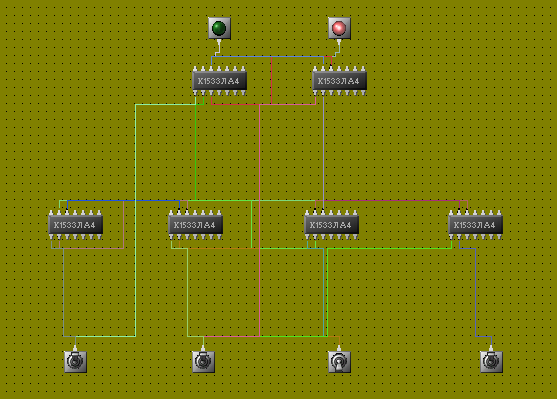

ВЫВОД: Вентиль И-НЕ работает, выполняет логическую функцию правильно. 3. Построение заданных булевых функций 3.1 Используя заданные микросхемы: 1533ЛИ1 (2И), 1533ЛЛ1 (2ИЛИ), 1533ЛН1 (НЕ), 1533ЛА3 (2И-НЕ), составить схемы, реализующие логические функции и занести её в отчёт (смотри раздаточный материал). 3.2 Построить в отчёте логическую схему, соответствующую своему варианту и показать её преподавателю. 1)  2)  3.2 Построить и занести в отчет логическую схему, соответствующую своему варианту.  3.3. Построение многовходовых элементов И и ИЛИ   Не     И     Или     Или  Не     A B C D На базе микросхем 1533ЛИ1 (4*2И) и 1533ЛЛ1 (4*2ИЛИ) построить вентили 5И и 5ИЛИ, «собрать» и продемонстрировать их работу. Составленные схемы и скриншоты собранных вентилей занести в отчет.   ВЫВОД: Из готовых микросхем 2И и 2ИЛИ можно собрать громоздкие аналоги вентилей 5И и 5ИЛИ, но это бесполезно 4. Построение управляемого инвертора (Используется в компьютерах при выполнении операций вычитания и деления). В зависимости от значения управляющего сигнала «Упр.» (0 или 1) входной сигнал «Вх.» либо поступает на выход без изменения, либо в инвертированном виде (рис. 1.3):  Вх. Вых. Упр. Рис.1.3. Схемы работы одноразрядного управляемого инвертора. 4.1. Используя три логических вентиля: И-НЕ, ИЛИ, И спроектировать и собрать указанную схему и занести в отчет (скриншот).       И-НЕ Вх       ВЫХ И    ИЛИ УПР    5.3. Составить таблицу истинности управляемого инвертора (табл. 1.3.) и вместе со схемой занести в отчёт. Таблица 1.3.

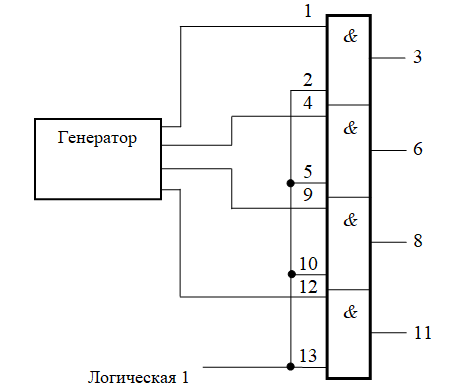

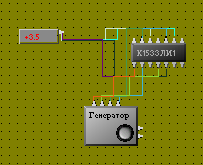

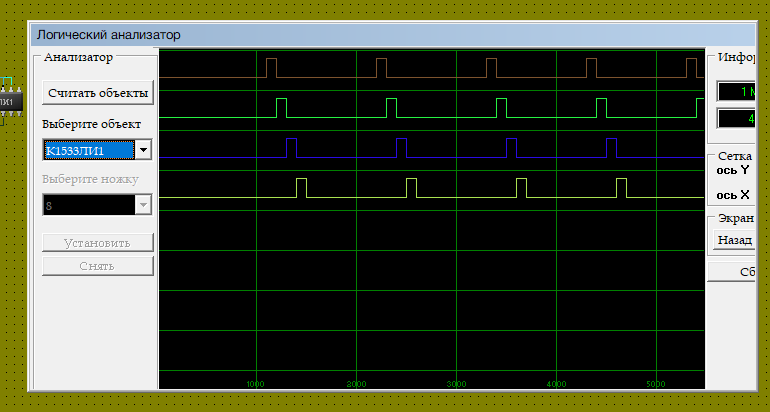

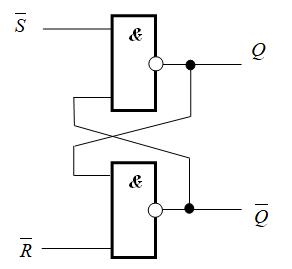

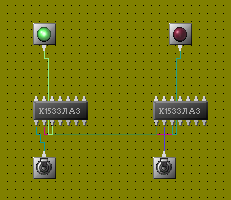

ВЫВОД: Управляемый инвертор можно собрать из уже известных нам несложных вентилей. 5. Проверка функционирования логических элементов 2И в условиях динамически меняющихся входных воздействий 6.1. Вызвать на рабочее поле экрана генератор и логический анализатор (логический анализатор вызывается только после вызова генератора). 6.2. Вызвать микросхему 1533ЛИ1 (4 вентиля 2И). 6.3. Подсоединить выходные сигналы генератора, сдвинутые по фазе относительно друг друга, ко входам 1533ЛИ1, как показано на рис. 1.4:  Рис. 1.4. Коммутация выходных сигналов генератора, сдвинутых по фазе относительно друг друга, к входам 1533ЛИ1. 6.4. Подсоединить логический анализатор к выходам 1533ЛИ1, для чего: 1). Считать вызванные объекты (микросхему 1533ЛИ1) посредством нажатия кнопки «Считать объекты». 2). В подокне «Выберите объект» выбрать микросхему, к выходам которой подключается логический анализатор. 3). В подокне «Выберите ножку» последовательно выбрать те ножки микросхем, к которым будут подключаться соответствующие каналы логического анализатора. После каждого выбора ножки нажимать активизирующуюся кнопку «Установить». После каждого выбора и установки ножки вновь выбирать микросхему в подокне «Выберите объект». Факт подсоединения логического анализатора к ножкам микросхемы не отображается графически на экране монитора. В программе не предусмотрена возможность подключения логического анализатора непосредственно к генератору входных сигналов. 6.5. Задать частоту генерирования. 1).Навести курсор на корпус генератора и нажать правую кнопку мыши. 2). В открывшемся меню выбрать позицию «Частота». 3). В открывшемся подменю выбрать соответствующее значение. 6.6. Задать режим непрерывной генерации, для чего: 1).Навести курсор на корпус генератора и нажать правую кнопку мыши. 2). В открывшемся меню выбрать позицию «Такты». 3). В открывшемся подменю выбрать позицию «Непрерывно». 6.7. Запустить генератор, нажав кнопку на его корпусе. 6.8. По сигналам на экране логического анализатора убедиться в работоспособности генератора и логического элемента. Обратить внимание на то, что с четырёх выходов генератора снимается четырёхфазный сигнал и временная задержка между фазами равна длительности генерируемых импульсов. 6.9. Занести в отчёт полученные временные диаграммы с пояснением их формы. 6.10. Задать конечное число генерируемых импульсов (например, 7) и получить аналогичные временные диаграммы. Схема соединения логического анализатора к выходам 1533ЛИ и полученные временные диаграммы   ВЫВОД: Вентили 2И стабильно работают при динамически изменяющемся воздействии, и исправно умножают сигнал на логическую единицу. 6. Изучение работы триггеров 6.1. Синтез RS-триггера на базе логических вентилей И – НЕ 6.1. Используя логические вентили И-НЕ, построить схему, представленную на рис. 1.5.   Рис. 1.5. Схема RS-триггера. Скриншот схемы. Заполнить таблицу 1.4.

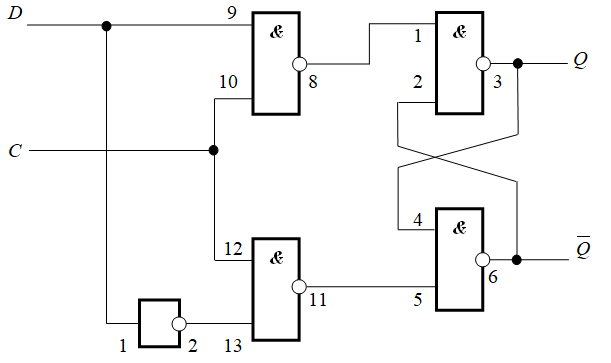

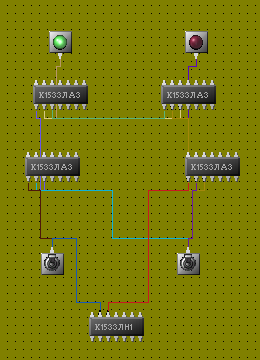

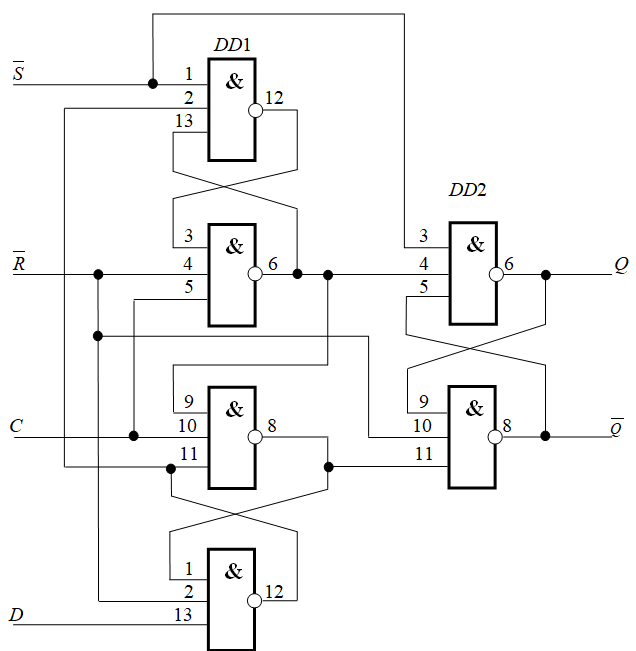

6.2. Построение D-триггера на базе логических элементов 6.2.1. Используя логические вентили, собрать схему синхронного D-триггера, представленную на рис. 1.6. Составить таблицу истинности D-триггера, представленного на рис. 1.6.   Рис. 1.6. Схема синхронного D-триггера. Скриншот схемы. Заполнить таблицу 1.5.

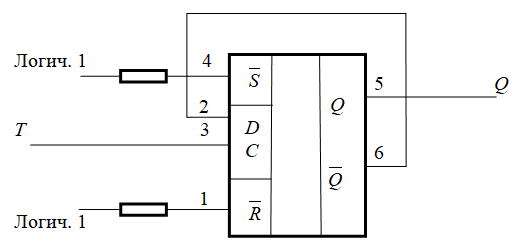

Проверить правильность составленной таблицы истинности. При проверке использовать все последовательные комбинации входных сигналов. 6.3. Построение D-триггера на базе логических элементов с учётом сигналов принудительной установки и сброса 6.3.1. Ввести дополнительные сигналы принудительной установки (S) и принудительного сброса (R) D-триггера. С учётом введённых сигналов построить схему (рис. 1.7):   Скриншот схемы. Скриншот схемы. Рис. 1.7. Схема D-триггера с сигналами принудительной установки и сброса. 6.3.2. На основании собранной схемы составить таблицу истинности (табл. 1.6.) и убедиться в работоспособности устройства. Пояснить полученные результаты. Таблица 1.6.

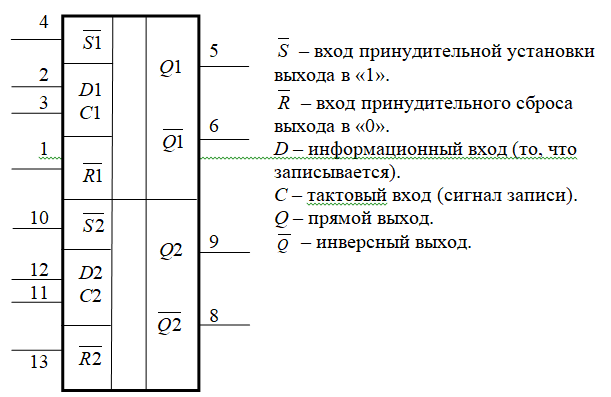

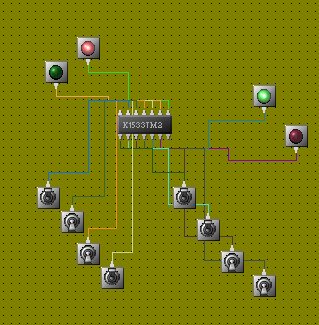

6.4. Изучение схемы включения сдвоенного D-триггера на базе микросхемы 1533ТМ2 6.4.1. Собрать схему включения данной микросхемы (рис. 1.8) и убедиться, что принцип её работы полностью соответствует составленной в п. 3.4.3 таблице истинности. Поместить в отчет схему сборки сдвоенного D-триггера (поле для рис. 1.9.)  Рис. 1.8. УГО микросхемы 1533ТМ2 и сборка сдвоенного D-триггера.  Рис. 1.9. Сборка сдвоенного D-триггера (скриншот). 6.5. Изучение работы Т-триггера, построенного на базе D-триггера  3.5.1. Изменить схему включения синхронного D-триггера для построения Т-триггера, как показано на рис. 1.10. Схему включения Т-триггера и таблицу истинности показать преподавателю и занести в отчёт. 3.5.1. Изменить схему включения синхронного D-триггера для построения Т-триггера, как показано на рис. 1.10. Схему включения Т-триггера и таблицу истинности показать преподавателю и занести в отчёт. Скриншот схемы. Скриншот схемы.Рис. 1.10. Схема построения Т-триггера на базе синхронного D-триггера. 6.5.2. Составить таблицу истинности работы Т-триггера (табл. 1.7): Таблица 1.7.

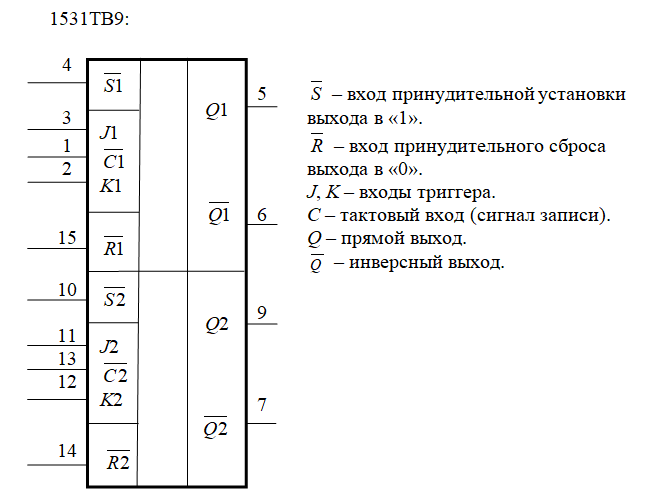

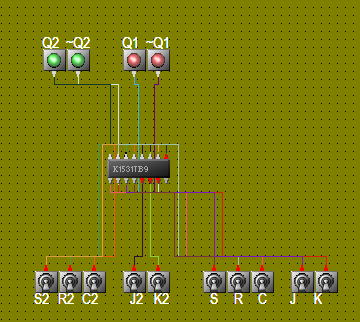

6.6. Изучение работы JK-триггера на базе микросхемы 1531ТВ9 В лабораторной работе рассматривается тактируемый JK-триггер на базе микросхемы 1531ТВ9 (рис. 1.11).  Рис. 1.11. УГО микросхемы 1531ТВ9. 6.6.1. Для открытия готовой схемы в окне программы IC Builder v1.51 выбрать: Файл → Открыть проект → Триггеры → Триггер - К1531ТВ9 (JK).icb. 6.6.2. На основании собранной схемы составить таблицу истинности (табл. 1.8.) и убедиться в работоспособности устройства. Пояснить полученные результаты. Таблица 1.8.

6.6.3. Схему триггера (скриншот), а также таблицу истинности занести в отчёт.  | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||