Министерство образования и науки РФ

Федеральное государственное бюджетное

образовательное учреждение высшего образования

«Омский государственный технический университет»

Факультет (институт) Радиотехнический

Кафедра Радиотехнические устройства и системы диагностики

КУРСОВОЙ ПРОЕКТ (РАБОТА)

по дисциплине Цифровые устройства и микропроцессоры

на тему Проектирование генератора сигналов произвольной формы табличным способом

Пояснительная записка

Шифр проекта (работы) 2068999 – 32 – 07 – 00.00.000.ПЗ

Студента Дерманты Эдуард Александрович

Курс 3 Группа ИСС-171

Направление (специальность) 110504

Инфокоммуникационные технологии и

системы специальной связи

Руководитель Семёнов К.В.

Выполнил

К защите

Проект (работа) защищен(а) с оценкой

Омск, 2020

КУРСОВОЙ ПРОЕКТ

Курсовой проект содержит 30 страницу, 10 рисунков.

Ключевые слова: Генератор, аналоговые сигналы, цифровые сигналы, ПЛИС, Quartus, Программируемая логическая интегральная схема, проектирование, Verilog.

В данном курсовом проекте произведено разработка и проектирование устройства генерации сигнала табличным методом на ПЛИС при помощи программной среды Quartus на языке описания аппаратуры Verilog.

COURSE PROJECT

The course project contains 30 pages, 10 figures.

Key words: Generator, analog signals, digital signals, FPGA, Quartus, Programmable logic integrated circuit, design, Verilog.

In this course project, the development and design of a signal generation device by a tabular method on an FPGA using the Quartus software environment in the Verilog hardware description language was carried out.

Оглавление

Введение 5

1.Способы генерации сигналов 6

2.Генераторы аналоговых и смешанных сигналов 8

2.1Генераторы сигналов произвольной формы 8

2.2Генераторы сигналов произвольной формы и стандартных функций (AFG) 9

12

2.3 Генераторы сигналов произвольной формы (AWG) 14

3.Описание ПЛИС и программной среды Quartus 16

3.1История развития ПЛИС 16

3.2Проектирование на ПЛИС 19

4.Разработка генератора сигналов произвольной формы табличным методом в программной среде Quartus 25

Заключение 28

Список используемой литературы 29

Введение

Генератор сигналов функционирует в полном соответствии со своим названием: генерирует сигналы, используемые в качестве воздействующих сигналов в ходе измерений параметров электронных устройств. Большинству схем требуется входной сигнал с изменяющейся во времени амплитудой. Такой сигнал может быть истинным биполярным сигналом переменного тока1 (пиковые значения которого попеременно поднимаются выше или опускаются ниже нулевого уровня), или он может колебаться относительно некоторого уровня постоянного напряжения (положительного или отрицательного).

Форма сигнала может представлять собой синусоиду или другую периодическую функцию, цифровой импульс, двоичную последовательность или полностью произвольную форму. Генератор сигналов может создавать «идеальные» сигналы или добавлять к сигналу известные искажения (или ошибки) нужной величины и типа. Эта возможность является одним из главных достоинств генератора сигналов, поскольку часто невозможно создать предсказуемые искажения в нужном месте и в нужное время с помощью самой исследуемой схемы. Реакция исследуемого устройства на эти искажения демонстрирует его способность работать в неблагоприятных условиях, выходящих за пределы нормального режима.

Способы генерации сигналов

Существуют аналоговые способы генерации и цифровые.

Для аналоговых способов генерации сигналов используют автоколебательные системы или автогенератор, принцип которого состоит в том, чтобы энергию от источника питания через управляющий элемент подавать в колебательную систему.

Основные методы цифровой генерации сигналов – метод аппроксимации и табличный метод.

Метод аппроксимации использует представление периодического сигнала в аналитическом виде и выполняет в микропроцессоре вычислений по заданной программе. В памяти устройства хранятся лишь параметры генерируемого сигнала. Программа вычисляет отсчеты функции с некоторым заданным интервалом. При необходимости получения аналогового сигнала далее используется ЦАП. Либо цифровые данные используются внутри устройства, например, в другой программе, или для модуляции. Метод аппроксимации позволяет обходится небольшим объемом памяти. Однако недостатком является необходимость вычисления значительного числа арифметических и логических операций, затрачиваемые на формирование одного отсчета сигнала, что ограничивает максимальную частоту сигнала.

Табличный метод генерации предполагает, что предварительно вычисленные цифровые отсчеты функции постоянно хранятся в памяти. Формирование очередного отсчета сводится к операциям подготовки адреса и чтения соответствующей ячейки памяти. Достоинством этого метода является меньшее время, затрачиваемое на формирование отсчета и, как следствие, возможность генерации сигналов с более высокой частотой. Недостатком является необходимость иметь большой объем памяти данных.

К табличному методу относится метод прямого цифрового синтеза. Прямой цифровой синтез (от англ. DDS – Direct Digital Synthesizer) – метод, позволяющий получить аналоговый сигнал (обычно это синусоидальный сигнал, пилообразный, последовательность треугольных импульсов) за счет генерации временной последовательности цифровых отсчетов и их дальнейшего преобразования в аналоговую форму посредством ЦАП. Так как сигнал сначала синтезируется в цифровой форме, такое устройство может обеспечить быстрое переключение частоты, высокое разрешение по сетке частот, работу в широком диапазоне частот.

Генераторы аналоговых и смешанных сигналов Генераторы сигналов произвольной формы

Исторически сложилось так, что задачу создания разных сигналов выполняют отдельные специализированные генераторы сигналов – от генераторов сверхчистых аудиосигналов до многогигагерцовых генераторов радиочастотных сигналов. И хотя существует множество серийно выпускаемых приборов, зачастую пользователю для решения стоящих перед ним задач приходится дорабатывать существующий генератор или самому изготавливать специализированный генератор.

Проектирование измерительного генератора – очень сложная задача и, конечно, время, потраченное на разработку дополнительного оборудования, вычитается из самого проекта. К счастью, технология дискретизации и обработки сигнала дала нам решение, позволяющее решить практически любую задачу с помощью одного единственного прибора – генератора сигналов произвольной формы. Генераторы сигналов произвольной формы можно разделить на генераторы сигналов произвольной формы и стандартных функций (AFG) и генераторы сигналов произвольной формы (AWG).

Генераторы сигналов произвольной формы и стандартных функций (AFG)

Генератор AFG предназначен для решения широкого спектра задач и на сегодняшний день генераторы этого типа являются наиболее распространенными. Обычно такой прибор предлагает меньше возможностей по изменению сигнала, чем аналогичный AWG, но обладает превосходной стабильностью и быстрым откликом на изменение частоты. Если исследуемому устройству необходима синусоида и меандр (не говоря уже о прочих сигналах) и возможность почти мгновенного переключения между двумя частотами, то решить эту задачу можно с помощью AFG. Другим достоинством AFG является низкая цена, что делает его весьма привлекательным для приложений, не требующих гибкости AWG.

У AFG и AWG есть много общих черт, хотя по конструкции AFG является более специализированным прибором. AFG обладает уникальными преимуществами: он создает стабильные сигналы стандартных функций – в частности, широко применяемые синусоиды и меандры – обладающие высокой точностью и быстро перестраиваемые по частоте. Быстрая перестройка означает возможность быстрого и чистого перехода с одной частоты на другую.

Большинство AFG предлагает набор следующих широко используемых сигналов и функций:

Синусоида

Меандр

Треугольник

Свипирование

Импульс

Линейное нарастание

Модуляция

Гаверсинус

И хотя AWG тоже могут генерировать все эти сигналы, современные AFG обеспечивают улучшенное управление фазовыми, частотными и амплитудными характеристиками выходного сигнала. Кроме того, многие AFG позволяют модулировать сигнал внутренним или внешним источником, что очень важно для некоторых типов тестирования на соответствие стандартам. Старые модели AFG для создания выходных сигналов использовали аналоговые задающие генераторы с последующей обработкой сигнала. Последние модели AFG используют технологию прямого цифрового синтеза (DDS) тактовой частоты, с которой выборки сигнала извлекаются из памяти.

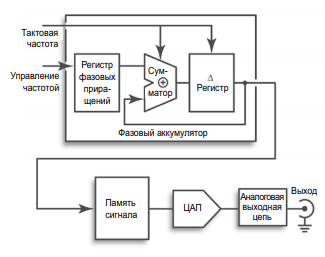

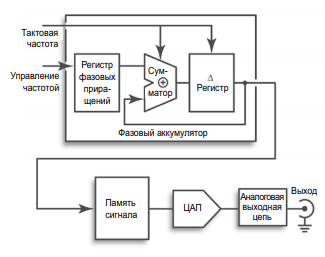

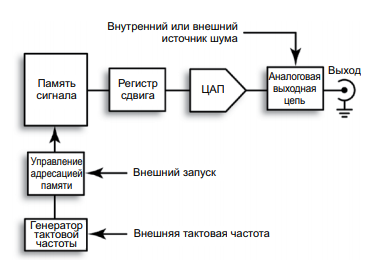

Рисунок 1 –Упрощенная архитектура AFG

Особенностью технологии DDS является синтез выходных сигналов и всех частот, используемых внутри прибора, только из одной тактовой частоты. На рисунке 1 показана упрощенная архитектура AFG, построенного на основе DDS. Регистр фазовых приращений в фазовом аккумуляторе принимает инструкции от контроллера частоты, показывающие, на сколько должна изменяться фаза выходного сигнала в каждом следующем периоде. В современных производительных AFG разрешение по фазе может достигать 2-30, что примерно равно 1/1000 000 000.

Выход фазового аккумулятора используется в качестве тактовой частоты для памяти сигналов. Работа этого прибора очень напоминает работу AWG, за тем исключением, что память сигналов содержит обычно лишь несколько базовых сигналов, таких как синус и меандр. Аналоговая выходная цепь обычно представляет собой фиксированный фильтр нижних частот, который обеспечивает поступление на выход только запрограммированной полезной частоты (подавляя проникновение тактовой частоты).

Чтобы лучше понять, как фазовый аккумулятор создает нужную частоту, представьте себе, что контроллер посылает значение “1” в 30-битный регистр фазовых приращений. Выходной регистр фазовых приращений фазового аккумулятора будет изменять фазу на 360/230 градусов в каждом периоде, поскольку полный период выходного сигнала соответствует фазе 360 градусов. Следовательно, значение “1” регистра фазовых приращений соответствует минимальной частоте выходного сигнала и требует 230 приращений для создания одного периода. Генератор будет работать на этой частоте до поступления нового значения в регистр фазовых приращений.

Значения больше “1” будут быстрее проходить полный период 360 градусов, создавая более высокую выходную частоту (некоторые AFG используют другой подход: они повышают выходную частоту, пропуская некоторые выборки, ускоряя, тем самым, считывание содержимого памяти). Единственное, что при этом меняется, это значение фазы, поступающее от контроллера частоты. Главную тактовую частоту менять не надо. Кроме того, это позволяет начинать генерацию сигнала с любой точки периода.

Рисунок 2 – Серия выборок, представляющих синусоиду (слева), реконструированная синусоида (справа)

Допустим, нам надо получить синусоиду, которая начинается с максимума положительной полуволны. Элементарная математика говорит, что этот максимум соответствует фазе 90 градусов.

Следовательно:

230 приращений = 360°; и

90° = 360° / 4; следовательно,

90° = 230 / 4

Когда фазовый аккумулятор получает значение, эквивалентное (230 / 4), он заставляет память сигналов начать генерацию с точки, содержащей положительный максимум синусоидального сигнала.

В памяти готовых сигналов типичного AFG хранится несколько стандартных сигналов. Обычно, наиболее частое применение находят синусоидальные сигналы и меандры. Сигналы произвольной формы хранятся в области памяти, доступной для перепрограммирования пользователем. Эти сигналы можно определять с той же гибкостью, как и в традиционных AWG. Однако архитектура DDS не поддерживает сегментирование памяти и последовательный вывод сигналов. Такими расширенными возможностями обладают только высокопроизводительные AWG.

Архитектура DDS обеспечивает исключительно высокую скорость перестройки частоты, упрощая программирование частотных и фазовых изменений, что полезно для тестирования устройств, использующих частотную модуляцию – например, компонентов радиостанций и спутниковых систем. И если вам хватает частотного диапазона AFG, то такой генератор идеально подходит для тестирования ЧМн и телефонных технологий со скачкообразной перестройкой частоты, таких как GSM.

И, хотя AFG не обладает возможностью создания практически любых форм сигналов, как это делает AWG, он может воспроизводить большинство широко распространенных сигналов, используемых в лабораториях, ремонтных центрах и конструкторских отделах. Кроме того, он обеспечивает превосходную скорость перестройки частоты. И, что немаловажно, AFG зачастую является самым экономичным решением.

2.3 Генераторы сигналов произвольной формы (AWG)

Хотите ли вы получить поток данных, в точности соответствующий по форме функции Лоренца, для измерения характеристик дискового накопителя, или сложномодулированный ВЧ сигнал для тестирования телефона GSM или CDMA, генератор сигналов произвольной формы (AWG) может создать сигнал любой мыслимой формы. При этом для создания нужного сигнала можно использовать множество методов – от математической формулы до «рисунка» сигнала.

В сущности, AWG представляет собой сложную систему воспроизведения, которая создает сигналы на основе сохраненных цифровых данных, описывающих постоянно изменяющиеся уровни напряжения сигнала переменного тока. Блок-схема этого прибора обманчиво проста. Если обратиться к более привычным терминам, AWG можно представить, как плеер компакт-дисков, который считывает сохраненные данные в реальном времени (в AWG – из собственной памяти сигнала; в CD плеере – с диска). Оба эти устройства выдают на выход аналоговый сигнал.

Для понимания принципа работы AWG нужно сначала усвоить общую концепцию цифровой дискретизации. Суть цифровой дискретизации полностью описывается ее названием: она определяет сигнал с помощью дискретных выборок, или точек данных, представляющих собой последовательность измеренных напряжений вдоль графика сигнала. Эти выборки можно определить, реально измеряя сигнал, например, осциллографом, или используя графические или математические методы. На рисунке 2 (слева) показана серия выборок. Все выборки получены через равные интервалы времени, хотя по виду кривой может показаться, что интервалы не равны. В AWG значения выборок сохраняются в двоичной форме в быстром Оперативном Запоминающем Устройстве (ОЗУ).

Используя сохраненную информацию, сигнал можно в любое время реконструировать, считывая значения из памяти и пропуская их через цифро-аналоговый преобразователь (ЦАП). Результат показан на рисунке 2 (справа). Обратите внимание, что выходная цепь AWG содержит фильтр, который объединяет отдельные точки в чистый, непрерывный выходной сигнал. В результате исследуемое устройство не «видит» отдельных точек сигнала, а воспринимает его как непрерывную аналоговую волну.

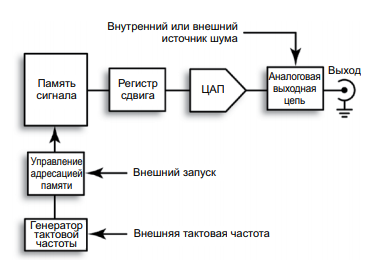

Упрощенная блок-схема AWG, реализующая описанные функции, показана на рисунке 3. AWG предлагает гибкость, практически не достижимую другими приборами. Обладая возможностью воспроизводить сигнал любой мыслимой формы, AWG может применяться практически везде, от моделирования работы антиблокировочной системы тормозов автомобиля до тестирования беспроводных сетей в предельных режимах.

Рисунок 3 – Упрощенная блок – схема

Описание ПЛИС и программной среды Quartus

Программируемая логическая интегральная схема (ПЛИС, англ. programmable logic device, PLD) — электронный компонент (интегральная микросхема), используемый для создания конфигурируемых цифровых электронных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования (проектирования). Для программирования используются программатор и IDE (отладочная среда), позволяющие задать желаемую структуру цифрового устройства в виде принципиальной электрической схемы или программы на специальных языках описания аппаратуры: Verilog, VHDL, AHDL и др. Альтернативой ПЛИС являются:

базовые матричные кристаллы (БМК), требующие заводского производственного процесса для программирования;

ASIC — специализированные заказные большие интегральные схемы (БИС), которые при мелкосерийном и единичном производстве существенно дороже;

специализированные компьютеры, процессоры (например, цифровой сигнальный процессор) или микроконтроллеры, которые из‑за программного способа реализации алгоритмов в работе медленнее ПЛИС.

непрограммируемые цифровые устройства и системы, настроенные на решение заранее известных задач, построенные на принципах т.н. "жесткой логики".

История развития ПЛИС

По мере развития цифровых микросхем возникло противоречие между возможной степенью интеграции и номенклатурой выпускаемых микросхем. Экономически оправдано было выпускать микросхемы средней интеграции, таких как регистры, счетчики, сумматоры. Более сложные схемы приходилось создавать из этих узлов. Разместить более сложную схему на полупроводниковом кристалле не было большой проблемой, но это было оправдано либо очень большой серийностью аппаратуры, либо ценой. Заказные микросхемы не могли удовлетворить возникшую потребность в миниатюризации аппаратуры. Решение могло быть только одним — предоставить разработчикам аппаратуры возможность изменять внутреннюю структуру микросхемы (программировать).

История развития программируемых логических интегральных схем начинается с появления программируемых постоянных запоминающих устройств. Первое время программируемые ПЗУ использовались исключительно для хранения данных, однако вскоре их стали применять для реализации цифровых комбинационных устройств с произвольной таблицей истинности. Однако данное решение имело существенный недостаток - экспоненциальный рост сложности устройства в зависимости от количества входов. Добавление одного дополнительного входа цифрового устройства приводит к удвоению требуемого количества ячеек памяти ПЗУ. Это не позволяет реализовать многовходовые комбинационные цифровые схемы.

Для реализации цифровых комбинационных устройств с большим числом входов были разработаны программируемые логические матрицы (ПЛМ). В иностранной литературе они получили название — PLA (англ. Programmable Logic Arrays). Именно программируемые логические матрицы можно считать первыми программируемыми логическими интегральными схемами (Programmable Logic Devices — PLDs)[2].

Некоторые производители для своих ПЛИС предлагают программные процессоры, которые можно модифицировать под конкретную задачу, а затем встроить в ПЛИС. Тем самым:

обеспечивается увеличение свободного места на печатной плате (возможность уменьшения размеров платы);

упрощается проектирование самой ПЛИС;

увеличивается быстродействие ПЛИС.

Проектирование на ПЛИС

Этапы проектирования ПЛИС

Задание принципиальной электрической схемы или программы на специальных языках описания аппаратуры: Verilog, VHDL, AHDL и др.

Логический синтез с помощью программ-синтезаторов (получение списка электрических соединений (в виде текста) из абстрактной модели, записанной на языке описания аппаратуры).

Проектирование печатной платы устройства с помощью системы автоматизированного проектирования (САПР) печатных плат (Altium Designer, P-CAD и др.), на которой размещается микросхема ПЛИС и прочие электронные компоненты (резисторы, конденсаторы, генераторы, АЦП, разъёмы и т.д.).

Создание файла конфигурации ПЛИС.

Загрузка файла в микросхему ПЛИС или отдельную микросхему памяти конфигурации. В результате загрузки конфигурации микросхема ПЛИС обретает заданную функциональность[3].

ПЛИС широко используется для построения различных по сложности и по возможностям цифровых устройств, например:

устройств с большим количеством портов ввода-вывода (бывают ПЛИС с более чем 1000 выводов («пинов»));

устройств, выполняющих цифровую обработку сигнала (ЦОС);

цифровой видеоаудиоаппаратуры;

устройств, выполняющих передачу данных на высокой скорости;

устройств, выполняющих криптографические операции, систем защиты информации;

устройств, предназначенных для проектирования и прототипирования интегральных схем специального назначения (ASIC);

устройств, выполняющих роль мостов (коммутаторов) между системами с различной логикой и напряжением питания;

реализаций нейрочипов;

устройств, выполняющих моделирование квантовых вычислений;

устройств, выполняющих обработку радиолокационной информации.

Классификация ПЛИС

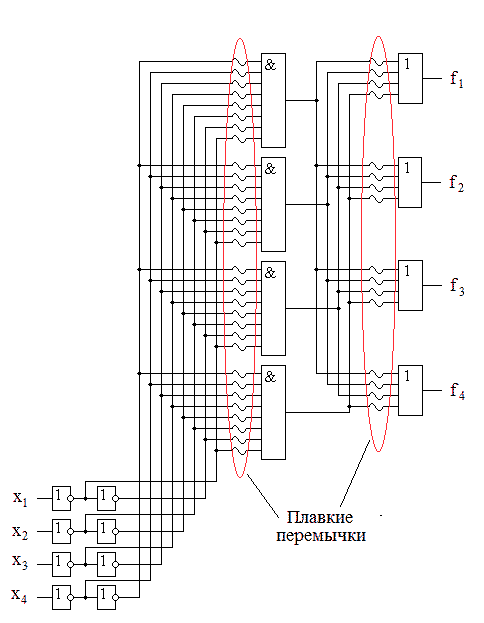

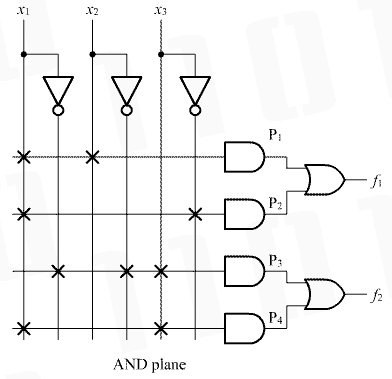

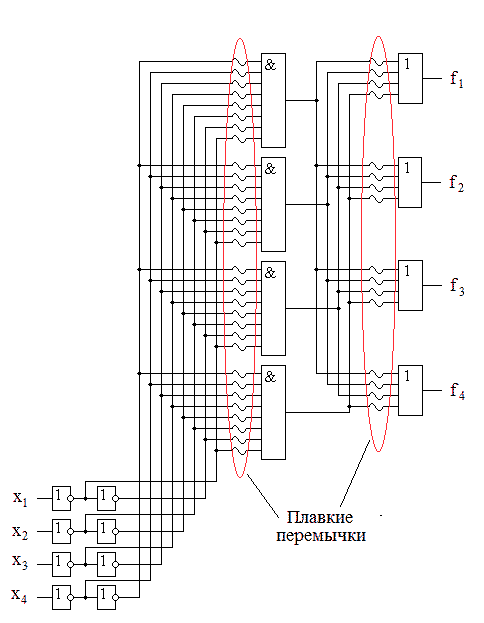

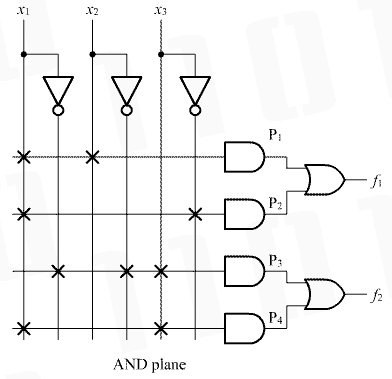

PLA (англ. Programmable Logic Arrays) — программируемая логическая матрица. Основная идея работы ПЛМ заключается в реализации логической функции, представленной в СДНФ — дизъюнктивной нормальной форме. В программируемой логической матрице обе матрицы логических элементов "И" и "ИЛИ" программируемы. На рисунке 4 приведена обобщенная структура программируемых логических матриц.

Рисунок 4 - Обобщенная структура программируемых логических матриц (ПЛМ)

PAL (англ. Programmable Array Logic) — программируемая матрица логики. В отличии от ПЛМ в ПМЛ матрица логических элементов "И" является программируемой, а матрица логических элементов "ИЛИ" фиксированной. Обобщенная структура программируемых матриц логики изображена на рисунке 5. Поскольку изготовить такие устройства проще, чем ПЛМ, они имеют меньшую стоимость и обладают улучшенными характеристиками, что привело к их высокой популярности.

Рисунок 5 - Обобщенная структура программируемых матриц логики (ПМЛ)

GAL (англ. Gate Array Logic) ПЛИС, имеющие программируемую матрицу «И» и фиксированную матрицу «ИЛИ».

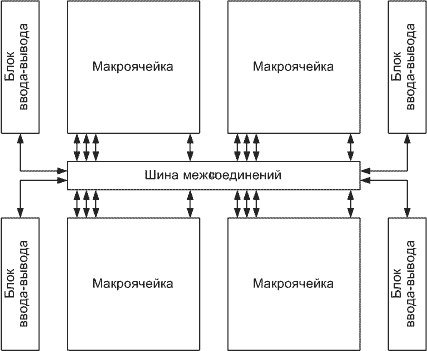

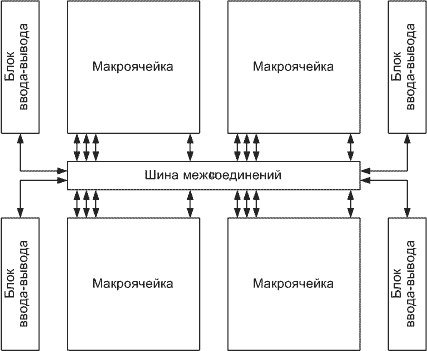

CPLD (англ. Complex Programmable Logic Device). Программируемая логическая интегральная схема CPLD состоит из нескольких макроячеек, расположенных на одном кристалле. Каждая макроячейка соединена с блоками ввода-вывода, осуществляющими формирование необходимого вида входов или выходов для работы с внешними схемами. Кроме того, все макроячейки и блоки ввода-вывода связаны между собой внутренними параллельными шинами. Приведенная на рисунке 5 микросхема CPLD состоит из четырех макроячеек, которые связаны между собой внутренними шинами и соединяются с блоками ввода-вывода. Макроячейка построена подобно ПЛМ микросхеме, к которой на выходе подключен D-триггер. К недостаткам можно отнести то, что трудно обеспечить эффективное применение всех макроячеек. Всегда часть макроячеек остается неиспользуемыми. Часто из макроячейки используется только триггер или логический элемент "2И" ("2ИЛИ"). Остальная часть схемы зря занимает площадь кристалла и потребляет ток от источника питания.

Рисунок 6 - Пример внутренней схемы CPLD

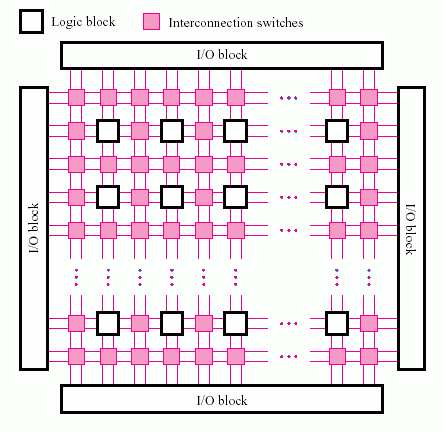

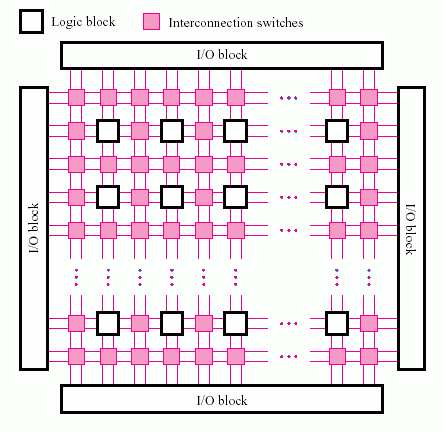

FPGA (англ. Field-Programmable Gate Array). Принцип работы FPGA существенно отличаются от принципа работы CPLD. FPGA является наследником комбинационных схем, реализованных на постоянных запоминающих устройствах (ПЗУ)[3]. Обобщенная структура микросхем FPGA приведена на рисунке 6.

Рисунок 7 - Обобщенная структура микросхем FPGA

Intel Quartus Prime - программируемое логическое устройство, разработанное Intel; до приобретения Intel Altera этот инструмент назывался Altera Quartus II. Quartus Prime позволяет анализировать и синтезировать HDL- проекты, что позволяет разработчику скомпилировать свои проекты, выполнять анализ времени, анализировать графики RTL, моделировать реакцию проекта на разные стимулы и настраивать целевое устройство с помощью программиста. Quartus Prime включает в себя реализацию VHDL и Verilog для аппаратного описания, визуального редактирования логических схем и моделирования векторных сигналов.

Функции программного обеспечения Quartus Prime включают:

SOPC Builder, инструмент в программном обеспечении Quartus Prime, который устраняет задачи ручной интеграции системы, автоматически генерируя логику межсоединений и создавая тестовую среду для проверки функциональности

Qsys, инструмент системной интеграции, который является следующим поколением SOPC Builder. Он использует оптимизированную по FPGA архитектуру сети на кристалле, которая удваивает производительность fMAX и SOPC Builder.

SoCEDS, набор средств разработки, служебных программ, программного обеспечения во время выполнения и примеры приложений, которые помогут вам разработать программное обеспечение для встроенных систем SoP FPGA.

DSP Builder, инструмент, который создает бесшовный мост между инструментом MATLAB / Simulink и программным обеспечением Quartus Prime, поэтому разработчики FPGA имеют возможности разработки, моделирования и проверки алгоритмов средств проектирования на уровне системы MATLAB / Simulink

Инструментарий интерфейса внешней памяти, который идентифицирует проблемы калибровки и измеряет поля для каждого сигнала DQS.

Генерация файлов JAM / STAPL для программистов внутрисхемного устройства JTAG.

Разработка генератора сигналов произвольной формы табличным методом в программной среде Quartus

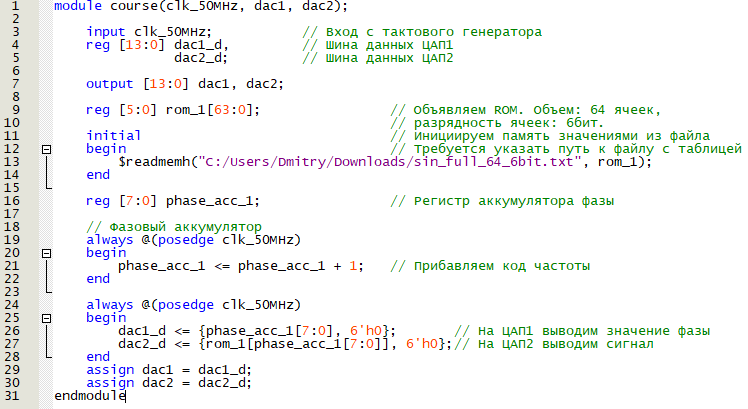

В Verilog память – это массив регистров. Объявляется следующим образом: reg [7:0] mem_name[1023:0]; «mem_name» память, которая содержит 1024 ячеек, каждая ячейка состоит из 8-битного регистра.

Доступ к отдельной ячейке осуществляется так: dac1_d <= mem_name[124] – 8-ми битное значение из 124-ой ячейки записывается в 8-битный регистр dac1_d.

Доступ к отдельному биту ячейки осуществляется так: assign led[0] <= mem_name[124][7] – Значение старшего (7-го) бита 124-ой ячейки назначается 0-му биту шины led.

Доступ к группе бит ячейки осуществляется так: assign led <= mem_name[124][7:4] Значение четырех старших бит 124-ой назначается шине led.

Память может быть инициализирована начальными значениями с помощью системных функций readmemh и readmemb. При компиляции проекта функции считывают значение из текстового файла и помещают их в указанную память. Файл для функции readmemh должен содержать данные в шестнадцатеричном формате, для функции readmemb – в двоичном.

Вызов функций должен происходить в блоке инициализации Inicial.

Общий синтаксис вызова следующий: $readmemh ( " file_name " , memory_name [ , start_addr [ , finish_addr ] ] ); где file_name – относительный путь к файлу и имя, memory_name – имя инициализируемой памяти, start_addr – начальный адрес для загрузки, finish_addr – конечный адрес. Последние два параметра опциональны.

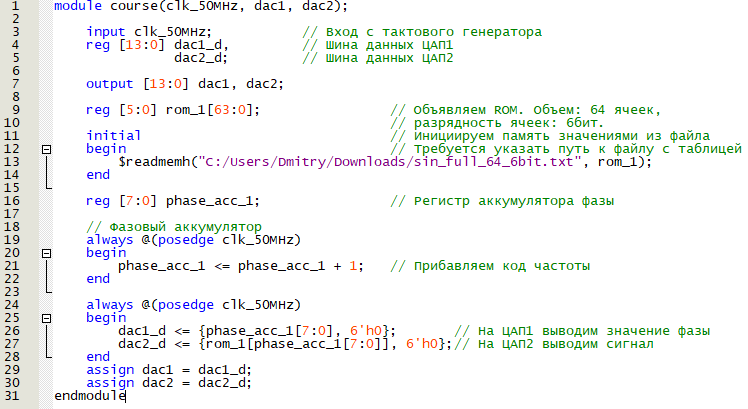

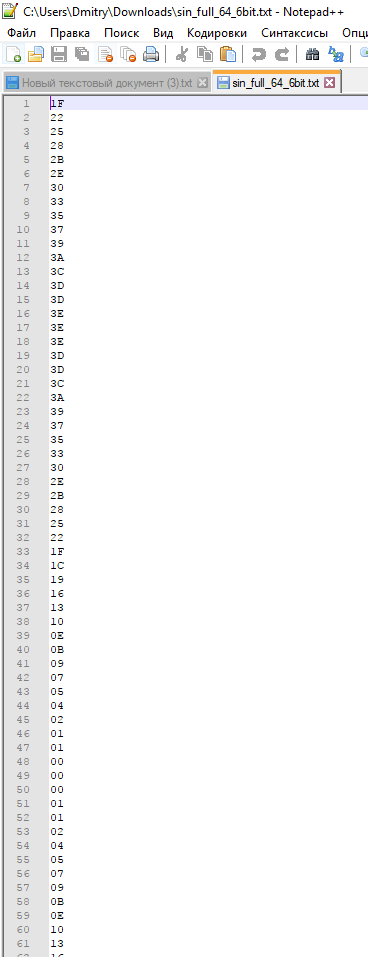

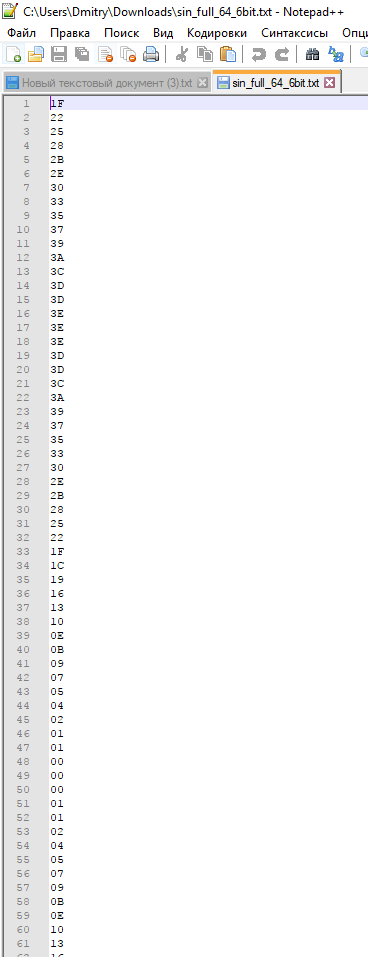

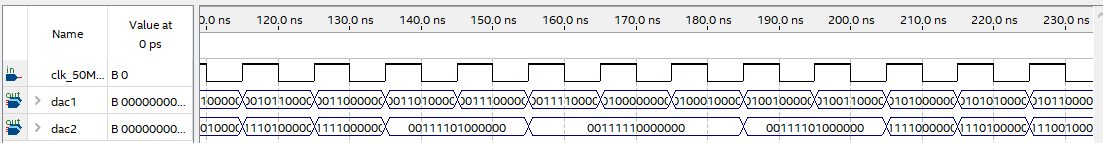

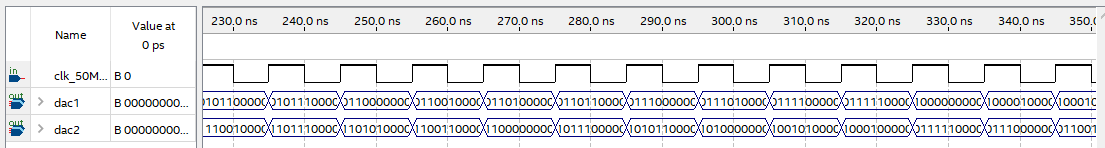

Программный код генератора, а также табличные значения в текстовом файле показаны на рисунке 8 и 9.

Рисунок 8 – Программный код генератора

Рисунок 9 – Текстовый файл с значениями

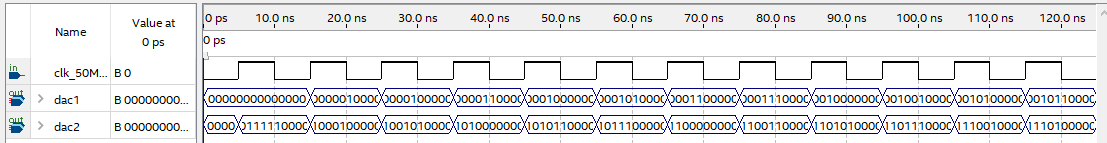

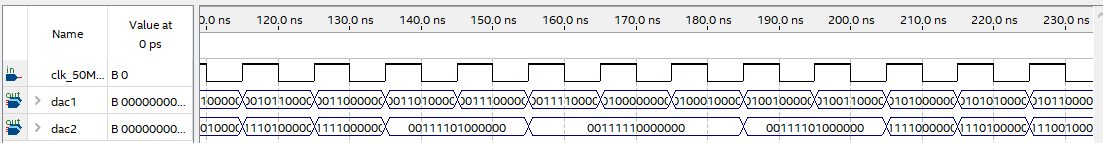

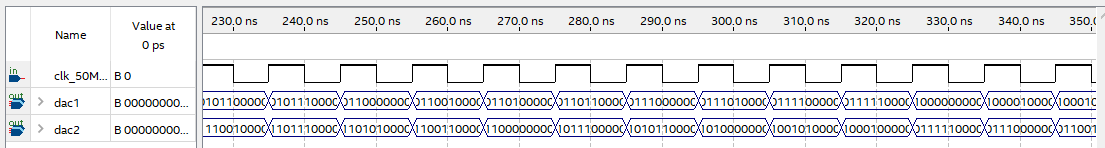

На 11 строчке кода происходит чтение текстового файла, в котором записаны 64 отсчета по 6 бит. Данные значения заносятся 6 битный массив регистров rom_1 на 64 ячейки.

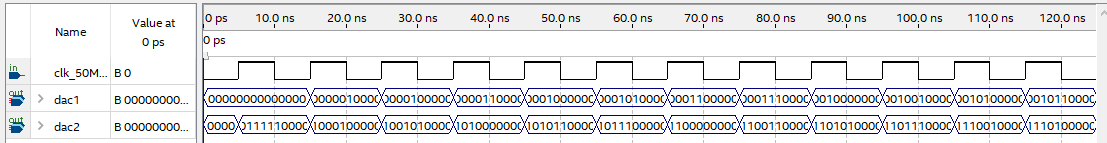

По каждому положительному перепаду генератора CLK происходит инкрементация регистра фазового аккумулятора, а также внесение в регистры dac1_d и dac2_d значений. Регистр dac1_d формирует синусоидальный сигнал, dac2_d – пилообразный.

С помощью встроенных инструментов произведена симуляция проекта (рисунок 10).

Рисунок 10 – Симуляция работы программы

Заключение

Генераторы сигнала являются неотъемлемой частью современной цифровой индустрии. В ходе выполнения курсового проекта были изучены различные способы генерации сигналов, а также виды генераторов.

В программной среде Quartus разработан работоспособный образец генератора сигнала табличным методом, задаваемый в отдельном текстовом файле. Устройство способно генерировать сигнал с 64 отсчетами на период с 6 битной точностью.

Список используемой литературы

Берикашвили В.Ш. Электроника и микроэлектроника: импульсная и цифровая электроника, 2018 г. – 188 с.

Википедия. Свободная энциклопедия [Электронный ресурс]. Режим доступа: URL https://ru.wikipedia.org/wiki/Шифратор

Миловзоров О. В. Электроника, 2015 г.

Андык В.С. Автоматизированные системы управления технологическими процессами на ТЭС, 2018 г. – 248 с.

Кузовкин В.А. Электротехника и электроника, 2018 г. – 226 с.

|

Скачать 255.27 Kb.

Скачать 255.27 Kb.