Реферат по к580. К580 теория. 1. микропроцессорные устройства 1 Структура микропроцессорного устройства

Скачать 237.5 Kb. Скачать 237.5 Kb.

|

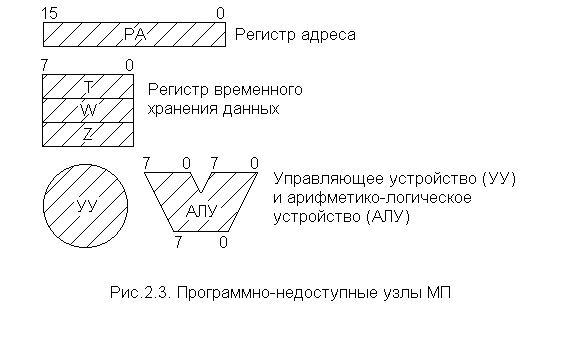

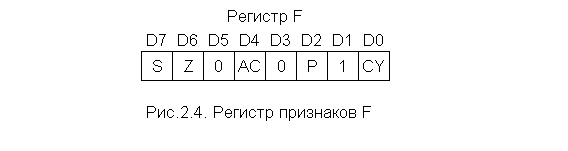

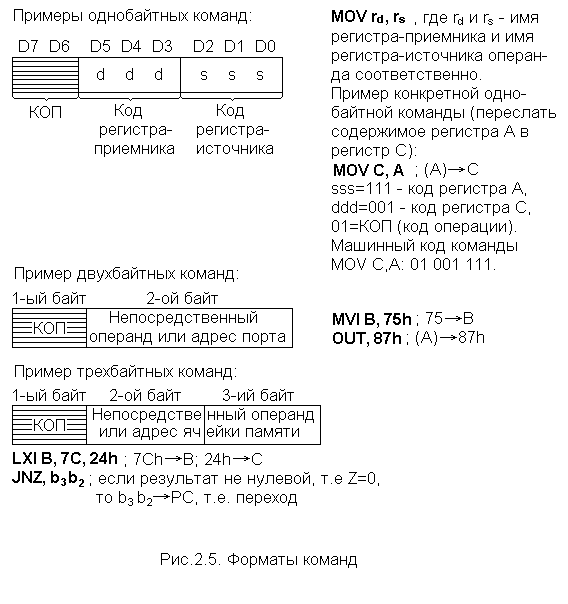

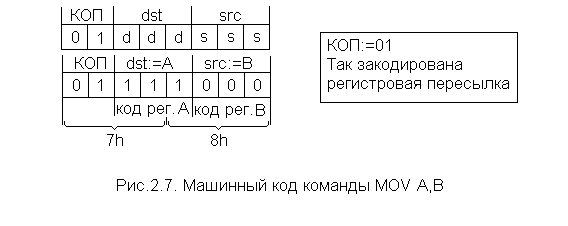

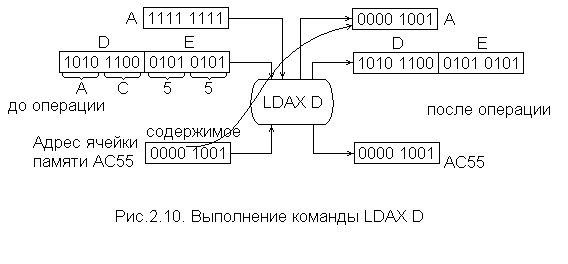

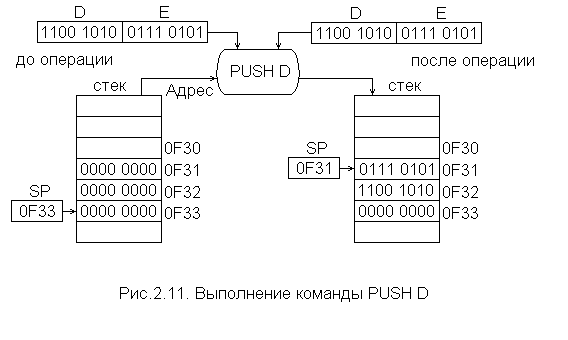

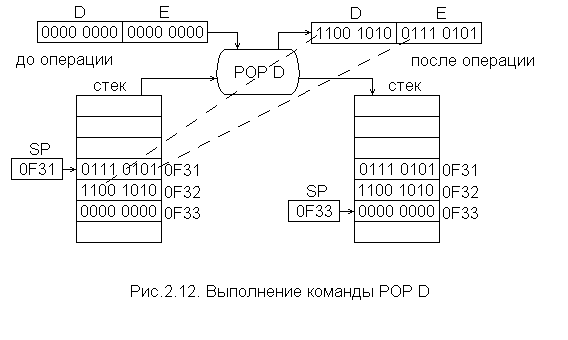

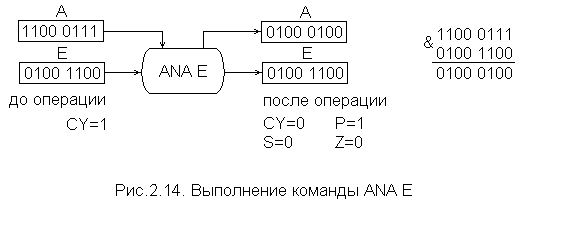

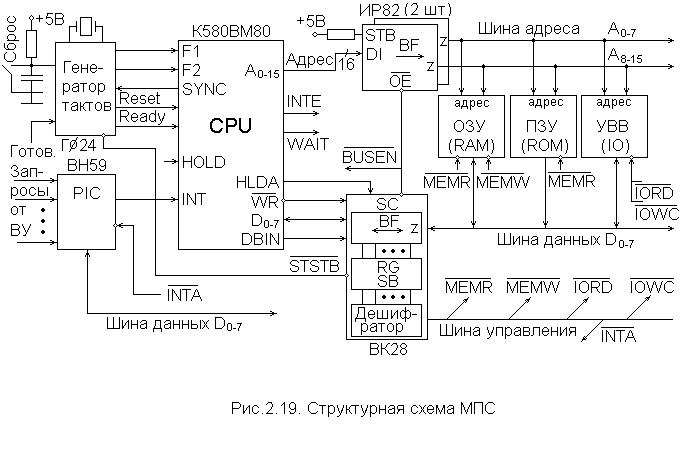

1 2 ВВЕДЕНИЕ Современные микропроцессоры представляют собой весьма сложные по устройству изделия микроэлектроники, выпускаются многочисленных классов, функциональных возможностей и разнообразных архитектурных решений. Микропроцессорная техника стремительно и многонаправленно развивается и совершенствуется, интегрируя новейшие достижения микроэлектроники и схемотехники. Одним из важнейших направлений развития микропроцессорной техники является создание универсальных микропроцессоров, предназначенных для применения в вычислительных системах: персональных компьютерах, рабочих станциях, серверах, параллельных супер ЭВМ. Создание микроконтроллеров и цифровых сигнальных процессоров является также важнейшим направлением развития микропроцессорной техники. Однокристальные микроконтроллеры выпускаются различных типов, отличаются назначением, сложностью, архитектурными решениями и т.д. Изучение микропроцессорных средств, являясь достаточно сложной задачей требует оптимального выбора тематики и временных затрат на их освоение. Значительный интерес для изучения представляют первые семейства 8-разрядных микропроцессорных БИС: 8080, 8085 (Intel), Z80 (Zilog), МС6800, МС6809 (Motorola), MCS6500 (MOS Technology). Эти микросхемы стали доступными и классическими примерами построения на их основе МП-систем. Особенно подробно описаны в учебно-методической и инженерно-технической литературе микропроцессорные БИС семейства 8080 и 8085 и их отечественные аналоги серии К580 и К1821. Поэтому начальные знания о микропроцессорах и микропроцессорных системах целесообразно получить, используя в качестве примеров семейства БИС серии К580, 8080. Это позволит эффективно освоить простейшие средства и далее двигаться к более совершенным, более сложным. 1. МИКРОПРОЦЕССОРНЫЕ УСТРОЙСТВА 1.1 Структура микропроцессорного устройства Наиболее широко применяется магистрально-модульный принцип построения микропроцессорных систем (МПС). Упрощенная структура такой МПС приведена ниже. Центральным устройством в системе является микропроцессор (МП), выполняющий арифметические и логические операции над данными, осуществляющий управление выборкой команд и данных из памяти и организующий взаимодействие всех устройств, входящих в систему. Работа МП происходит под воздействием тактовых сигналов, вырабатываемых схемой синхронизации, часто выполняемой в виде отдельной микросхемы (генератора тактовых импульсов). Программы МПС размещаются в модулях постоянных запоминающих устройств (ПЗУ) и оперативных запоминающих устройств (ОЗУ). Микропроцессорные устройства и МПС содержат различные средства ввода-вывода информации. Шины адреса, данных и управления объединяют все устройства в единую систему. Периферийные устройства подсоединяются к шинам через программируемые периферийные адаптеры, осуществляющие передачу информации в параллельном или последовательном кодах. Наличие программно-настраиваемых адаптеров делает весьма гибкой и функционально богатой систему ввода-вывода информации в МПС. Для разработки микропроцессорных устройств и МПС промышленность выпускает семейства микропроцессорных БИС, позволяющие удобную реализацию всех необходимых подсистем. В настоящее время выпускается большое разнообразие однокристальных микроконтроллеров разных классов, на базе которых можно создавать весьма совершенные микропроцессорные устройства, микро ЭВМ, МПС.  Подготовка списка команд называется программированием, а подготовленный список команд представляет собой программу, которая заносится в ПЗУ или ОЗУ и предписывает микропроцессору определенные действия. МП считывает из памяти команду и выполняет ее. Далее МП формирует адрес следующей команды в программе, считывает, выполняет и формирует адрес новой команды. Так функционирует ЭВМ. 1.2 Основные понятия (термины) Микро ЭВМ - это цифровая ЭВМ, выполненная на микропроцессорных БИС и имеющая малые размеры. Простейшая микро ЭВМ состоит из пяти частей: устройства ввода, устройства управления, арифметико-логического устройства, памяти и устройства вывода. Микропроцессор - это микросхема, выполняющая арифметические и логические операции над данными и осуществляющая программное управление вычислительным процессом. Микропроцессорный комплект (МПК) или серия микропроцессорных БИС представляет набор взаимно совместимых микросхем, позволяющих разработку микро ЭВМ, микропроцессорных систем (МПС). Микропроцессорной системой обычно называют специализированную информационную или управляющую систему, построенную на основе микропроцессорных БИС. Микроконтроллер представляет собой однокристальную микро ЭВМ с небольшими вычислительными ресурсами и упрощенной системой команд, ориентированной на выполнение процедур логического управления различным оборудованием, или, в общем случае, систему команд, ориентированную на удобное выполнение определенного типа задач. Логическая организация микропроцессоров и МПС направлена на достижение универсальности применения, высокой производительности вычислений. Логическую организацию МП и МПС называют их архитектурой. Встроенной системой управления называют систему управления, конструктивно интегрированную в оборудование: станок, робот, стиральную машину, принтер, автомобиль и т.д. Индустриальные компьютеры имеют развитый набор стандартных устройств сопряжения с объектом (УСО) и являются универсальными средствами управления для широкого круга применений. Промышленные контроллеры в отличии от однокристальных микроконтроллеров содержат средства адаптации языка программирования под конкретную область применения и средства объединения их в системы. Универсальные микропроцессоры предназначаются для применения в вычислительных системах, персональных ЭВМ, рабочих станциях и супер-ЭВМ. Цифровые сигнальные процессоры (ЦСП) ориентированы на обработку в реальном времени цифровых потоков, образованных путем оцифрования аналоговых сигналов. Вопросы и задания 1.1.Назовите основные функциональные устройства ЭВМ и поясните их назначение. 1.2.Изобразите по памяти структурную схему ЭВМ. 1.3.Дайте определение понятий «микропроцессор», «семейство микропроцессорных БИС», «МПК БИС». 1.4.Назначение и различие персональных и индустриальных компьютеров. 1.5.Назначение однокристальных и промышленных контроллеров. 1.6.Поясните понятие «встроенная микропроцессорная система управления». 2. МИКРОПРОЦЕССОР К580ВМ80 2.1. Структура микропроцессора Микропроцессор К580ВМ80 (далее будем называть ВМ80) является аналогом микропроцессора 8080, выпущенного фирмой Intel в 1974 г. Микропроцессор ВМ80 представляет собой функционально законченный однокристальный универсальный 8-разрядный микропроцессор с фиксированной системой команд. В структурной схеме ВМ80 (рис.2.1) можно выделить следующие ее части: арифметико-логическое устройство (АЛУ), блок регистров, буферные схемы, управляющее устройство.  Блок регистров ВМ80 Блок регистров ВМ80 содержит 8-разрядные программно-доступные регистры: А (регистр-аккумулятор); В, С, D, Е, Н, L (регистры общего назначения); F (регистр признаков-флагов); 16-разрядные специализиро-ванные регистры; программный счетчик СК (РС); регистр-указатель стека УС (SР); сдвоенный регистр косвенного адреса HL (Н-регистр старшего полуадреса, L-регистр младшего полуадреса). А также имеются непосредственно недоступные программе регистры: 8-разрядный регистр команд (РК); 8-разрядные регистры временного хранения Т, W, Z; 16-разрядный регистр адреса РА. Содержимое пар регистров В и С, D и Е, H и L можно использовать в качестве слов двойной длины, т.е. 16-разрядных слов. Регистры общего назначения (РОН) используются для хранения операндов, промежуточных и конечных результатов, а также адресов при косвенной адресации данных. Регистр-аккумулятор А является особым в команде, в явном виде не адресуется, что позволяет упростить формат команд. Регистр А используется в качестве источника одного из операндов и приемника результата выполнения операции. Поэтому аккумулятор строится на основе двухступенчатых триггеров, что позволяет ему одновременно быть регистром-источником операнда и регистром-приемником результата выполнения операции. На использование аккумулятора в операции указывает код операции команды, т.е. в отношении аккумулятора применяется подразумеваемая адресация, что позволяет применять одноадресные команды, имеющие сравнительно короткий формат. К остальным программно-доступным регистрам применяется подразумеваемая или укороченная (регистровая) адресация, задаваемая коротким номером регистра в команде. Механизмы адресации будут рассмотрены ниже. Использование регистра А и РОН позволяет при выполнении команд уменьшить количество обращений к памяти и этим самым повысить быстродействие микропроцессора. В блоке регистров МП имеется схема инкремента/декремента, которая без привлечения АЛУ выполняет операцию прибавления/вычитания 1 над содержимым регистров. Схема инкремента/декремента позволяет реализовать процедуры автоматического задания приращений при операциях с адресами как в указателе стека (регистре SP), так и в программном счетчике (регистре РС). При выполнении операций в МП возникает потребность в кратковременном хранении некоторых операндов и результатов выполнения операций. Для этого служат регистры временного хранения данных T, W, Z. Для повышения эффективности операций с двухбайтными операндами и операций пересылок двухбайтных адресов имеется возможность оперировать с содержимым регистровых пар В и С, D и Е, Н и L. В состав блока регистров входит регистр-защелка адреса памяти РА. Любая пара регистров (ВС, DE, HL) может быть использована для задания адресов команд и данных в программе. Такой адрес под воздействием соответствующих команд может быть загружен в регистр-защелку РА и модифицирован (посредством схемы инкремента/декремента) в процессе загрузки. Регистр-защелка РА передает адрес в буфер ША и далее в шину адреса. Регистр команд РК служит для запоминания первого байта команды на все время ее выполнения. Код команды из этого регистра используется устройством управления для выработки последовательностей сигналов как для управления внутренними узлами МП, так и для управления внешними устройствами (памятью, портами и др.). Арифметико-логическое устройство(АЛУ) АЛУ выполняет арифметические и логические операции над 8-разрядными двоичными числами и представляет собой комбинационно-логическую схему. К одному из входов схемы АЛУ всегда подключен аккумулятор, к другому через регистр Т может быть подключен любой из регистров общего назначения. АЛУ непосредственно связано с регистром признаков F, в соответствующих разрядах которого фиксируются особенности выполнения каждой операции: нулевой результат в аккумуляторе - Z, перенос из старшего/ заем в старший разряд - CY, знак результата - S, паритет - Р и вспомогательный перенос из младшего полубайта - АС. Наличие в МП регистра признаков упрощает осуществление программных переходов в зависимости от состояния одного или более триггеров признаков. АЛУ позволяет в процессе регистровых “пересылок с перекосом” выполнять операции сдвига на один разряд вправо или влево. В состав АЛУ входит комбинационная схема десятичной коррекции ДК, которая под воздействием специальной команды DAA преобразует результат сложения из двоичной формы в двоично-десятичную. АЛУ выполняет простейшие арифметические операции сложения, вычитания; логические: конъюнкции, дизъюнкции, сложения по модулю 2; операции сравнения, сдвига. Выполнение более сложных операций (умножение, деление, вычисление элементарных функций) может быть реализовано по разработанным подпрограммам. Стековая память Микропроцессор ВМ80 содержит средства для организации стековой памяти, позволяющей безадресное задание операндов. В общем случае стек представляет собой последовательность регистров или ячеек памяти, снабженных указателем стека, в котором автоматически при записи и считывании устанавливается адрес последней занятой ячейки стека (вершины стека). В стеке реализуется принцип обслуживания “последний пришел - первый вышел”. Этот принцип при обращении к стеку реализуется автоматически. Поэтому команды записи и считывания не содержат адрес ячейки стека. Микропроцессор ВМ80 имеет только регистр-указатель стека (SP) и соответствующие цепи управления. Сам стек реализуется в оперативной памяти путем записи в указатель стека SP адреса ячейки памяти, являющейся исходной вершиной стека. Буферные схемы Двунаправленный буфер шины данных осуществляет логическое и электрическое разделение внутрипроцессорной шины данных и внешней, системной ШД. Буфер состоит из регистра-защелки и выходной схемы с тремя состояниями, т.е. выходной схемы, обеспечивающей на выходе состояния логических 0 и 1 и третье состояние, реализующее полное электрическое отключение от нагрузки (высокоимпедансное состояние). Наличие такого буфера дает возможность отключать устройства, подключенные к общей системной шине в МП- системе. При выполнении операций вывода данных буферная схема передает в системную шину данных содержимое буферного регистра-защелки, на вход которого по внутренней шине с одного из регистров ВМ80 загружен код, подлежащий выдаче. При выполнении ввода данных в микропроцессор внутренняя шина данных подключается к выходным цепям регистра-защелки буфера, загрузку которого из внешней ШД производит буферная схема под управлением команды. Буферная схема переходит в высокоимпедансное Z-состояние при выполнении МП- операций, не связанных с вводом или выводом. Буферная схема шины адреса БА - однонаправленная, обеспечивает передачу адресов команд, данных и адресов устройств ввода-вывода. Выход буфера адреса также может переходить в Z-состояние. Это позволяет использовать ША другим устройствам, например контроллеру прямого доступа к памяти и др. Устройство управления Устройство управления (или схема управления) вырабатывает управляющие сигналы, необходимые для выполнения команды. В основе этой схемы действует цифровой автомат. В схеме управления можно выделить следующие средства: - Регистр команд РК, служащий для приема кода команды (первого байта) и хранения этого кода на время ее выполнения; - Дешифратор кода команды и выработки сигналов управления микрооперациями в соответствии с «зашитой» микропрограммой выполнения команды; - Схему формирования машинных тактов, машинных циклов; - Схему выборки РОН, участвующих в операции, представляющую собой дешифратор разрядов кода команды, указывающий номер регистра источника и регистра приемника операндов; - Схему анализа переходов, которая анализирует состояние триггеров регистра признаков F при выполнении команд условных переходов; - Схему формирования и выдачи кода типа текущего машинного цикла, на основе которого можно формировать расширенный набор сигналов для управления памятью, устройствами ввода-вывода, прерываниями, т.е. МП-системой; - Схему анализа прерываний, содержащую триггер разрешения прерываний и триггер запроса прерываний. Анализ наличия запросов МП ВМ80 осуществляет в последнем такте последнего машинного цикла текущей команды; - Схему анализа готовности, которая проверяет сигнал высокого уровня на линии “Ready” в конце второго такта машинного цикла; - Схему анализа запроса шин (входная линия HOLD), обеспечивающую возможность реализации режима прямого доступа к памяти. Упражнение 2.1. 2.1.Изобразите по памяти структуру МП ВМ80 и поясните назначение образующих ее узлов. 2.2Поясните функции, выполняемые АЛУ. 2.3.Какие признаки формируются и при выполнении каких операций? 2.4.Назначение регистра IR инструкций (команд). 2.5.Зачем регистр-аккумулятор имеет структуру с двумя элементами памяти? Пояснение выполните на примере выполняемых команд. 2.6.Поясните назначение регистра Т временного хранения операнда на примерах выполнения команд. 2.7.Поясните состояние узлов МП после воздействия сигнала Reset. 2.8.Поясните последовательность действий МП при начальном пуске (включении питания или действия сигнала Reset). 2.9.Каково назначение блока десятичной коррекции и алгоритм его работы? 2.10.Каково назначение регистров А, В, С, D, E, H, L и ячейки М? Пояснение выполните на примерах команд, выполняемых микропроцессором. 2.2. Программная модель микропроцессора и микропроцессорной системы Модель микропроцессора содержит только узлы, наиболее важные для понимания процесса его работы. Модель может содержать программно-доступные и программно-недоступные узлы. На рис.2.2 представлены программно-доступные (адресуемые в командах в явной или неявной форме) узлы МП, памяти и устройств ввода-вывода. На рис.2.3 указаны программно-недоступные узлы МП, наиболее существенные для процесса выполнения команд. В программной модели выделены регистры В, С, D, E, H, L, A. Эти регистры предназначены для хранения данных. Они находятся в полном распоряжении программиста и единообразно участвуют в арифметических и логических операциях. К этой же группе отнесена так называемая ячейка памяти М, адрес которой помещен в регистровую пару HL. Ячейка памяти М также предназначена для хранения данных и находится в полном распоряжении программиста после того, когда ее адрес загружен в регистровую пару HL. При этом она так же как и РОН единообразно участвует в арифметических и логических операциях. Все РОН, в том числе и ячейка М, могут использоваться для создания программно-управляемых счетчиков.   Регистр А выполняет функции аккумулятора. В двухоперандных операциях он является источником одного операнда и приемником результата выполнения команды. Регистр признаков F содержит признаки выполнения операций. Формат регистра F приведен на рис. 1..4.  В регистре F фиксируются признаки: CY - признак переноса/заема. Если при выполнении команды возник перенос из старшего разряда или заем в старший разряд, то CY=1, иначе CY=0. Р - признак паритета. Если число единиц в байте результата четно, то Р=1, иначе Р=0. АС - признак вспомогательного переноса. Если есть перенос между тетрадами байта, то АС=1, иначе АС=0. Z - признак нуля. Если результат равен нулю, то Z=1, иначе Z=0. S - признак “знака”, принимает значение старшего разряда результата. Группы регистров управления ВС, DE, HL являются указательными. Они предназначены для хранения 16-битных адресов, обеспечивают при этом косвенную адресацию и динамическое вычисление адреса ячейки памяти. Указательный регистр SP содержит адрес ячейки оперативной памяти, являющейся текущей вершиной стека. Содержимое SP автоматически и последовательно уменьшается на 2 при выполнении команд записи в стек. А при выполнении команд считывания из стека, содержимое регистра SP автоматически увеличивается на 2. Одна стековая команда записи осуществляет запись содержимого указанной в команде регистровой пары, т.е. два байта. При считывании из стека содержимое двух ячеек вершины стека заносится в регистровую пару, указанную в команде считывания. Регистр инструкций IR доступен неявно. В этот регистр помещается первый байт команды, выбираемой из памяти при выполнении микропроцессором программы.  Указательный регистр РС выполняет функции основного адресанта, называется программным счетчиком или счетчиком команд (СК). Содержимое РС автоматически увеличивается на 1 при выборке очередного байта команды (или очередной команды) из памяти в процессе выполнения программы. Указательный регистр РС выполняет функции основного адресанта, называется программным счетчиком или счетчиком команд (СК). Содержимое РС автоматически увеличивается на 1 при выборке очередного байта команды (или очередной команды) из памяти в процессе выполнения программы.Регистровая пара PSW называется словом состояния процессора. Она образуется регистрами A и F. 2.3. Форматы команд и данных Команды микропроцессора ВМ80 имеют однобайтный, двухбайтный и трехбайтный форматы. Поле команды содержит информацию (в кодах): о типе операции (код операции), об адресе операнда, типе обращения к памяти, о количестве байт в команде. Примеры команд приведены на рис.2.5. 2.4. Режимы адресации Способ определения источников и приемников операндов называют режимами адресации данных. Для микропроцессоров разработано около двух десятков режимов адресации. В микропроцессоре ВМ80 используются четыре режима адресации данных: 1. Прямая (абсолютная) адресация. Это наиболее простая, но найменее экономичная адресация. В поле самой команды содержится полный 16-битный адрес операнда в памяти (рис. 2.6,а.). С помощью прямой адресации можно обращаться к любой ячейке в адресном пространстве. 2. Непосредственная адресация. Данные (байт или два байта) находятся непосредственно в команде во втором или во втором и третьем ее байтах (рис. 2.6,б). 3. Регистровая адресация. Операндом является содержимое адресуемого в команде регистра (рис.2.6,в.). Команды с регистровой адресацией имеют однобайтный формат, выполняются достаточно быстро. В однобайтных командах с неявной адресацией подразумевается, что операнд находится в определенном внутреннем регистре МП и его специально адресовать не надо. Например, все команды сдвига микропроцессора ВМ80 или команда инвертирования оперируют содержимым аккумулятора. 4. Косвенная регистровая адресация (рис.2.6,г) позволяет компактно адресовать все пространство памяти. В этом режиме в поле команды содержится указание на регистровую пару, содержащую адрес операнда (данных). Косвенная адресация широко применяется при обращении к структурам данных типа массивов. Вопросы и задания 2.11Какие устройства образуют программную модель МП ВМ80 и МПС на его основе? 2.12.Убедитесь в своих знаниях программной модели МП ВМ80 и МПС на его основе, изобразив программно -доступные узлы. 2.13.Какие команды определяют доступ к устройствам ввода-вывода? 2.14.Назовите очень важные устройства МП, которые программно-недоступны. 2.15.Поясните кодирование команд, их форматы и назначение. 2.16.Приведите примеры одно-, двух- и трехбайтных команд и определите по справочнику их машинные коды. 2.17.Поясните способы адресации к командам. 2.18.Адресация данных в МПС на МП ВМ80.  2.19.Адресация к стеку в МПС на ВМ80. 2.20.Определите способы адресации: STA 80C2h; IN, 58h; ADI 4Ah; OUT, 58h; MOV C, M; LHLD 94C2h; MOV E, D; PUSH PSW. 2.21.Поясните почему ВМ80 может выполнять только установленные для него команды и какими его средствами это определяется? 2.22.На какие группы можно подразделить систему команд МП ВМ80? 2.5. Система команд МП Систему команд МП можно представить в виде 76 мнемокодов (ассемблерных кодов). Здесь команды ВМ80 рассматриваются с позиции описания действий микропроцессора. Всю систему команд можно по функциональным признакам разделить на группы: Пересылки/загрузки; Положительных/отрицательных приращений; Арифметические; Логические; Сдвига в аккумуляторе; Передачи управления; Ввода-вывода; Специальные. 2.5.1. Команды пересылки/загрузки В любой прикладной программе возникает необходимость передать содержимое регистра-источника (src-регистра) в регистр-приемник (dst-регистр). Эту операцию выполняют многочисленные команды пересылок dst(src). При этом содержимое src-регистра и состояние флажков в регистре признаков F не изменяются. Обобщенный мнемокод команды пересылок можно представить в виде MOV dst, src; содержимое регистра-источника пересылается в регистр-приемник, т.е. dst(src). В качестве src и dst могут быть указаны любые РОН (В, С, D, E, H, L), а также регистр А и ячейка М. Пересылки возможны из любого РОН, регистра А и ячейки М в любой РОН, регистр А и ячейку М. Микропроцессор не выполняет только пересылку из ячейки М в ячейку М. В описании системы команд, приведенных в методических указаниях, регистр-источник операнда обозначается rs, регистр-приемник rd, а обобщенный мнемокод регистровой пересылки в методических указаниях имеет вид: MOV rd, rs; (rs) rd; Пусть необходимо переслать содержимое регистра В в регистр А. Здесь src:=В, а dst:=А. Обобщенный мнемокод примет вид MOV A, B: т.е. содержимое регистра В пересылается в регистр А. Рассмотрим машинный код команды MOV A, B (рис.2.7). Обобщенный вид команды. Кодирование команды MOV dst, src. sss: = код рег. src; ddd: = код рег. dst Кодирование конкретной команды MOV A, B: Код регистра В:=000=SSS. Надо поставить в поле src вместо sss код 000. Код регистра А:=111 надо поставить вместо ddd. Машинный код команды MOV А, В будет 0111 1000 В = 78h.  Рассмотрим действие команды MOV A, B (рис.2.8).  Содержимое регистра В записалось в регистр А, при этом содержимое регистра В не изменилось. Непосредственная загрузка регистров. Это двухбайтные команды, обобщенный вид мнемокода: MVI rd, b2; где b2 - второй байт команды, является непосредственным операндом (числом), который загружается в регистр-приемник rd. Пусть необходимо число 75h загрузить в аккумулятор. Применим команду: MVI A, 75h; 75h A; Двухбайтные загрузки в регистровые пары. Обобщенный вид: LXI rp, b3b2; где rp: B, D, H, SP, т.е. регистровые пары BC, DE, HL, SP, b3b2 - 16-разрядное число. Действие команды: b2 rPL , b3 rPH. Пример: Загрузить указатель стека SP (рис.2.9). В результате выполнения этой команды b2=A0h - загружается в младшую часть указателя стека SPL A0h, b3=28h - загружается в старшую часть SP, т.е. SPH 28h.   Запоминания/загрузки регистра А и регистровой пары HL. STA b3 b2; (А) b3b2, т.е. содержимое А запоминается в ячейке b3b2. LDA b3 b2; (b3b2) А, т.е. содержимое ячейки b3b2 заносится в регистр А. STAX rp; (A) (rp), т.е. содержимое регистра А запоминается в ячейке, адрес которой находится в регистровой паре rp: BC, DE. LDAX rp; ((rp)) A, т.е. содержимое ячейки, адресуемой указанной регистровой парой, заносится в регистр А. Рассмотрим действие команды LDAX D (рис.2.10). В результате содержимое ячейки, адрес которой находится в регистровой паре DE, записалось в регистр А. SHLD b3b2; (L) b3b2, (H) b3b2+1. Содержимое HL пересылается в ячейки памяти с прямой адресацией. Запись содержимого регистровых пар в стек. PUSH rp, где rp: BC, DE, HL, PSW. (rPH) (SP)-1, (rPL) (SP)-2, (SP)-2 SP. Рассмотрим выполнение команды PUSH D (рис.2.11). При выполнении команды PUSH D МП выполняет следующие действия: 1) (SP)-1 SP; 2) (D) (SP) = 0F32; 3) (SP)-1 SP; 4) (E) (SP) = 0F31. Вывод из стека в регистровые пары: POP rp. Эта команда считывает содержимое вершины стека (двух ячеек) и заносит в указанную регистровую пару rp, где rp: BC, DE, HL, PSW. Рассмотрим действие вывода из стека на примере выполнения команды POP D (рис.2.12).   При выполнении команды POP D МП выполняет следующие действия: 1) ((SP)) D; 2) (SP)+1 SP; 3) ((SP)+1) E; 4) (SP)+1 SP. Обмен между регистрами DE и HL: XCHD; H D, L E. Обмен вершины стека с HL: XTHL; (L) ((SP)), (H) ((SP)+1). Пересылка содержимого HL в указатель стека SP: SPHL; (HL) SP. 2.5.2. Команды положительных/отрицательных приращений Признаки результата моди- S Z AC P CY ф + + + +     ицируются, кроме CY: ицируются, кроме CY: Положительные/отрицательные приращения РОН, регистра А и ячейки М. I  NR r; (r)+1 r, где r: B, C, D, E, H, L, M. A. NR r; (r)+1 r, где r: B, C, D, E, H, L, M. A.DCR r; (r)-1 r, Положительные/отрицательные приращения регистровых пар: I  NX rp; ( rp )+1 rp , где rp: BC, DE, HL. NX rp; ( rp )+1 rp , где rp: BC, DE, HL.DCR rp; (rp)-1 rp , При этом флаги не модифицируются. Вопросы и задания 2.23.Приведите примеры команд однобайтных и двухбайтных пересылок, загрузок и размещений. 2.24. Опишите последовательность действий МП в каждом машинном цикле при выполнении команды LDA 78A6h. 2.25. Вы можете проверить свои знания функционирования МП. Выберите любую команду и поясните, какие действия выполняются в каждом машинном цикле при ее выполнении. 2.26. Поясните выполнение команды PCHL. 2.27. Опишите по циклам выполнение команды SHLD. 2.28. Определите содержимое аккумулятора: LXI Н, 35E7h; LXI Н, 35E7h; INX H; SHLD 854Ch; SHLD 854Ch; INX H; LDA 854Ch; LDA 854Ch. 2.29. Определите содержимое ячейки памяти 1000h: MVI A, 00h; MOV B, A; STA 1000h. 2.30.Определите содержимое указателя стека SP и ячейки В06Аh: LXI SP B069h; MVI A, 45h; PUSH PSW. 2.5.3. Арифметические команды (модифицируются все признаки в регистре F) S Z AC P CY + + + + +     Арифметические команды выполняют операции сложения, сложения с учетом переноса, вычитания и вычитания с учетом заема. Команда сложения без учета бита переноса: ADD r; (A)+(r) A, где r: A, B, C, D, E, H, L, M. Команда сложения с учетом бита переноса: ADC r; (A)+(r)+(CY) А. Команд вычитания без учета бита заема: SUB r; (A)-(r) А. Команда вычитания с учетом бита заема: SBB r; (A)-(r)-(CY) А. Рассмотрим выполнение команды SBB E (рис.2.13).  Арифметические команды с непосредственной адресацией Сложение с непосредственным операндом: ADI, b2; (A)+b2 A, т.е. содержимое аккумулятора сложить с непосредственным операндом b2. ACI , b2; (A)+b2+(CY) A, т.е. сложение содержимых регистра А, непосредственного операнда b2 и бита переноса CY. Вычитание непосредственного операнда: SUI , b2; (A)-b2 A, т.е. из содержимого аккумулятора вычесть непосредственный операнд b2. SBI , b2; (A)-b2-(CY) A. Команды сравнения CMP r; CPI, b2 выполняют операцию сравнения содержимого аккумулятора с содержимым регистра r или непосредственным операндом b2. При этом содержимое аккумулятора не изменяется, но формируются признаки в регистре F. CMP r; (A)-(r), где r: B, C, D, E, H, L, M, A. CPI , b2; (A)-b2. Команда сложения удвоенной точности: DAD rp; (HL)+(rp) HL, rp: регистровые пары ВС, DE, HL. При выполнении этой команды устанавливается только флаг CY. Команда десятичной коррекции DAA применяется после выполнения операций сложения двоично-десятичных чисел с целью преобразования результата из двоичной формы в двоично-десятичную. При выполнении команды DAA реализуются следующие действия: Если значение младшей тетрады аккумулятора больше кода 1001 или если флаг АС=1, то к содержимому аккумулятора прибавляется число 0110. Если после этого старшая тетрада содержимого аккумулятора имеет код больший 1001 или если флаг CY=1, то к содержимому аккумулятора прибавляется число 0110 0000. 2.5.4. Команды логических операций Признаки результата: S Z AC P CY + + - + 0     Команда побитной конъюнкции: ANA r; (A) & (r) A. Команда побитной дизъюнкции: ORA r; (A) v (r) A. Команда побитного сложения по модулю два: XRA r; (A) (r) A. В этих командах r: B, C, D, E, H, L, M, A. Рассмотрим выполнение команды ANA E (рис.2.14).  Логические команды с непосредственной адресацией (непосредственным операндом b2). ANI , b2; (A) & b2 A. ORI , b2; (A) v b2 A. XRI , b2; (A) b2 A. 2.5.5. Команды сдвига в аккумуляторе на 1 разряд Признаки результата: S Z AC P CY - - - - -     Сдвинуть циклически влево: R CY 7 - A - 0 LC;      Сдвинуть циклически вправо: R CY 7 - A - 0 RC;      Сдвинуть циклически влево через бит CY: R CY 7 - A - 0 AL;       Сдвинуть циклически вправо через бит CY: RAR; CY 7 - A - 0       2.5.6. Команды передачи управления Признаки результата: S Z AC P CY - - - - -     После выборки кода команды из памяти в программном счетчике РС формируется адрес следующей по порядку команды методом автоматического увеличения содержимого РС на единицу. Такой механизм ведения по программе имеет место на линейных ее участках. В разветвляющихся или циклических программах и при использовании подпрограмм имеют место переходы, когда выполняется не следующая по порядку команда, а команда, находящаяся в другом месте программной памяти. Команды, выполняющие такие переходы, называют командами передачи управления. Команды передачи управления осуществляют перезагрузку РС адресом передачи управления, который указывается в кодах этих команд. Команды безусловной передачи управления: PCHL; (H) PCH, Перейти без условия по адресу, находящемуся в HL. (L) PCL. JMP b3b2; b2 PCL, Перейти без условия по адресу b3b2. b3 PCH. Команды передачи управления по условию выполняют передачу управления, если условие выполняется, и не выполняют перехода, если указанное условие не выполняется. Условия определяются по значениям признаков в регистре флагов CY, P, Z, S по их единичному или нулевому значению. Восемь команд передачи управления приведены в табл.2.1. В общем виде все восемь команд передачи управления по условию можно представить в виде одного мнемокода Jcon b3b2 и одного кода команды 11ССС010, где con переменная часть мнемокода, ССС - код условия передачи управления (см. табл.2.1.). Таблица 1.1

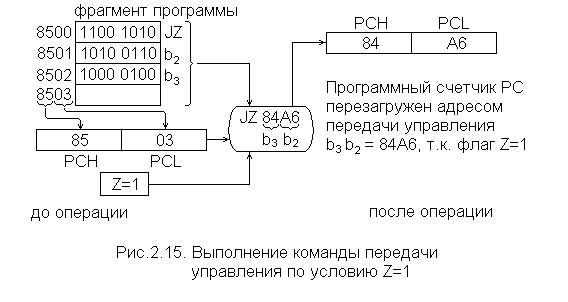

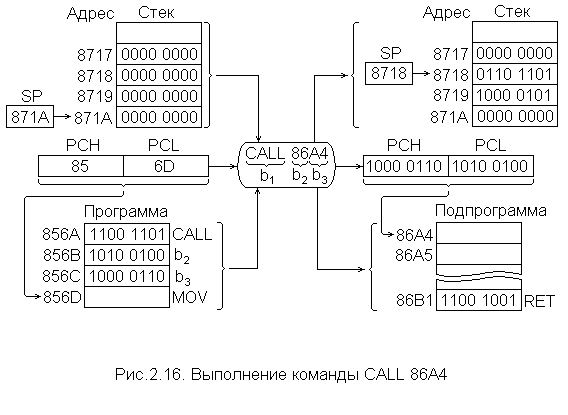

Рассмотрим выполнение МП одной команды передачи управления по условию Z=1 (рис.2.15).   Вызов подпрограмм (команда CALL b3b2). Команда вызова подпрограмм CALL b3b2 состоит из первого байта (код операции) и адреса вызываемой подпрограммы (b3b2). При выполнении этой команды текущее содержимое РС (т.е. адрес команды, следующей за CALL) автоматически запоминается в стеке. Этот адрес (называемый адресом возврата) возвращается в РС командой возврата RET, которой должно завершаться выполнение вызванной подпрограммы. Для запоминания адресов возврата необходима магазинная память (стек), работающая по принципу: первый записанный в нее адрес возврата извлекается последним. При выполнении команды CALL b3b2 выполняются следующие действия: (РС) в стек, т.е. адрес возврата загружается в стек, b3b2 PC, т.е. адрес подпрограммы загружается в РС. Рассмотрим выполнение команды CALL 86 A4 (рис.2.16) При выполнении команды CALL 86A4 реализуются следующие действия: программный счетчик, ведя по программе, считывает из нее команду CALL 86A4. Содержимое РС после считывания последнего байта команды CALL увеличивается на единицу и равно 856Dh. Далее начинается выполнение считанной в МП команды CALL 86A4. Содержимое РС=856D заносится в стек. РС загружается начальным адресом подпрограммы РС=86А4 и МП приступает к выполнению подпрограммы. 1) (PCH) ((SP)-1) (PC) в стек. 2) (PCL) ((SP)-2) 3) (SP-2) SP новое содержимое SP. 4) b2 = A4 PCL начальный адрес подпрограммы загружен в РС. 5) b3 = 86 PCH Команда возврата из подпрограммы RET; ((SP)) PCL. ((SP)+1) PCH. SP: = (SP)+2. Содержимое двух ячеек вершины стека заносится в РС. Таким способом реализуется возврат в “основную” программу. Микропроцессор ВМ80 имеет восемь команд условных вызовов подпрограмм и восемь условных возвратов из подпрограмм. Проверяются единичные и нулевые значения флагов Z, CY, P, S. Если проверяемое в команде вызова или возврата условие выполняется, то осуществляется вызов или возврат. А если условие не выполняется, то выполняется следующая по порядку команда. Команды условного вызова и условного возврата в таблице команд представлены в виде обобщенных мнемокодов команд (см. приложение 1) C con b3b2 и R con. В системе команд МП имеется особая 1-байтная команда вызова, предназначенная для обработки прерываний, введения контрольных точек при отладке программ. Она называется рестартом RST n. В коде команды RST n=11NNN111 три бита NNN формируются подсистемой прерываний или задаются программистом. Имеется восемь команд RST n = 0, 1, 2, 3, 4, 5, 6, 7. Выполнение команды сводится к двум действиям: - текущее содержимое РС загружается в стек; - в РС передается код 0000 0000 00NN N000B. Здесь NNN есть двоичный код n. Таким образом, в зависимости от NNN микропроцессор переходит к одной из восьми ячеек памяти, которые могут быть начальными адресами подпрограмм. 2.5.7. Команды операций ввода-вывода IN , port; (port) A, где port - восьмибитный адрес порта ввода. OUT , port; (A) port, где port - восьмибитный адрес порта вывода. 2.5.8. Специальные команды Инвертирование аккумулятора C  MA; (A) A. MA; (A) A.Установка и инвертирование бита CY. STC; 1 CY. C  MC; (CY) CY. MC; (CY) CY. EI; Разрешение прерываний. DI; Запрещение прерываний. NOP; “Пустая” команда, пропуск 4 тактов. HLT; Команда останова. МП воспринимает запросы прерывания и запросы шин. Полный список команд приведен в приложении 1. Вопросы и задания 2.31.Поясните выполнение команд ADD и ADC, SUB и SBB и какие признаки формируются в регистре F. 2.32.Поясните команду DAD. Обратите внимание, что при ее выполнении формируется только признак переноса CY. 2.33.Перечислите команды, позволяющие сравнивать двоичные коды. 2.34.Поясните отличие команд: INR H; DCR D; INX H; DCX D. 2.35.Занесите в аккумулятор десятичное число 73 в двоично-десятичном коде и определите содержимое аккумулятора и признаки результата после каждой из команд: ORI, 0Fh; ANI, F0h; XRA, A. 2.36.Содержимое какого устройства изменяют команды RLC, RRC, RAL и RAR и поясните выполняемые ими операции. 2.37.Поясните, что общего и различного при выполнении команд: JMP 0000h; CALL 0000h; RST 0. 2.38.Для чего служат команды EI и DI. 2.6. Управление системой В основе устройства управления МП используется цифровой автомат. Примерная схема алгоритма функционирования управляющего автомата в течение рабочего цикла выполнения команды приведена на рис.2.17. Выполнение рабочего цикла команды начинается с опроса триггера прерывания. Если запрос прерывания поступил и прерывания разрешены (командой EI), то автомат формирует машинный цикл обработки прерывания, в котором управление передается подпрограмме обработки прерывания, и она выполняется. При отсутствии прерывания управляющий автомат формирует цикл выборки команды из памяти и формирует адрес следующей команды. Далее управляющий автомат дешифрирует код операции в команде и генерирует соответствующую коду операции серию управляющих сигналов, обеспечивающую выполнение в МП заданной операции. Алгоритм работы управляющего автомата содержит условный оператор ожидания готовности операнда. Наличие такого оператора в алгоритме позволяет МП приспосабливаться для работы с различными видами внешней памяти, имеющей разные времена доступа, а также с медленно действующими устройствами ввода-вывода (УВВ). Наличие в схеме алгоритма устройства управления, оператора ожидания готовности операнда, механизма анализа запросов на прерывание и запросов на захват шин позволяет МП формировать последовательность управляющих сигналов не только на основе команды, но и под воздействием внешних управляющих сигналов Ready, INT, HOLD. Устройство управления МП в зависимости от кода текущей команды, состояния своего управляющего автомата, а также в зависимости от значений сигналов оповещения с шины управления МПС вырабатывает последовательности сигналов, реализующие процедуры системного обмена информацией. В МП управляющий автомат в зависимости от сложности команды выполняет цикл команды за несколько (1-5) внутренних машинных циклов. Один машинный цикл требуется МП для одного обращения к памяти или УВВ. Машинный цикл МП ВМ80 может состоят из 3-5 тактов. Тактирование МП осуществляется от внешнего генератора сигналами F1, F2 (рис.2.18, 2.19). В стандартном машинном цикле может быть от трех до пяти состояний автомата управления. Микропроцессор ВМ80 приступает к анализу запросов на прерывание только после окончания выполнения текущей команды. Из состояния останова МП может быть выведен сигналом прерывания INT или сигналом установки в исходное состояние Reset.   Временная диаграмма, изображенная на рис.2.18, определяет основной цикл команды МП. В первом такте синхронизации Т1 МП выставляет на шине адреса код адреса А0-15 очередной команды. Одновременно на линии синхронизации SYNC появляется единичный сигнал, который идентифицирует информацию на шине данных D0-7 как байт состояния SB процессора и загружает его в регистр системного контроллера К580ВК28 (рис.2.19). Сигнал SYNC также свидетельствует о начале машинного цикла. По окончании сигнала SYNC буферная схема шины данных, расположенная в системном контроллере, переводит шину данных D0-7 в режим ввода, о чем свидетельствует единичный сигнал на линии DBIN шины управления.  В такте Т2 МП осуществляет проверку готовности внешнего устройства (или памяти). Если внешнее устройство не формирует сигнал Готов (высокий уровень), то автомат управления МП переходит в состояние ожидания. В этом состоянии МП будет находиться до тех пор, пока на линии Ready не появится единичный сигнал, который будет свидетельствовать о том, что память или ВУ готовы к обмену. На временных диаграммах (рис.2.18) приведен вариант отсутствия готовности в течение одного такта и МП сформировал один такт ожидания Тож, в котором обнаружил единичный сигнал готовности Ready и перешел к рабочему такту Т3. В такте Т3 МП производит чтение или запись слова в память. Такты Т4 и Т5 отводятся для выполнения операции, заданной кодом операции команды. Выполнение некоторых сложных команд требует неоднократного прохода по циклу состояний автомата управления от Т1 до Т5. Для нормального функционирования МПС недостаточно управляющих сигналов, формируемых МП на собственных выводах. Например, нельзя отличить циклы обращения к памяти от циклов обращения ввода-вывода. Расширение числа управляющих сигналов достигается с помощью специального 8-разрядного кода BS (байта состояния), который МП выдает через шину данных в первом такте Т1 каждого машинного цикла. Байт состояния BS содержит информацию о текущем машинном цикле. Всего 11 типов машинных циклов: Тип Мнемоника Функциональное назначение 1 2 |