Документ Microsoft Word. 2 jkтриггер

Скачать 268.82 Kb. Скачать 268.82 Kb.

|

|

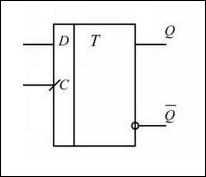

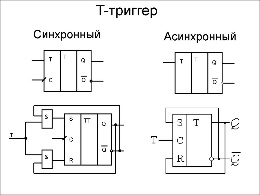

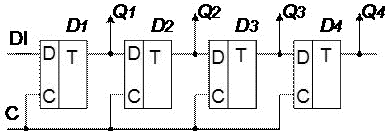

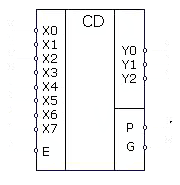

1 билет 1) Классификация ЭВМ. По принципу действия вычислительные машины делятся на три больших класса: аналоговые (АВМ), цифровые (ЦВМ) и гибридные (ГВМ). Критерием деления вычислительных машин на эти три класса является форма представления информации, с которой они работают. 2) JK-триггер — это универсальный триггер, на базе которого можно реализовать любой из рассмотренных ранее триггеров. Таблица истинности jk-триггера практически совпадает с таблицей истинности синхронного RS-триггера. Для того чтобы исключить запрещённое состояние, его схема изменена таким образом, что при подаче двух единиц jk-триггер превращается в счётный T-триггер. Это означает, что при подаче на тактовый вход C импульсов он изменяет своё состояние на противоположное. Таблица истинности jk-триггера приведена в таблице 1. 3) 1 бит из 2 2 билет 1) Способ получения таких моделей сигналов состоит в следующем. Реальный сигнал приближенно представляется суммой некоторых элементарных сигналов, возникающих в последовательные моменты времени. Если теперь устремить к нулю длительность отдельных элементарных сигналов, то, естественно, в пределе будет получено точное представление исходного сигнала. Будем называть этот способ описания сигналов динамическим представлением, подчеркивая этим развивающийся во времени характер процесса. Широкое применение нашли два способа динамического представления, Согласно первому из них в качестве элементарных сигналов используются ступенчатые функции, возникающие через равные промежутки времени 2) В обозначении Д триггера отмечена главная особенность. Буквой «Д» (D лат.) маркируют вход, на который подают информационный сигнал. D-триггер реагирует и на существующие в данный момент значения, и на поступившие ранее. При параллельном коде все разряды кода слова представляются в одном временном такте, фиксируются отдельными элементами и проходят через отдельные линии, каждая из которых служит для представления и передачи только одного разряда. При параллельной передаче информации код слова развертывается в пространстве, в отличие от последовательной, в которой развертывается во времени. В некотором смысле триггер задерживает прохождение поступившего по -входу сигнала до появления активного (единичного) уровня на синхро-входе С (интервалы времени и на рис. 7.4, в). Поэтому название " D - триггер" можно с одной стороны рассматривать как произошедшее от англ. Delay - задержка. Другое назначение D -триггера - сохранить данные (данные по англ. data), поступившие по -входу.  3) 1 бит из 2 4)¬x¬yz ∨ ¬xy¬z ∨ xy¬z ∨ xyz диз (x∨y∨z) ∧ (x∨¬y∨¬z) ∧ (¬x∨y∨z) ∧ (¬x∨y∨¬z) кон 3 билет 1) Технический способ измерения количества информации (или, точнее, информационного объема сообщения) основан на подсчета количества символов, из которых образовано сообщение. 2) T-триггеры. T-триггер — это счетный триггер. У данного триггера имеется только один вход. Принцип работы T-триггера заключается в следующем. После поступления на вход T импульса, состояние триггера меняется на прямо противоположное. Счётным он называется потому, что T триггер как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса  3) 3 бита 4) ¬a¬b¬c ∨ ¬ab¬c ∨ a¬b¬c ∨ a¬bc ∨ ab¬c ∨ abc (a∨b∨¬c) ∧ (a∨¬b∨¬c) 4 билет 1) Функция Хартли или энтропия Хартли является мерой неопределенности, введенной Хартли в 1928 г. Если выбрать образец конечного множества А случайным образом и равномерно, информация, представленная, когда выход известен, энтропия Хартли. Загадано целое число x от 1 до 1000. Нам сообщили, что x делится на 6. Сколько информации нам сообщили? Воспользуемся рассуждением выше. log2 1000 - log2 166 = log2 100\166 = 2.59 битов 2) Регистр — устройство для записи, хранения и считывания n-разрядных двоичных данных и выполнения других операций над ними. Регистр представляет собой упорядоченный набор триггеров, обычно D-триггеров, число которых соответствует числу разрядов в слове. С регистром может быть связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами. Основой построения регистров являются: D-триггеры, RS-триггеры, JK-триггеры. 3) з бита 4) ¬a¬b ∨ ¬ab ∨ a¬b ∨ ab 5 билет 1) Кодирование символов-это процесс присвоения чисел графическим символам, особенно письменным символам человеческого языка, позволяющий хранить, передавать и преобразовывать их с помощью цифровых компьютеров. Униполярный это 1 и 0 , полярный это 1 и -1, биполярный это 1, 0 и -1. 2)Сдвигающий регистр. (Пример 4 разрядного регистра на d-триггере). Регистры сдвига представляют собой цепочку последовательно включённых D-триггеров или RS- и JK-триггеров, включённых в режим D-триггера. Появление импульса на тактовом входе регистра сдвига вызывает перемещение записанной в нём информации на один разряд вправо или влево. Как и другие регистры, регистры сдвига используются для записи, хранения и выдачи информации, но основным их назначением является преобразование последовательного кода в параллельный или параллельного в последовательный. Схема 4-разрядного регистра сдвига приведена на рисунке. Схема работает следующим образом. Благодаря тому, что выход предыдущего разряда соединён со входом «D» последующего, каждый тактовый импульс устанавливает последующий триггер в состояние, в котором до этого находился предыдущий. Так осуществляется сдвиг информации вправо.  3) 0,5 бит 4) ¬x¬y ∨ x¬y ∨ xy x∨¬y 6 билет 1)Кодирование символов-это процесс присвоения чисел графическим символам, особенно письменным символам человеческого языка, позволяющий хранить, передавать и преобразовывать их с помощью цифровых компьютеров. Символ — знак, изображение какого-нибудь предмета или животного, для обозначения качества объекта; условный знак каких-либо понятий, идей, явлений. Разрядность (битность) в информатике — количество разрядов (битов) электронного (в частности, периферийного) устройства или шины, одновременно обрабатываемых этим устройством или передаваемых этой шиной. Значность шифра — количество знаков (цифр или букв), образующих одно шифробозначение А́рность предиката, операции или функции в математике — количество их аргументов или операндов. Последовательный код - это обычный сдвиговый регистр. один выход, на него последовательно подаются биты. параллельный - 8 входов и значения вводятся одновременно. берешь какой-нить порт твоего мк, говоришь это будет мой параллельный ввод. берешь еще один доп вход - синхросигнал. как поступает синхолсигнал - считываешь свой порт и считанное значение отправляешь на USART. вот и весь твой преобразователь. 2) Дешифраторы предназначены для преобразования параллельного двоичного кода в унитарный, т.е. позиционный код. Шифраторы (кодеры) и дешифраторы (декодеры). — это комбинационное устройство, преобразующее десятичные числа в двоичную систему счисления, причём каждому входу может быть поставлено в соответствие десятичное число, а набор выходных логических сигналов соответствует определённому двоичному коду Микросхема К155ИД1 представляет собой высоковольтный дешифратор управления газоразрядными индикаторам. Предназначены для преобразования двоично-десятичного кода в десятичный. Дешифратор состоит из логических ТТЛ-схем и десяти высоковольтных транзисторов. На входы "1-2-4-8" поступают числа от 0 до 9 в двоичном коде, при этом открывается соответствующий выходной транзистор. Номер выбранного выхода соответствует десятичному эквиваленту входного кода. Коды, эквивалентные числам от 10 до 15, дешифратором на выходе не отображаются. 3)0.5 бит 4) ¬x¬y ∨ x¬y ∨ xy x∨¬y 7 билет 1)Разница между ASCII и Unicode заключается в том, что ASCII представляет строчные буквы (az), прописные буквы (AZ), цифры (0-9) и символы, такие как знаки препинания, в то время как Unicode представляет буквы английского, арабского, греческого и т. Д. Математические символы, исторические сценарии, эмодзи, охватывающие широкий спектр символов, чем ASCII. 2)Микросхемы К155ИВ1, КМ155ИВ1 (74148) — приоритетный шифратор, принимающий напряжение низкого уровня на один из восьми параллельных адресных входов I1 — I8. На выходах I1А0 — А2 появляется двоичный код, пропорциональный номеру входа, оказавшегося активным. Приоритет в том случае, если несколько входов получили активные уровни, будет иметь старший среди них по номеру. Высший приоритет у входа I1 — I8.  3) 8=2^i I = 3 бита 8 билет 1)

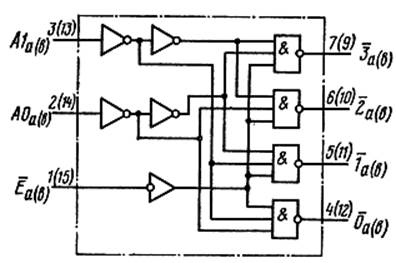

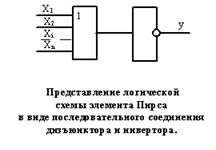

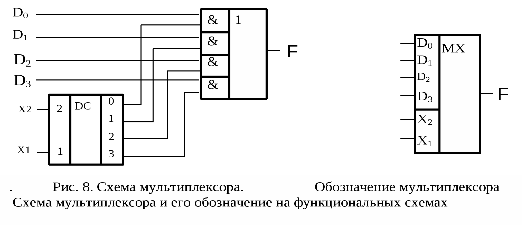

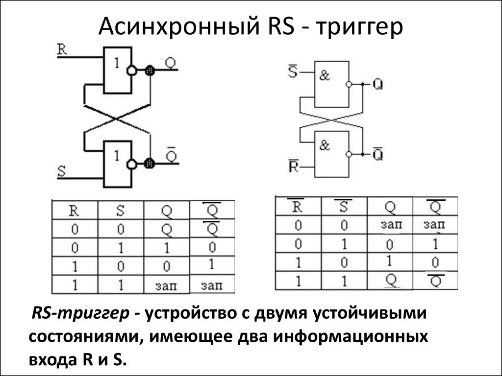

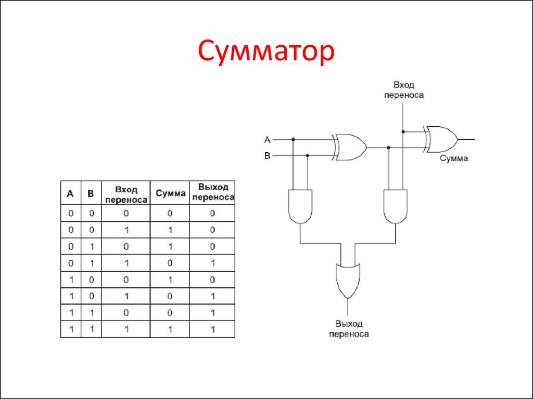

2)  3) 8=2^i I = 3 бита 10 билет 1) Элемент Шеффера (элемент И-НЕ) - реализует операцию логическое умножение с отрицанием. На выходе сигнал "1" имеет место всегда, кроме случая, когда сигналы "1" на всех входах совпадают  Элемент Пирса (элемент ИЛИ-НЕ) - реализует операцию логическое сложение с отрицанием. На выходе сигнал "1" имеет место только в случае, если на всех входах одновременно будет сигнал "0"  2) Дешифра́тор (декодер) (англ. decoder) в цифровой электронике — комбинационная схема, преобразующая n-разрядный двоичный, троичный или k‑ичный код в k‑ичный одноединичный код, k — основание системы счисления. 3) 8=2^i I = 3 бита 11 билет 1) Схематизация происходит при выполнении шести процедур. Действия, входящие в данные процедуры, на схеме обозначены цифрами. 1. Сбор материала для будущей схемы. 2. Выявление значимых частей. Осуществляется разъединение частей, которые обладают некоторой целостностью. 3. Реальное разъединение значимых частей. 4. Выделение значимых частей. Выделяются некоторые критерии значимости, по которым одни части рассматриваются как значимые, а другие — как незначимые. Обучение Python с нуля. Выплатим кэшбек с покупки курса 5. Если схематизатора устраивают выделенные им значимые части, то происходит синтезирование этих частей. 6. Появление конструкции схемы. Соверше́нная дизъюнкти́вная норма́льная фо́рма (СДНФ) — одна из форм представления функции алгебры логики (булевой функции) в виде логического выражения. Представляет собой частный случай ДНФ, удовлетворяющий следующим трём условиям[1]: в ней нет одинаковых слагаемых (элементарных конъюнкций); в каждом слагаемом нет повторяющихся переменных; каждое слагаемое содержит все переменные, от которых зависит булева функция (каждая переменная может входить в слагаемое либо в прямой, либо в инверсной форме). 2)Mультипле́ксор — устройство, имеющее несколько сигнальных входов, один или более управляющих входов и один выход. Мультиплексор позволяет передавать сигнал с одного из входов на выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов.  12 билет 1)RS-триггер - это триггер с раздельной установкой состояний логического нуля и единицы (с раздельным запуском).  2) Сумма́тор — в кибернетике - устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов[1]; устройство, производящее операцию сложения.  Одноразрядные сумматор и полусумматор предназначены для сложения двоичных разрядов. Полусумматор представляет собой комбинационную схему, имеющую два входа и два выхода. 3) 8=2^i I = 3 бита |