Учебное пособие ОИБ. Аннотация дисциплины наименование дисциплины 4 глоссарий 5 Физические основы полупроводниковых приборов

Скачать 1.49 Mb. Скачать 1.49 Mb.

|

|

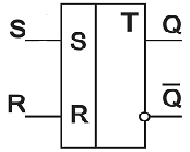

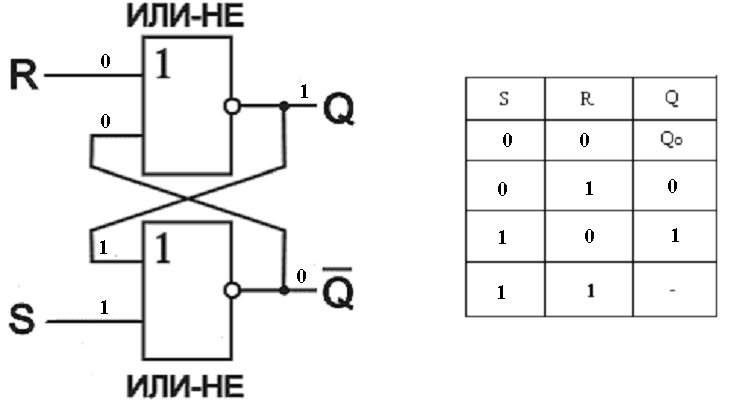

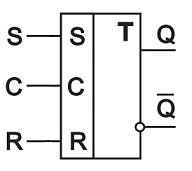

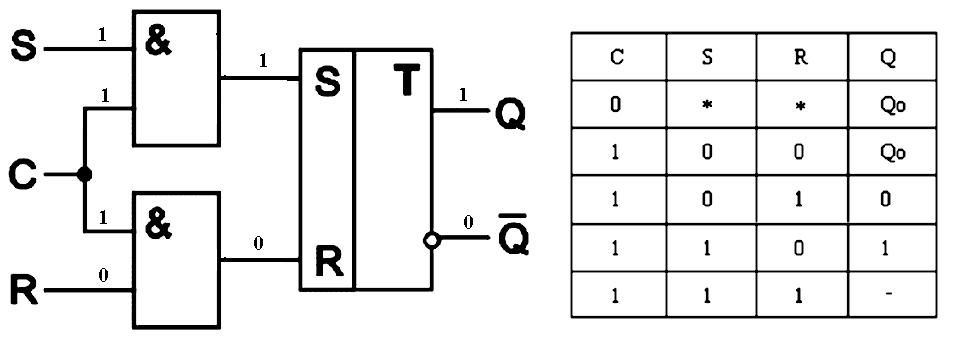

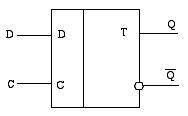

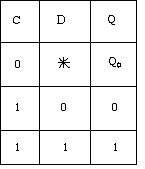

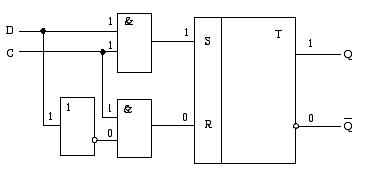

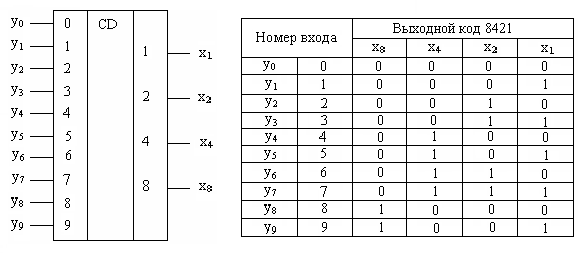

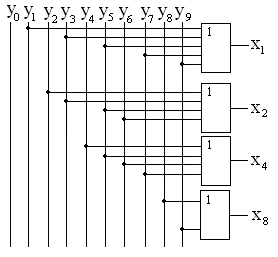

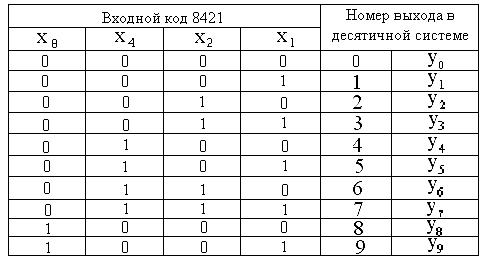

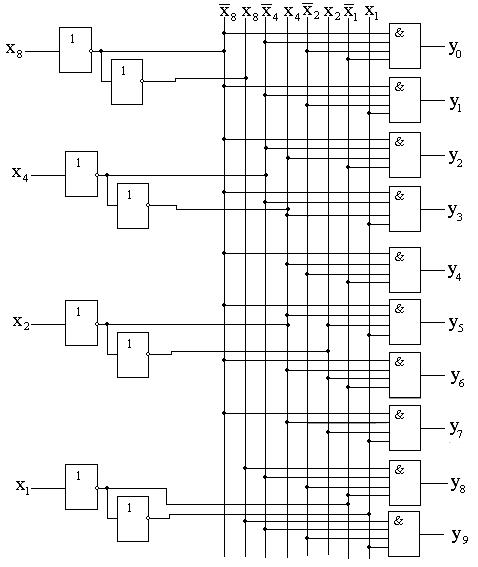

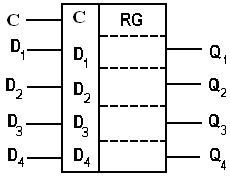

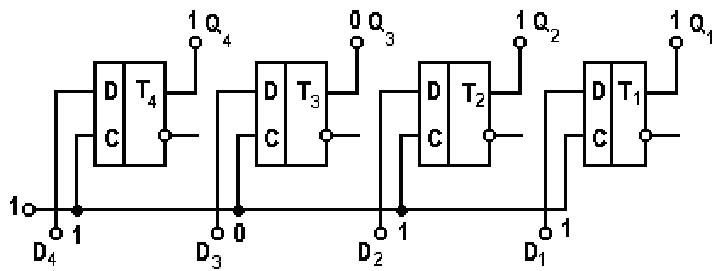

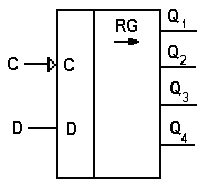

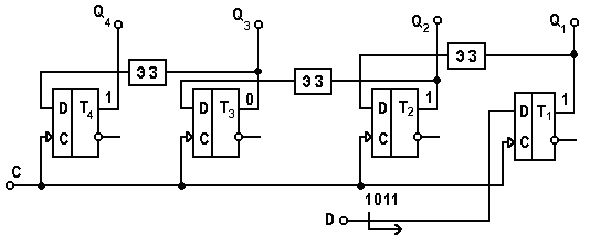

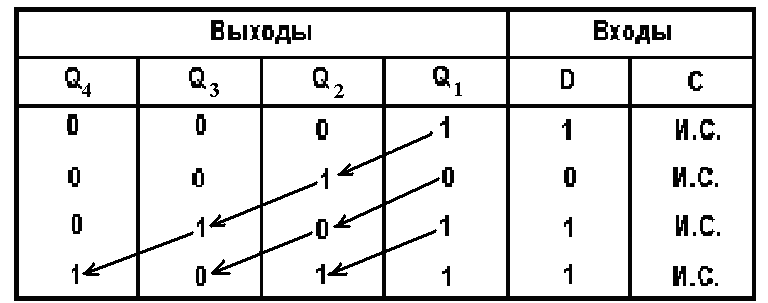

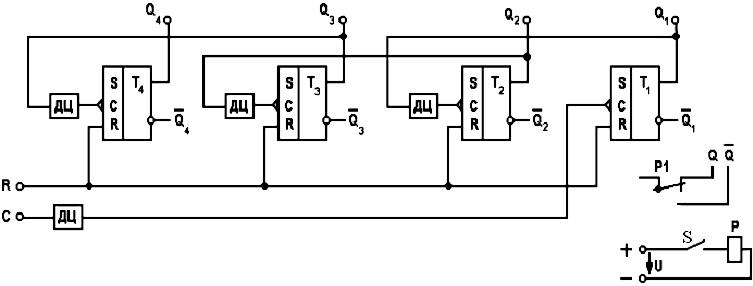

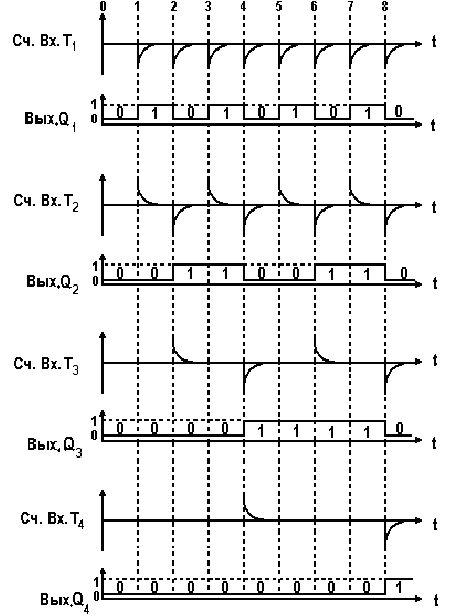

3.3. Асинхронный RS-триггер. Устройство, принцип действия Триггером называется электронное устройство, предназначенное для записи, хранения и считывания двоичной информации. На рис. 3.3 изображено условное обозначение асинхронного RS-триггера, в котором происходит переключение из одного устойчивого состояния в другое под действием определённой совокупности раздельных импульсов напряжения на управляющих входах. Триггер имеет информационные входы R и S , а также информационные выходы: прямой Q и инверсный  . Вход R (от английского слова Reset) является входом установки триггера в состояние лог. 0 , вход S (от английского слова Set) – входом установки триггера в состояние лог.1. . Вход R (от английского слова Reset) является входом установки триггера в состояние лог. 0 , вход S (от английского слова Set) – входом установки триггера в состояние лог.1. Рис. 3.3. Условное обозначение асинхронного RS-триггера На рис. 3.4 приведена структурная логическая схема и таблица истинности RS-триггера, построенного на двух логических элементах ИЛИ-НЕ. Работу RS-триггера иллюстрирует таблица истинности.  Рис. 3.4. Структурная логическая схема и таблица истинности RS-триггера По таблице истинности видно, что RS-триггер работает только в случаях, когда на информационные входы R и S поступают раздельные сигналы лог.0 и лог.1 (или наоборот). При одновременной подаче на информационные входы R и S лог.0, триггер находится в состоянии хранения предшествующей информации на его информационных выходах. Если же на информационные входы R и S одновременно поступают сигналы лог.1, то триггер находится в состоянии запрета. 3.4. Синхронный RS-триггер. Устройство, принцип действия Синхронный RS-триггер снабжён синхронизирующим входом С, который разрешает приём сигналов с информационных входовR и S. Если на синхронизирующий вход С поступает сигнал лог.0, то любые логические сигналы, подаваемые на информационные входыR и S, не влияют на состояние триггера. При подаче на синхронизирующий вход С сигнала лог.1, синхронный RS-триггер работает в режиме асинхронного RS-триггера. На рис. 3.5 изображено условное обозначение синхронного RS-триггера.  Рис. 3.5. Условное обозначение синхронного RS-триггера На рис. 5.6 приведена структурная логическая схема и таблица истинности RS-триггера, построенного на двух логических элементах И, а также на одном асинхронном RS-триггере.  Рис. 3.6. Структурная логическая схема и таблица истинности RS-триггера Из таблицы истинности следует, что при подаче на вход С сигнала лог.0 триггер сохраняет на выходе Q информацию, предшествующую подаче этого сигнала, при любом состоянии информационных входов R и S (0 или 1). При подаче на синхронизирующий вход С сигнала лог.1, синхронный RS-триггер превращается в асинхронный RS-триггер. 3.5. Синхронные D-триггер. Устройство, принцип действия Синхронный D-триггер предназначен для одноступенчатого запоминания информации. На рис. 5.7 показаны условное обозначение и таблица истинности D- триггера. Триггер имеет два входа: информационный D и синхронизирующий C, а также два выхода: прямой Qи инверсный  . . Согласно таблице истинности, при подаче на синхронизирующий входC сигнала лог.0, а на вход D любого из логических сигналов лог. 0 или лог.1, на выходе Q будет сохранён логический сигнал, подаваемый на вход D.   Рис. 3.7. Условное обозначение и таблица истинности D- триггера При подаче на вход C сигнала лог.1, на выходе Q будет сохранён логический сигнал, подаваемый на вход D. На рис. 3.8 изображена логическая схема, реализующая принцип действия синхронного D- триггера. Схема состоит из асинхронного триггера, двух логических элементов И и одного инвертора. На схеме показан один из вариантов работы таблицы истинности.  Рис. 3.8. Логическая схема, реализующая принцип действия синхронного D-триггера 3.6. Шифратор. Устройство, принцип работы Шифратор осуществляет преобразование десятичных чисел в двоичную систему счисления. На рис. 3.9 приведено символическое изображение шифратора, преобразующего десятичные числа 0, 1, 2, … , 9 в выходной код8421и его таблица истинности. Символ CD образован из букв английского слова Coder. Слева показаны 10 входов шифратора, справа – выходы шифратора; цифрами 1,2,4,8 обозначены весовые коэффициенты двоичных четырёх разрядов шифратора. Из таблицы истинности видно, что выходу x1 будет соответствовать лог. 1, если одна из входных переменных y1, y3, y5, y7, y9 будет также иметь лог. 1. Следовательно, можно составить логическую операцию x1=y1  y3 y3 y5 y5 y7 y7 y9. Для остальных выходов можно составить логические операции: x2=y2 y9. Для остальных выходов можно составить логические операции: x2=y2 y3 y3 y6 y6 y7, x4=y4 y7, x4=y4 y5 y5 y6 y6 y7, x8=y8 y7, x8=y8 y9. y9.  Рис. 3.9. Символическое изображение шифратораи его таблица истинности Используя полученные логические операции, можно реализовать логическую схему шифратора, построенную на логических элементах ИЛИ, приведённую на рис. 3.10. Шифраторы используются в устройствах ввода информации в цифровые системы с клавиатуры.  Рис. 3.10. Логическая схема шифратора 3.7. Дешифратор. Устройство, принцип работы Дешифраторы используются для преобразования двоичных чисел в десятичные числа и находят применение в печатающих устройствах. В таких устройствах двоичное число, поступая на вход дешифратора, вызывает появление десятичного числа только на одном определённом его выходе. На рис. 3.11 приведено символическое изображение дешифратора и его таблица истинности. Символ DC образован от английского слова Decoder. Слева показаны входы, на которых отмечены весовые коэффициенты двоичного кода, справа выходы десятичных чисел. На каждом входе образуется десятичное число при определенных комбинациях входного кода.   Рис. 3.11. Символическое изображение дешифратора и его таблица истинности Рассмотрим построение дешифратора по его таблице истинности. Значения входных переменных определяются логическими выражениями: y0 =  8^ 8^ 4^ 4^  2^ 2^ 1, 1,y1 =  8^ 8^ 4^ 4^ 2^ x 1, 2^ x 1,y2 =  8^ 8^ 4^ x2 ^ 4^ x2 ^ 1, 1,y3 =  8 ^ 8 ^ 4^ x2 ^ x1, 4^ x2 ^ x1,y4 =  8 ^x4 ^ 8 ^x4 ^ 2 ^ 2 ^ 1, (3.1) 1, (3.1)y5 =  8 ^ x4^ 8 ^ x4^ 2 ^ x1, 2 ^ x1,y6 =  8 ^ x4^ x2 ^ 8 ^ x4^ x2 ^ 1, 1,y7 =  8 ^ x4^ x2 ^ x1, 8 ^ x4^ x2 ^ x1,y8 = x8 ^  4^ 4^ 2^ 2^ 1, 1,y9 = x 8 ^  4 ^ 4 ^  2^ x 1. 2^ x 1. Используя логические выражения (9.1), построим логическую схему дешифратора. На рис. 3.12 показана логическая схема дешифратора, построенного на логических элементах И и инверторах НЕ.  Рис. 3.12. Логическая схема дешифратора 3.8. Регистры. Устройство, принцип работы Регистрами называют логические устройства, предназначенные для запоминания и хранения цифровых кодов. Построение регистров выполняют на триггерах. Операцию передачи цифрового кода в регистр и из регистра можно осуществлять последовательно и параллельно. На рис. 3.13 изображено условное обозначение и схема четырёхразрядного регистра параллельного действия, построенного на синхронных D – триггерах. Регистр имеет четыре входа D1÷D4 информационных и один синхронизирующий вход С. B исходное нулевое состояние логических сигналов на всех выходах Q1 ÷ Q4 , регистр устанавливается при подаче на синхронизирующий вход С сигнала лог.1 и на все информационные входы D сигнала лог “0”. Запись двоичного числа производится при одновременной подаче на информационные входы D1÷D4 кода числа.   Рис. 3.13. Условное обозначение и схема четырёхразрядного регистра параллельного действия Триггеры, на информационные входы которых подаются сигналы лог. 1 , переводятся в состояния 1, остальные останутся в состоянии 0. Записанное число считывается с выходов Q1÷Q4. Для запоминания числа и сдвига влево используется схемы сдвигающего регистра. На рис. 3.14 приведено условное обозначение и логическая схема сдвигающего регистра. Регистры такого типа используют в качестве преобразователей последовательного кода в параллельный код. Регистр имеет два входа: на вход С поступают динамические импульсы сдвига, являющимися положительными импульсами, изменяющимися во времени; вход D является информационным входом. При записи числа в сдвигающий регистр цифровой двоичный код подается на информационный вход D триггера Т1, начинается со старшего разряда. При этом положительные импульсы сдвига поступают на счётные входы С триггеров. Работу регистра рассмотрим на примере записи числа 1011. С приходом импульса сдвига на вход С и подаче на вход D единицы старшего разряда числа, триггер Т1 переводится в состояние 1 (Q1). В регистре используются элементы задержки ЭЗ, которые осуществляют задержку во времени перемещения сигнала с одного триггера на другой. При подаче очередного импульса сдвига на вход С и подаче на вход D второго разряда (нуля) числа, на выходе Q1 появится 0 , а 1 из триггера Т1 через элемент ЭЗ переместится в триггер Т2. С приходом очередного импульса сдвига на вход С и подаче на вход D третьего разряда (единицы) числа, триггер Т1 установится в 1 и т.д. Путём последовательной подачи кодов чисел на вход Dи импульсов сдвига на вход С, число записывается в регистр.   Рис. 3.14. Условное обозначение и логическая схема сдвигающего регистра Считывание чисел осуществляется параллельным кодом с выходов Q1 ÷ Q4 или последовательным кодом с выхода Q4 путем последовательной подачи импульсов сдвига. На рис. 5.15 приведена таблица истинности сдвигающего регистра.  Рис. 3.15. Таблица истинности сдвигающего регистра 3.9. Счётчики импульсов. Устройство, принцип работы Счётчиком называется логическое устройство, предназначенное для подсчёта числа входных сигналов. На рис. 3.16 приведена упрощённая схема четырёхразрядного двоичного суммирующего счётчика импульсов. Счётчик состоит из четырёх синхронных RS - триггеров со счётным входом С и дифференцирующих цепочек ДЦ, предназначенных для отрицательного дифференцирования прямоугольных импульсов, поступаемых на счётные входы триггеров.  Рис. 3.16. Упрощённая схема четырёхразрядного двоичного суммирующего счётчика импульсов Прямые выходы каждого триггера подсоединены через дифференцирующие цепочки ДЦ к счётным входам С каждого последующего триггера. Импульсы, подлежащие счёту, подаются на счётный вход триггера Т1. Записанные в счётчике числа, снимаются с выходов триггеров Q1÷Q4. Принцип действия счётчика импульсов поясняется временными диаграммами, приведёнными на рис. 3.17. Начальные состояния триггеров счётчика нулевые (выходы Q1÷Q4). На счётный вход триггера Т1 поступают отрицательные дифференцирующие импульсы. При подаче на счётный вход триггера Т1 счётчика первого отрицательного импульса, триггер Т1 переходит в состояние 1 или положительно перепад напряжения (выход Q1). В результате дифференцирования этого перепада на счётном входе триггера Т2 появляется положительный импульс, который не переводит Т2 в состояние 1 (выход Q2), так как, применяемые в счётчике триггеры, переводятся из одного устойчивого состояния в другое только отрицательными импульсами. Второй отрицательный импульс, поданный на вход триггера Т1, переводит его в 0 и на выходе дифференциальной цепочки формируется импульс отрицательной полярности. Этот импульс переводит триггер Т2 в состояние 1 и т.д.  Рис. 3.17. Временные диаграммы, поясняющие принцип работы счётчика импульсов Из временной диаграммы видно, что триггер Т1 переходит из одного состояния в другое с приходом каждого импульса, подлежащего счёту, триггер Т2 – через каждые два импульса, триггер Т3 – через каждые четыре импульса и триггер Т4 – через восемь импульсов. Таким образом, коэффициент пересчёта счётчика КП = 2(n-1), где n– количество разрядов счётчика. В исходное нулевое состояние триггеры счётчика устанавливаются единичным импульсом сброса, подаваемым на нулевые R– входы триггеров. По назначению счётчики делятся на суммирующие, вычитающие и реверсные. В суммирующих счётчиках производится сложение, поступающих на вход импульсов с тем числом, которое хранилось в счётчике. В вычитающих счётчиках производят вычитание поступивших на вход импульсов из начального числа. Реверсивные счетчики могут производить сложение и вычитание, в зависимости от управляющего сигнала переключающего счетчик в режим сложения или вычитания. На рис. 3.16 показана упрощённая схема переключения контакта Р1 реле Р из положения суммирования импульсов в положение вычитания импульсов при замыкании контакта S. При этом в качестве обратных связей используются не прямые выходы Q триггеров, а обратные выходы  триггеров. триггеров.Контрольные вопросы по разделу 3 Основные виды логических устройств. Основные логические функции и способы их задания. Основные логические элементы и их обозначение на схемах. Асинхронный RS-триггер. Устройство, таблица истинности и принцип действия. Синхронный RS-триггер. Устройство, таблица истинности и принцип действия. Синхронные D-триггер. Устройство, таблица истинности и принцип действия. Шифратор. Устройство, область применения и принцип работы. Дешифратор. Устройство, область применения и принцип работы. Регистры. Устройство, условное обозначение и основные режимы работы. Счётчики импульсов. Устройство, основные разновидности и принцип действия двоичного суммирующего счетчика. ЗАКЛЮЧЕНИЕ Электронное учебное пособие по дисциплине «Электроника и схемотехника» разработано в соответствии с федеральным государственным образовательным стандартом по уровню бакалавриата. В электронном учебном пособии содержится материал основных разделов базового курса электроники и схемотехники, который необходим студентам в дальнейшем при изучении специальных дисциплин, связанных с информационной безопасностью автоматизированных систем, технологических процессов, а также построении защищенных информационных систем. Рассмотрены вопросы анализа и синтеза электронных устройств и схемотехнических решений для обеспечения информационной безопасности на объектах водного транспорта. Содержание данного электронного учебного пособия соответствует рабочей программе дисциплины и основано на материалах отечественных и зарубежных исследований, включая современные публикации. Шаблон представления тестовых заданий для проведения промежуточного тестирования Шаблон представления тестовых заданий для проведения промежуточного тестирования указывается один раз в конце раздела. Тестирование Вопрос 1 Текст вопроса 1 вариант ответа вопроса 1 (правильный ответ) вариант ответа вопроса 1 • вариант ответа вопроса 1 Вопрос 2 Текст вопроса 2 вариант ответа вопроса 2 (правильный ответ) вариант ответа вопроса 2 • • вариант ответа вопроса 2 В тесте рекомендуется представлять не более 7-15 вопросов с указанием правильных ответов. Структура представления материала для каждого раздела идентична. Используются: шаблон представления лекционного материала: шаблон представления контрольных вопросов: шаблон представления тестовых заданий для проведения промежуточного тестирования. БИБЛИОГРАФИЧЕСКИЙ СПИСОК Иванов Е.Н. Электротехника и электроника: Конспект лекций / Е.Н. Иванов. СПб: ФГБОУ ВПО «ГУМРФ имени адмирала С.О. Макарова», 2014.− 162 с. Миленина, С. А. Электротехника, электроника и схемотехника : учебник и практикум для СПО / С. А. Миленина ; под ред. Н. К. Миленина. — М.: Издательство Юрайт, 2015. − 399 с. Марченко А. Л. Основы электроники. Учебное пособие для вузов / А. Л. Марченко. − М.: ДМК Пресс, 2008. − 296 с. |