Цифровые устройства. Что такое цифровые микросхемы. Виды цифровых микросхем

Скачать 2.25 Mb. Скачать 2.25 Mb.

|

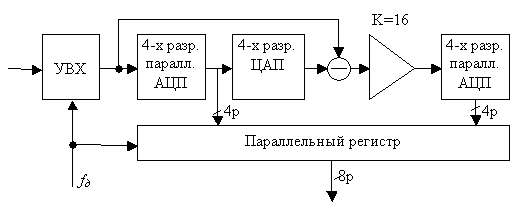

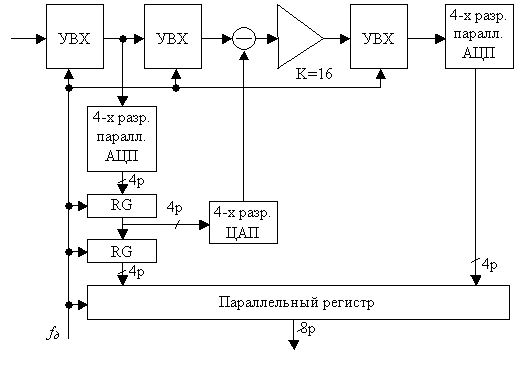

Глава 6Последовательно-параллельные АЦПСледующим видом аналого-цифровых преобразователей, занимающим промежуточное место между скоростными параллельными АЦП и наиболее распространенными АЦП последовательного приближения, являются последовательно-параллельные АЦП. Рассмотрим работу последовательно-параллельного АЦП на примере восьмиразрядного АЦП. Структурная схема этого АЦП приведена на рисунке 6.1.  Рисунок 6.1. Структурная схема восьмиразрядного последовательно-параллельного АЦП В схеме восьмиразрядного последовательно-параллельного АЦП используются два параллельных четырехразрядных АЦП. Второй аналого-цифровой преобразователь оцифровывает ошибку квантования, выделяемую при помощи цифро-аналогового преобразователя и аналогового вычитателя. Если бы мы преобразовывали входной сигнал в цифровую форму без погрешности, то на выходе АЦП (а затем и на выходе цифро-аналогового преобразователя) мы бы получили точную копию входного сигнала, однако это не так. Поэтому на выходе аналогового вычитателя формируется сигнал ошибки преобразования. Для того чтобы в схеме можно было бы использовать одинаковые АЦП, сигнал ошибки преобразования первого аналого-цифрового преобразователя усиливается в 16 раз. В результате уровень сигнала на входе второго АЦП равен уровню сигнала на входе первого АЦП, а значит можно использовать схему, полностью идентичную первому аналого-цифровому преобразователю. Следует отметить, что вычитатели обычно выполняют с использованием операционных усилителей, поэтому обычно в составе последовательно-параллельного преобразователя используется усиливающий вычитатель. Что же мы выиграли в результате усложнения схемы? Так как разрядность параллельных преобразователей снижена вдвое, то для их реализации в случае, приведенном на рисунке 1, потребуются только 2 * 15 = 30 компараторов. Для реализации восьмиразрядного АЦП, как это уже упоминалось в предыдущей главе, нам бы потребовалось 255 компараторов. То есть выигрыш по сложности реализации схемы составляет почти в десять раз! Теперь давайте оценим, во сколько же раз мы проиграли в быстродействии? Прежде чем мы сможем сформировать на выходе восьмиразрядный двоичный код, необходимо чтобы сигнал был преобразован в цифровую форму первым АЦП, снова преобразован в аналоговую форму цифро-аналоговым преобразователем. Затем должен быть сформирован и усилен сигнал ошибки, и этот сигнал должен быть снова оцифрован. В результате описанных действий время преобразования входного аналогового сигнала возрастает, по крайней мере, в четыре раза. Обратите внимание — время преобразования, а не тактовая частота! Как мы определили в предыдущей главе, время преобразования в параллельном АЦП в несколько раз больше периода тактовой частоты (частоты дискретизации аналогового сигнала). Все это время сигнал на входе преобразователя не должен меняться. Это означает, что в составе последовательно-параллельного АЦП должно находиться устройство выборки и хранения. Тем не менее, как и в случае с параллельным аналого-цифровым преобразователем, быстродействие всей схемы в целом может быть увеличено за счет применения конвейерной обработки. Достаточно разбить алгоритм преобразования на несколько этапов, которые могут выполняться одновременно. В цифровой части преобразователя разбиение на этапы производится при помощи параллельных регистров. В аналоговой части для этой цели служат устройства выборки и хранения. И на регистры и на устройства выборки и хранения подается тактовая частота аналого-цифрового преобразователя. Эта частота совпадает с частотой дискретизации входного аналогового сигнала. Структурная схема восьмиразрядного последовательно-параллельного преобразователя, использующая принцип конвейерного преобразования сигнала, приведена на рисунке 6.2.  Рисунок 6.2. Структурная схема конвейерного восьмиразрядного последовательно-параллельного АЦП В этой схеме, пока осуществляется преобразование в цифровую форму сигнала ошибки, формируется сигнал ошибки следующего отсчета сигнала. Пока формируется сигнал ошибки следующего отсчета сигнала, осуществляется формирование старших четырех разрядов выходного кода. Единственная трудность заключается в том, что необходимо совместить сформированные старшие и младшие разряды во времени. Это осуществляется за счет задержки старших разрядов в цифровой линии задержки, собранной на параллельных регистрах. В приведенной на рисунке 6.2 схеме выходной отсчет входного сигнала появится только через три тактовых импульса. Все последующие отсчеты входного аналогового сигнала будут появляться с каждым очередным тактовым импульсом. Итак, подведем итоги. Последовательно-параллельный АЦП способен осуществлять преобразование сигнала с большей разрядностью по сравнению с параллельным АЦП. Однако он обладает меньшим быстродействием, приблизительно равным времени задержки параллельного АЦП. Последовательно-параллельные АЦП способны формировать цифровой поток данных со скоростью несколько сотен миллионов отсчетов в секунду. |