ЛекцииМП. Эвм получили широкое распространение, начиная с 50х годов. Прежде это были очень большие и дорогие устройства, используемые лишь в государственных учреждениях и крупных фирмах

Скачать 0.63 Mb. Скачать 0.63 Mb.

|

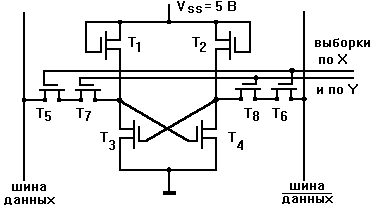

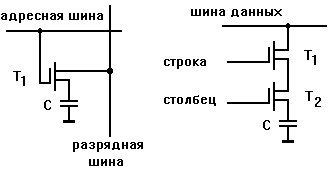

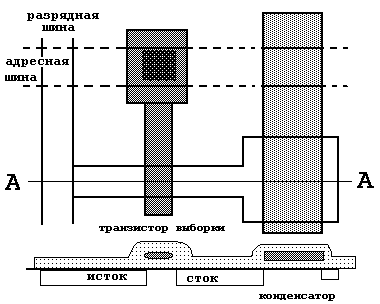

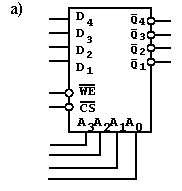

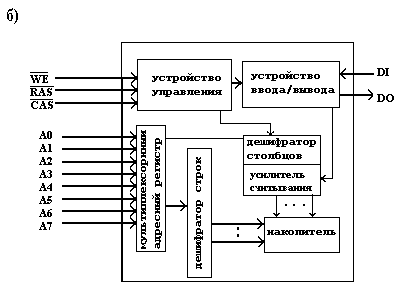

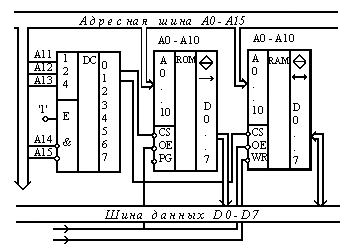

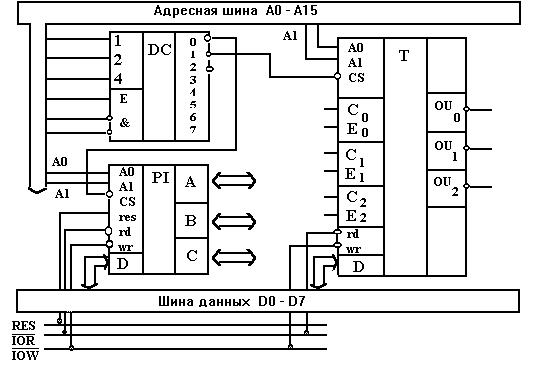

Статические запоминающие устройстваЭлементарной ячейкой статического ОЗУ с произвольной выборкой является триггер на транзисторах Т1-Т4 (рис. 3.7) с ключами Т5-Т8 для доступа к шине данных. Причем Т1-Т2 - это нагрузки, а Т3-Т4 - нормально закрытые элементы.  Рис. 4.7. Ячейка статического ОЗУ. Сопротивление элементов Т1-Т2 легко регулируется в процессе изготовления транзистора путем подгонки порогового напряжения при легировании поликремниевого затвора методом ионной имплантации. Количество транзисторов (6 или 8) на ячейку зависит от логической организации памяти микропроцессорной системы. Динамические запоминающие устройстваВ отличие от статических ЗУ, которые хранят информацию пока включено питание, в динамических ЗУ необходима постоянная регенерация информации, однако при этом для хранения одного бита в ДОЗУ нужны всего 1-2 транзистора и накопительный конденсатор (рис. 4.8). Такие схемы более компактны.  Рис. 4.8. Запоминающая ячейка динамического ОЗУ. Естественно, что в микросхеме динамического ОЗУ есть один или несколько тактовых генераторов и логическая схема для восстановления информационного заряда, стекающего с конденсатора. Это несколько "утяжеляет" конструкцию ИМС. Чаще всего и СОЗУ, и ДОЗУ выполнены в виде ЗУ с произвольной выборкой, которые имеют ряд преимуществ перед ЗУ с последовательным доступом.  Рис. 4.9. Конструкция ячейки ДОЗУ (см. рис. 4.8, слева). Снизу представлен разрез схемы по линии А-А. Запоминающие устройства с произвольной выборкойНа рис. 4.10 показано обозначение ЗУПВ и его внутренняя структура.   Рис. 4.10. ОЗУ с произвольной выборкой. а) ОЗУ 16x4 бит; б) ОЗУ 64Кx1 (КР565РУ5) Здесь: D1-Dn (справа DI) - информационные входы; Q1 - Qn (справа DO) - инверсные выходы; A1- An - адресные входы; WE# - запись/чтение; CS# (Chip Select) - выбор кристалла; CAS# (Column Address Strobe) и RAS# (Row Address Strobe) - сигнал выборки столбца и строки соответственно. Представленное здесь ЗУПВ - это ДОЗУ с организацией хранения информации 65536 бит на 1 разряд. Накопительная матрица с однотранзисторными запоминающими элементами имеет размер 512x128. Для уменьшения количества задействованных ножек у ИМС (16-входовый DIP корпус) применена мультипликация адреса, что видно на рисунке по наличию отдельных дешифраторов строк и столбцов. Устройство управления включает два генератора тактовых сигналов и генератор сигналов записи и обеспечивает 4 режима работы: записи, считывания, регенерации и мультипликации адреса. Время регенерации - 2 мс. Для сравнения на рис. 4.11 показана конструкция ППЗУ с ультрафиолетовым (УФ) стиранием на МНОП-структурах с организацией представления информации 2Кx8 (16384 бита). Микросхемы памяти в составе микропроцессорной системы Рис. 4.11. Микросхемы ОЗУ (К573РУ9) и ППЗУ (К573РФ5) в составе микропроцессорной системы. На рис. 4.11 представлено взаимодействие К573РФ2(5) и К573РУ9, имеющих одинаковую организацию 2Кx8, с системной магистралью. Байт данных с шины данных (линии D0-D7) считывается (или записывается) по адресу, выставленному на шине адреса (линии A0-A10). Естественно, число адресуемых ячеек составляет 211=800h=2048. Микросхема-дешифратор К555ИД7 посредством сигнала CS# (выбор кристалла) позволяет выбрать положение ИМС ЗУ в адресном пространстве. Для данного случая это адреса 0000h-07FFh для ПЗУ(ROM) и 0800h-0FFFh для ОЗУ(RAM). Низкий уровень сигналов управления MEMW# и MEMR# активизирует процесс записи и чтения, соответственно. Напомним, что запись информации в данную ИМС ППЗУ возможен только вне микропроцессорной системы в специальном программаторе после УФ стирания путем подачи достаточно высокого напряжения на вход PG. Аналогично можно проследить и взаимодействие программируемых ИМС параллельного интерфейса и программируемого таймера, служащих для взаимодействия МП с внешними устройствами. На рис. 4.12 они обозначены как PI и T. Регистры этих микросхем также доступны пользователю для чтения/записи, как и ячейки основной памяти. Однако их активизируют другие сигналы управления IOR# и IOW# (запись в порты ввода/вывода). Микросхема КР580ВВ55А (аналог Intel 8255А) позволяет переключать шину данных компьютера на один из трех 8-битных портов (регистров) A, B или C. Направление передачи данных и режим работы (0-2) определяются программным способом. Чаще других используется режим 0: простой ввод-вывод. Состояние адресных линий А0 и А1 позволяет выбрать для обмена информацией регистры A, B, C или регистр управления. Режим работы параллельного интерфейса КР580ВВ55А определяется байтом, записанным в регистр управления. При работе на вывод порты A, B, C действуют как регистры, т.е. сохраняют информацию до следующей записи; при работе на ввод информация теряется. Порт С, в отличие от портов A и B, разбит на полубайты и может программироваться раздельно, т.е. мы имеем группы A и B. В дополнение к основным режимам работы микросхема КР580ВВ55А обеспечивает возможность программной независимой установки/сброса любого бита (порт С), в этом случае старший бит в регистре управления должен быть 0.  Рис. 4.12. Пример взаимодействия программируемых ИМС параллельного порта (PI) КР580ВВ55А и таймера (T) КР580ВИ53 с системной магистралью компьютера; DC - дешифратор К555ИД7. Интегральная схема КР580ВИ53 создана по n-МОП технологии, Uпит=+5 В, U1>2.4 В, U0<0.45 В, P=1 Вт, fтакт <2 МГц, 24 вывода, максимальное значение счета: 216 - в двоичном коде и 104 - в двоично-десятичном. Программируемый таймер КР580ВИ53 реализован в виде трех независимых 16-разрядных вычитающих счетчиков (каналов) с общей схемой управления. Каждый канал может работать в шести режимах. Программирование режимов работы каналов осуществляется индивидуально и в произвольном порядке путем ввода управляющих слов в регистры режимов каналов, а в счетчики - некоторого числа байт. На рис. 4.12 можно видеть, что таймер обменивается информацией с 8-битной шиной данных микропроцессорной системы через вход D, а также он связан с адресной шиной двумя линиями А0-А1, обеспечивающими выбор одного из четырех регистров (3 канала и управляющее слово). Сигналы шины управления IOR# и IOW# (чтение/запись из/во внешнее устройство) определяют направление потока информации от процессора к таймеру и наоборот. С0, С1, С2 - тактовые входы, сигналы на Е0, Е1, Е2 - разрешают или запрещают работу соответствующего канала, OU0, OU1, OU2 - выходы. |