Лабораторные. АТПб(до)з-20-1_лабораторные_Герасимов_В.О. Герасимов Виктор Олегович Проверил преподаватель Сватов В. Ф. Тюмень Тиу 2023 лабораторная работа 1 Синтез и исследование

Скачать 1.39 Mb. Скачать 1.39 Mb.

|

|

Министерство образования и науки Российской Федерации ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ОБРАЗОВАНИЯ «Тюменский индустриальный университет» Институт геологии и нефтегазодобычи Кафедра кибернетических систем Лабораторные работы по дисциплине «Электроника и цифровая схемотехника» Вариант № 4 Выполнил: ст.гр. АТПбз-20-1 Герасимов Виктор Олегович Проверил: преподаватель Сватов В.Ф. Тюмень Тиу 2023 Лабораторная работа № 1 «Синтез и исследование логических схем цифровых устройств» 1. Цель работы Ознакомиться с принципами реализации логических функций с помощью логических элементов, провести исследование логических схем, приобрести навыки схемотехнического моделирования на персональных компьютерах. 2. Порядок выполнения работы Задание 1. По заданной функции, которая описывает роботу комбинационного устройства, необходимо синтезировать логическую схему минимальной сложности из логических элементов заданного базиса. Выбор варианта задания осуществляется из табл. 1 по номеру рабочего места. Таблица 1

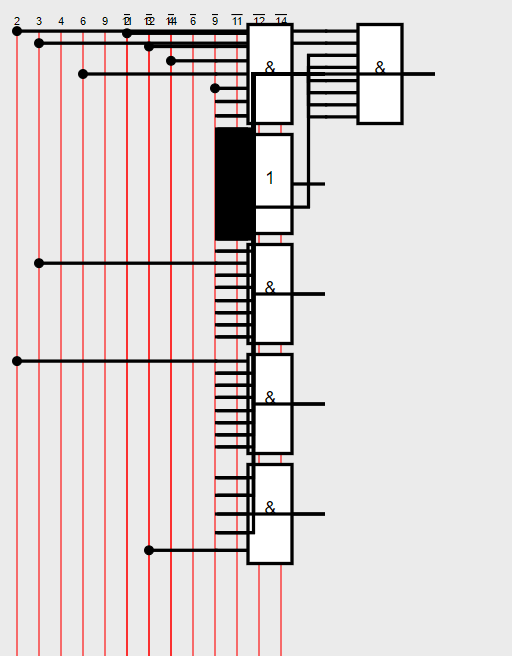

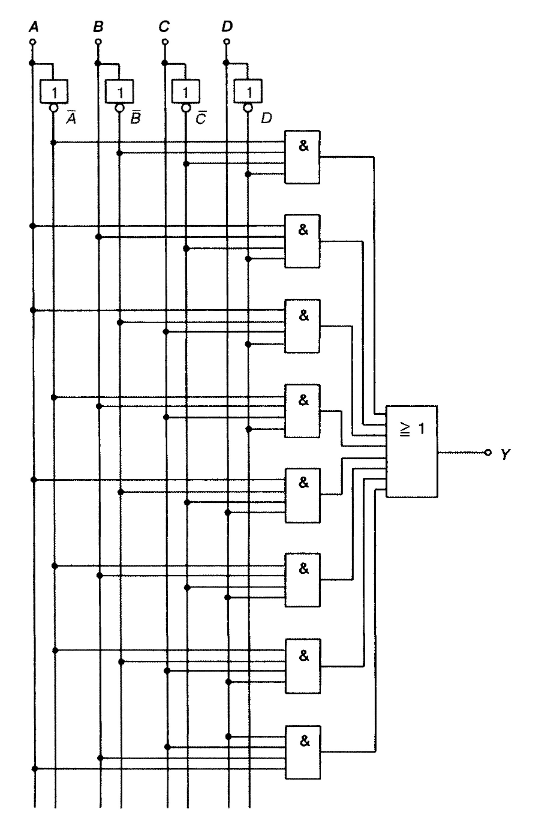

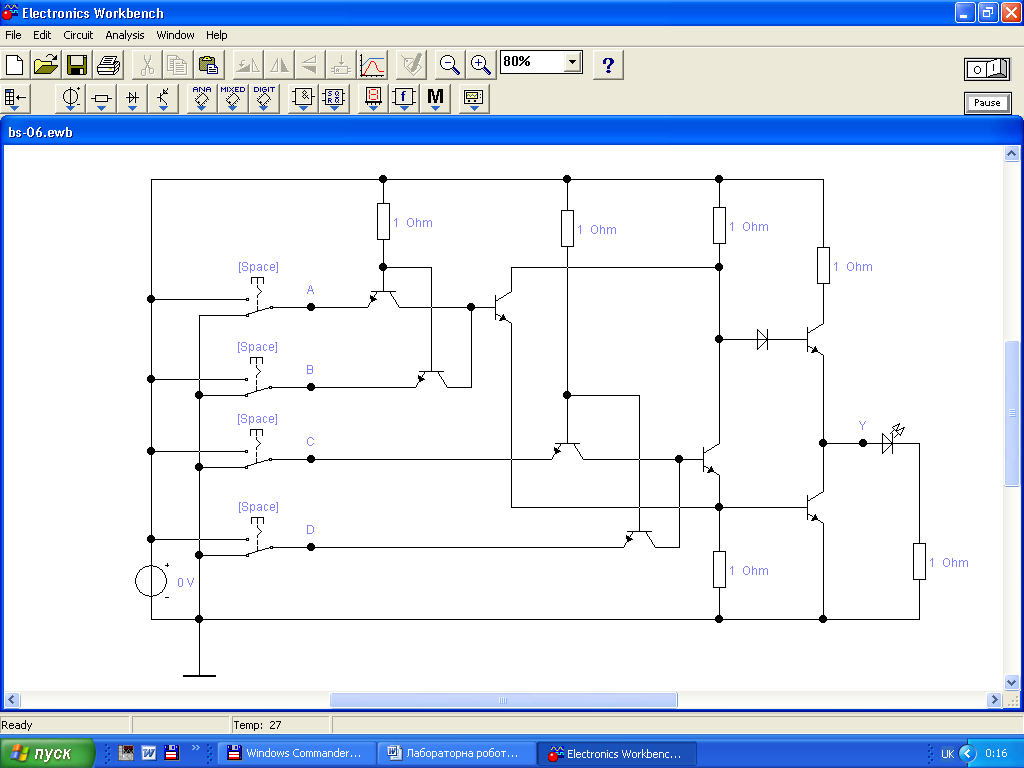

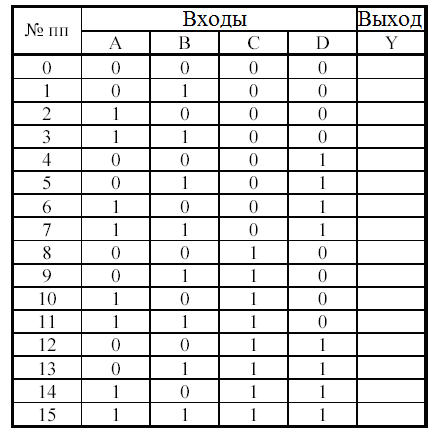

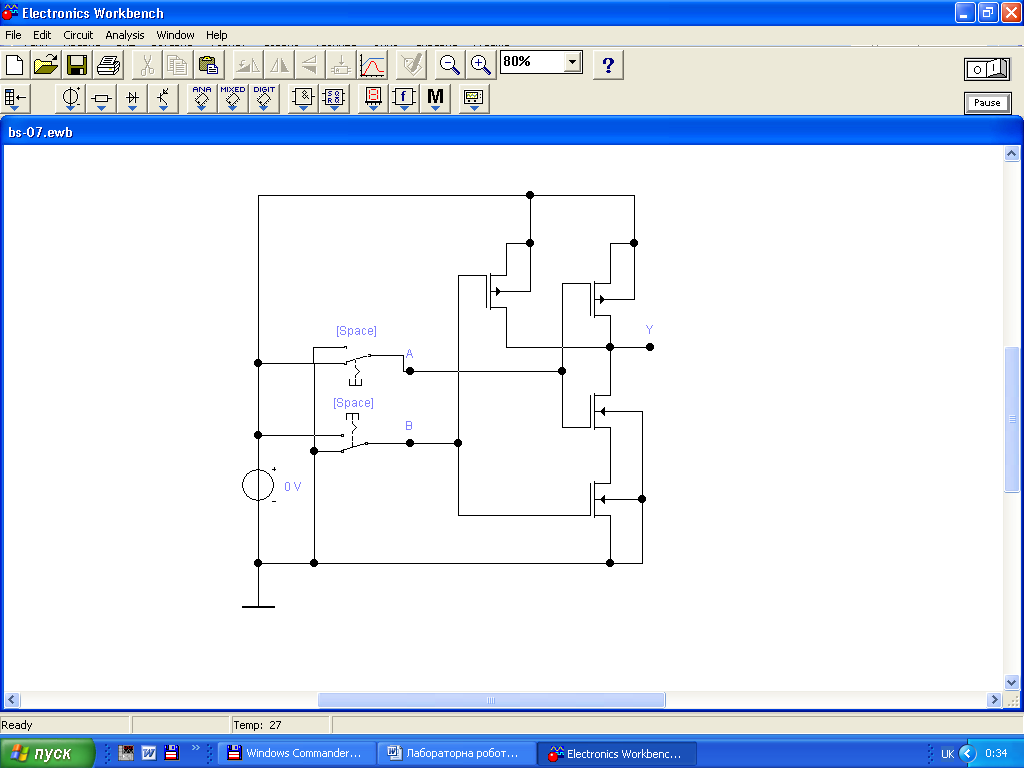

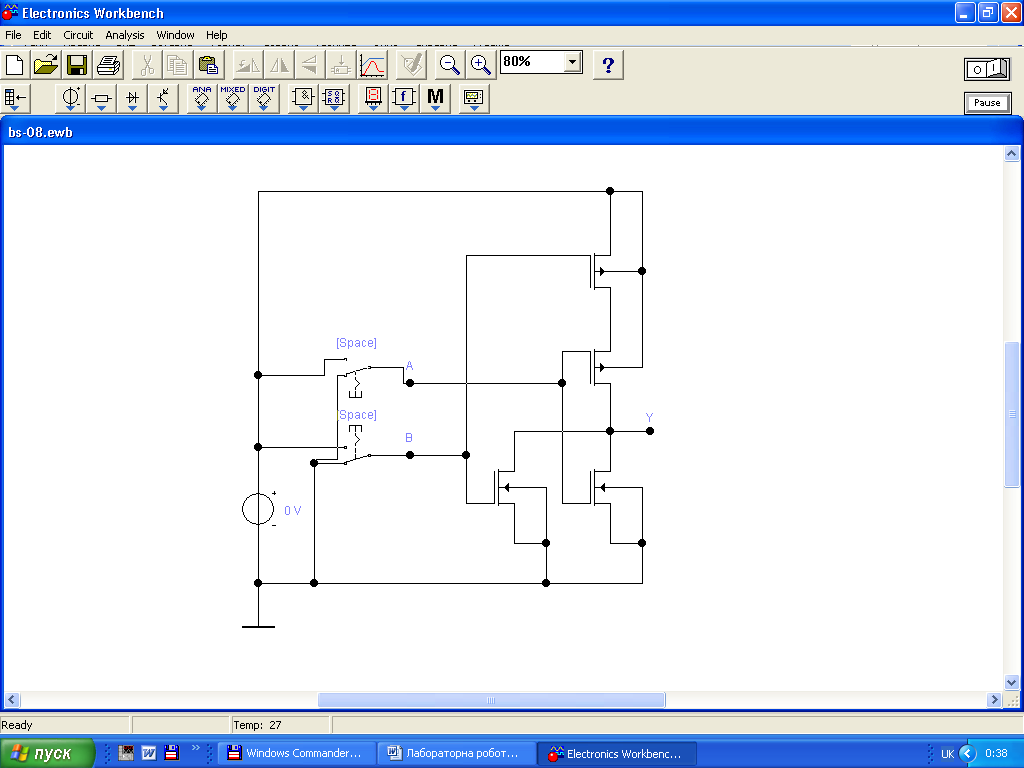

Примечание: для парных вариантов задается базис “И-НЕ”, для непарных – “ИЛИ-НЕ” Порядок выполнения работы: 1) Записать аналитическое выражение для булевой функции 2. Минимизировать полученные выражения СДНФ с помощью карт Карно или диаграмм Вейча и проверить результаты минимизации с помощью Electronics Workbench. 3. К минимизированной функции применить правило де Моргана. 4. Записать минимизированную структурную формулу в заданном базисе. На основе структурной формулы каждой логической операции ставится в соответствие логический элемент выбранного базиса и осущевстляются необходимые связи между элементами комбинационного устройства. 5. Оценить степень сложности схемы. Степень сложности схемы обычно оценивают общим числом ИМС данного типа и суммарным числом входов ЛЭ.  Задание 2. Построить схему комбинационного устройства на ЛЭ заданного базиса и провести исследования с помощью Electronics Workbench. Порядок выполнения работы: Собрать схему на ЛЭ заданного базиса в среде Electronics Workbench. Схема должна иметь четыре входа, например, А,В,С,D и один выход Y. Для большей наглядности добавте светодиоды , подключив их в точках схемы А,В,С,D и Y. 3. Включить моделирование. Нажимая клавиши А,В,С,D, следить за состоянием светодиодных индикаторов на входах и выходе схемы. Сложить таблицу истинности.  Вывод: любая логическая схема без памяти полностью описывается таблицей истинности. Эта таблица является исходной информацией для синтеза схемы на основе логических элементов «И», «ИЛИ», «НЕ». Для разработки требуемого цифрового устройства сначала на основе таблицы истинности записывают его логическое выражение. Затем с целью упрощения цифрового устройства минимизируют его логическое выражение и далее разрабатывают схему, реализующую полученное логическое выражение. Лабораторная работа № 2 Исследование базовых схем логических элементов цифровых устройств 1. Цель работы Ознакомиться с принципами работы базовых логических элементов транзисторно-транзисторной логики (ТТЛ) и элементов на униполярных транзисторах (МОП), провести исследования логических элементов, приобрести навыки схемотехнического моделирования на персональных компьютерах. 2. Порядок выполнения работы Задание 1. Исследование логических элементов транзисторно-транзисторной логики. Откройте файл Включаем моделирование. Нажимая клавиши А,В,С,D, следим за состоянием светодиодных индикаторов на входах и выходе схемы.  Рис.1  Задание 2. Исследование логических элементов на униполярных транзисторах. Откройте в начале файл <МОП1.ewb>, затем файл <МОП2.ewb>. Выставьте номиналы и обозначения элементов схем в соответствии с приведенными на рис.2,3. Подключите к точкам схемы А,В,Y индикаторы логического уровня. Включаем моделирование. Нажимая клавиши А и В, следим за состоянием индикаторов на входе и выходе схемы. Составляем таблицу истинности.  Рис.2

Рис.3

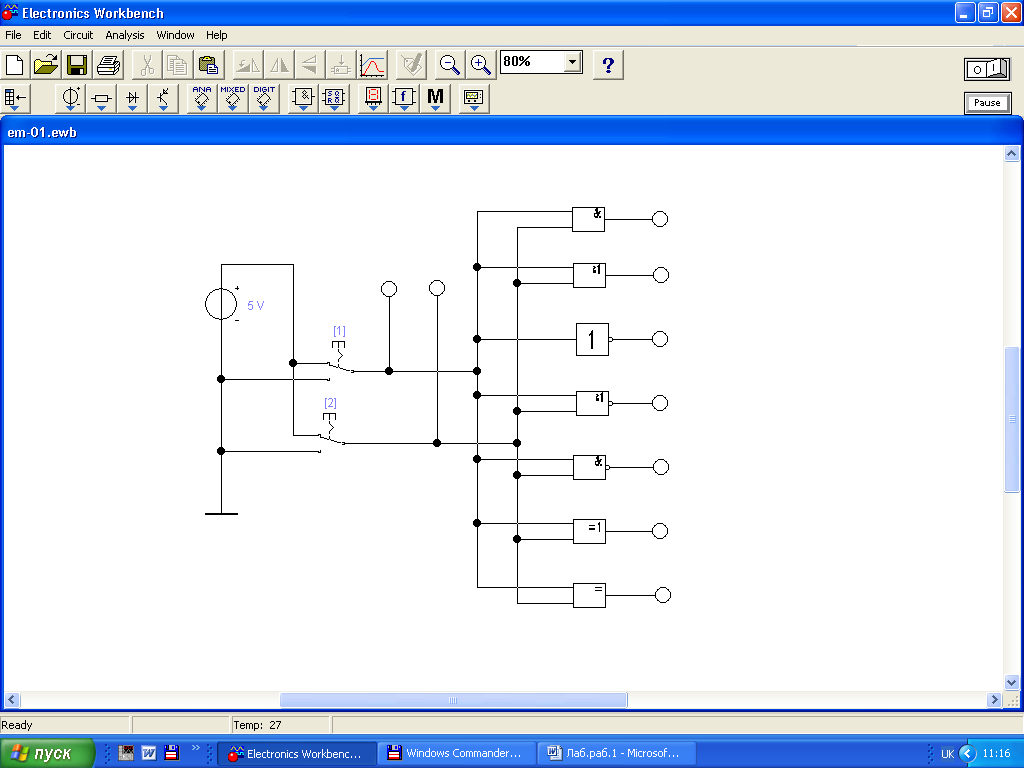

Задание 3. Исследование логических схем ( ручной режим). Откройте файл  Рис. 2.6. Набор базовых логических схем

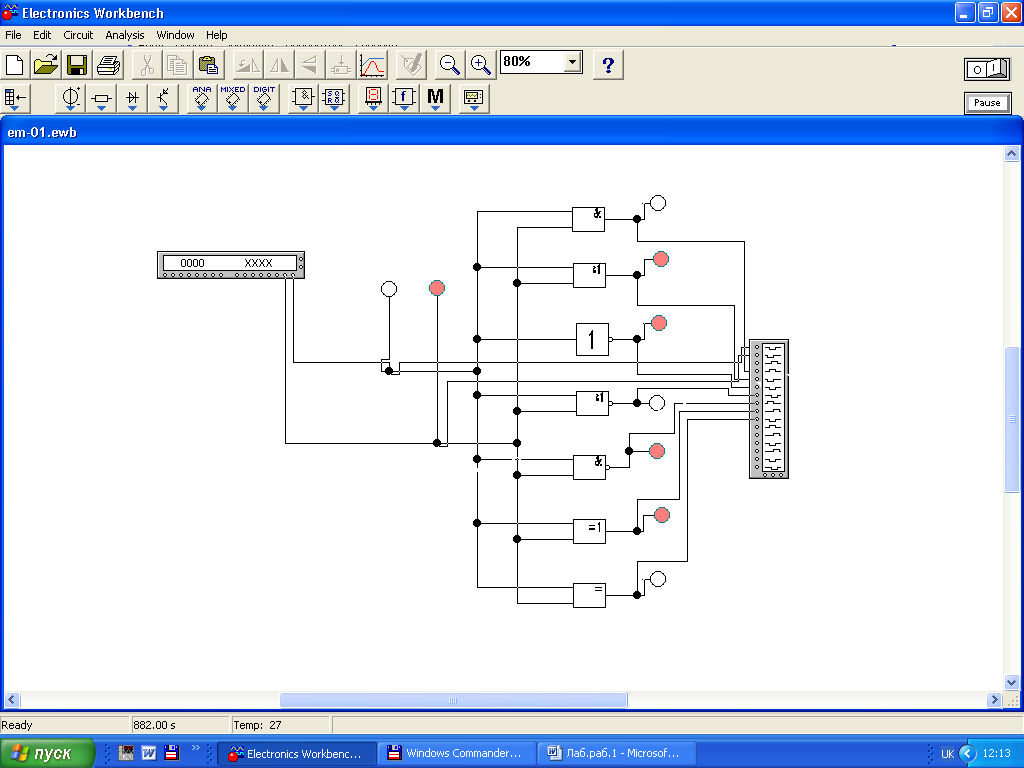

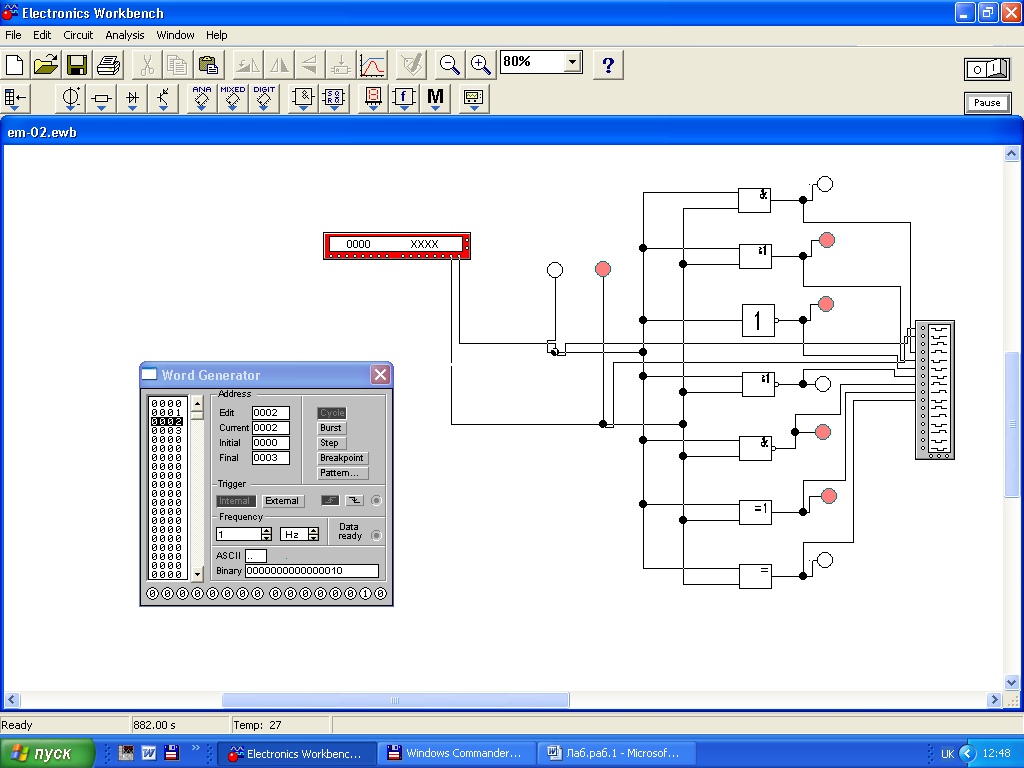

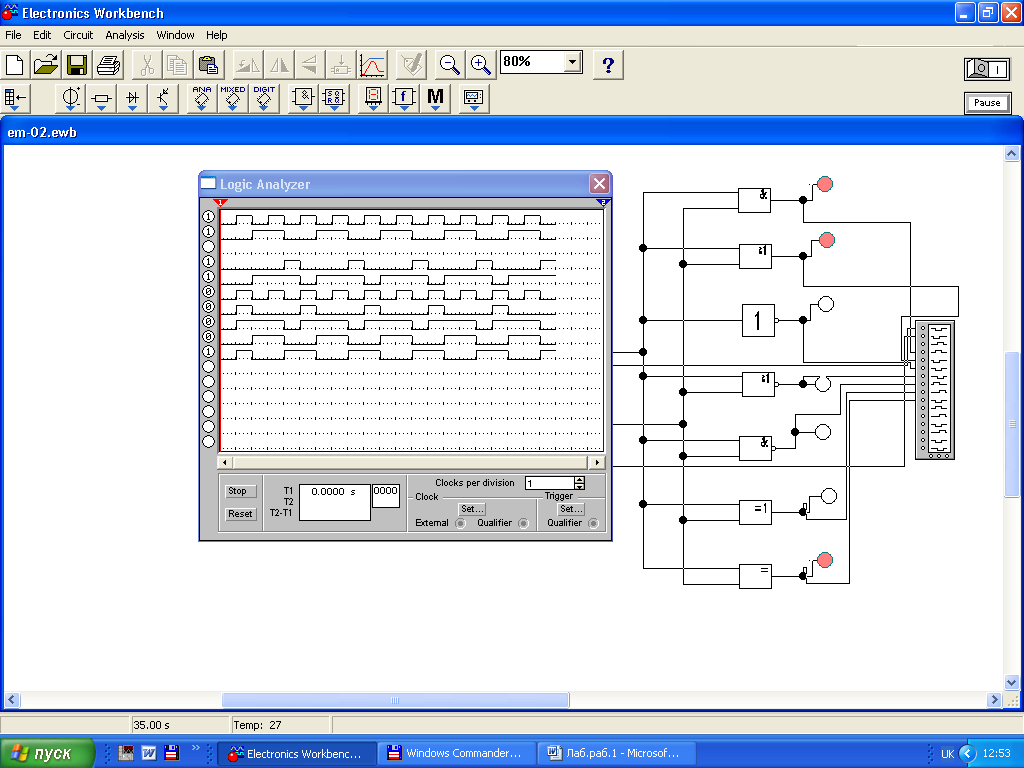

Задание 4. Исследование логических схем (автоматический режим). На панели инструментов откройте Inctruments. Выберите Word Generator и Loqis Analyzer. Удалите из схемы (Рис.4) источник питания и переключатели. Замените их генератором слов Word Generator. Подключите к входам и выходам схемы анализатор логики Loqis Analyzer. В результате получите схему, приведенную на рис.5.  Рис.5 Отредактируйте четыре первых слова генератора слов в окне Binary, выставив в двоичной системе счисления соответственно 0 (….0000), 1 (….0001), 2 (….0010), 3 (….0011). Выставьте конечный адрес (Final) 0003. Установите частоту выдачи слов Frequency 1Hz (рис.6). Приведите в соответствие также частоту тактирования в Loqis Analyzer, выставив Internal clok rate в Clok setup также 1Hz. Включите моделирование. Зафиксируйте осциллограммы логических сигналов и дайте им интерпретацию.   Вывод: в данной лабораторной работе исследовали базовую логику и определили реализуемые функции схемных решений. Также познакомились с принципом работы испытательного стенда для изучения устройств цифровой вычислительной техники. Лабораторная работа № 3 Исследование интегральных триггеров 1. Цель работы Изучение функционирования схем интегральных триггеров, овладение методами их проектирования, приобретения навыков исследования свойств триггеров с помощью персональных компьютеров. 2. Порядок выполнения лабораторной работы Задание 1. Исследование асинхронного RS - триггера на элементах И-НЕ. Открываем схему (файл

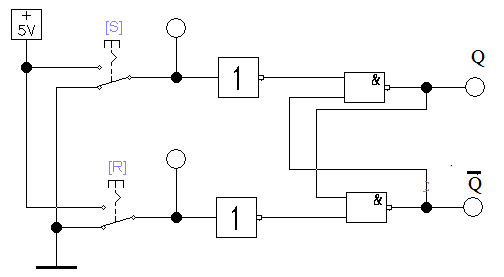

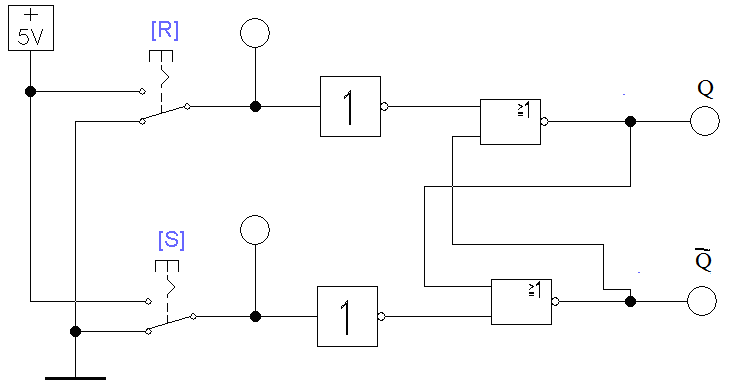

Рис. 3.3 Задание 2. Исследование асинхронного RS - триггера на элементах ИЛИ-НЕ. Открываем схему (файл

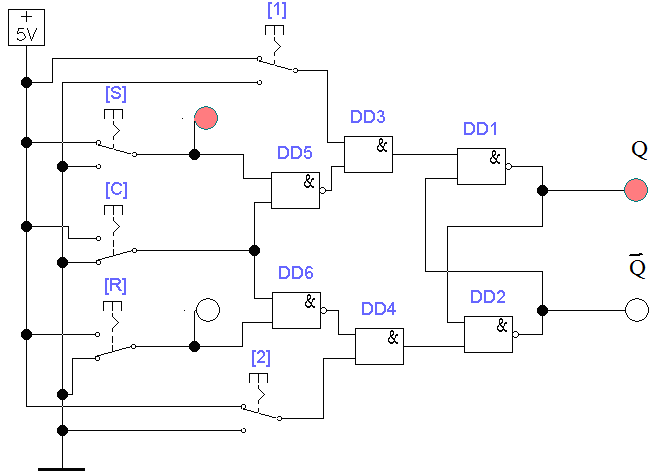

Рис. 3.4 Задание 3. Исследование синхронного RS - триггера на элементах И-НЕ. Используя панель инструментов, дополняем схему рис. 3.3 логическими элементами И-НЕ и выключателями так, чтобы получить схему синхронного RS -триггера, представленного на рис. 3.5. Составляем таблицу состояния на выходах триггера в зависимости от текущего и предыдущего состояния переключателей 1,2, R, S и С. Даем объяснение процессам в триггере в виде временных диаграмм. Приведите условное графическое изображение на схемах.

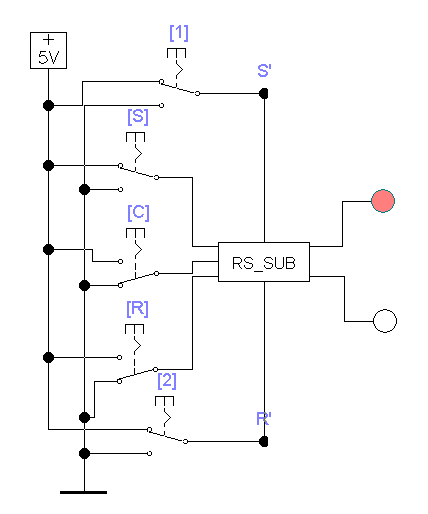

Рис. 3.5 Для упрощения изображения схемы триггера воспользуемся методикой построения субблоков. При нажатой левой кнопке мыши обведем все логические элементы схемы рис. 3.5, которые планируем включить в субблок. В меню откроем Circuit, выберем Create Subcircuit и нажмем на нем кнопку мыши. В окне pop-up меню Subcircuit напишем название субблока, например, RS_SUB. Удалим теперь часть схемы, которая вошла в субблок RS_SUB. На панели инструментов открываем Favorites, где должен находиться сформированный субблок RS_SUB. Забираем субблок и монтируем его в схему вместо удаленной части схемы. Должны получить схему, представленную на Рис. 3.6.  Рис. 3.6 После окончания монтажа схемы видим, что она работает так же, как и полная схема. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||