Лабораторные. АТПб(до)з-20-1_лабораторные_Герасимов_В.О. Герасимов Виктор Олегович Проверил преподаватель Сватов В. Ф. Тюмень Тиу 2023 лабораторная работа 1 Синтез и исследование

Скачать 1.39 Mb. Скачать 1.39 Mb.

|

|

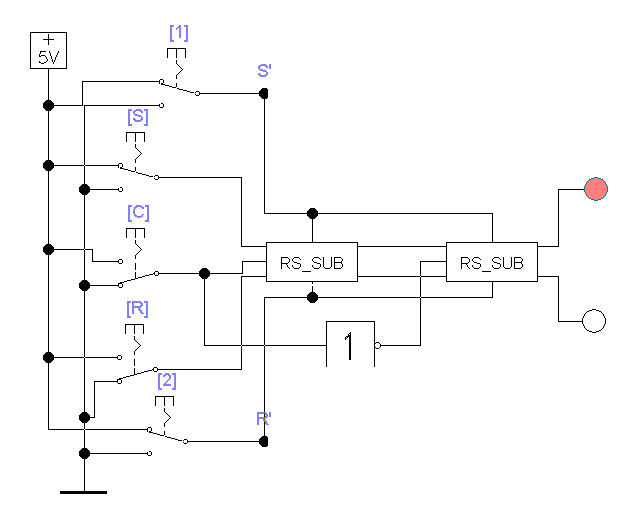

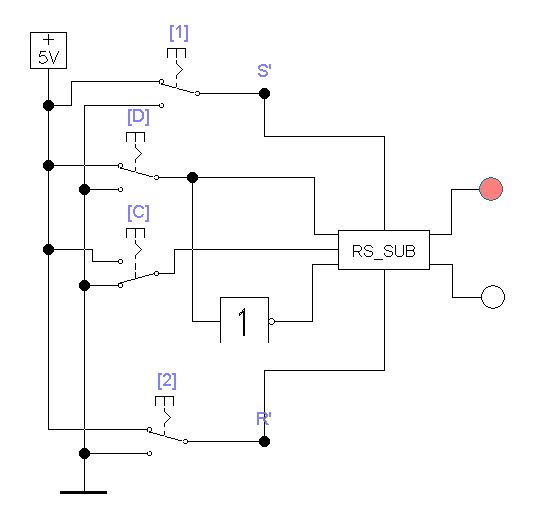

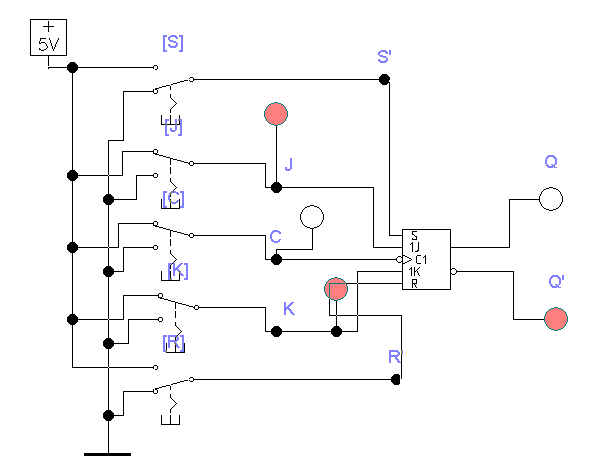

Задание 4. Исследование двухступенчатого синхронного RS - триггера. Синхронный двухступенчатый триггер со структурой "М-S" (Master-Slave) состоит из двух синхронных триггеров, где между основным (принимает новую входную информацию) и вспомогательным (передает старую информацию) включается инвертор, который блокирует перезапись информации во вспомогательный триггер при записи информации в основной триггер. Исполняем схему рис. 3.6 еще с одним схемным субблоком и сделаем соединения так, чтобы получить схему двухступенчатого синхронного RS-триггера, представленного на рис. 3.7.  Рис. 3.7 Проводим анализ работы схемы. Появление сигнала на выходе двухступенчатого триггера задерживается на время действия тактового импульса. Задание 5. Исследование D-триггера. Состояние D-триггера повторяет значение сигнала на D-входе в тактовые моменты времени. Схему D-триггера можно построить на основе синхронного RS-триггера, если сигнал на вход S одновременно подавать через инвертор и на вход R. Дополним схему рис. 3.6 логическим элементом НЕ, как показано на рис. 3.8

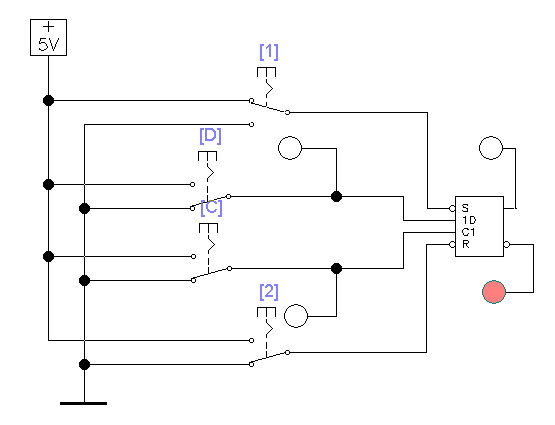

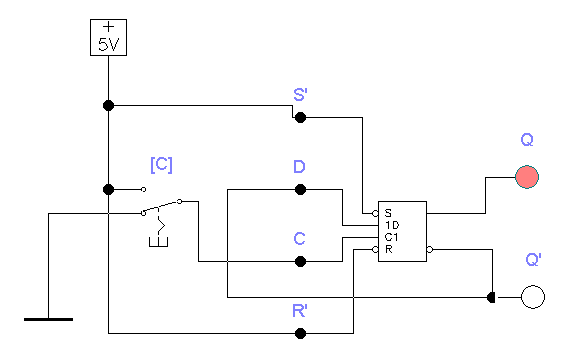

Рис. 3.8 Полученная схема, аналогична схеме показанной на рис. 3.9.  Рис. 3.9 Составляем таблицу состояния на выходах триггера в зависимости от текущего и предыдущего состояния переключателей 1,2, D и С. Даем объяснение процессам в триггере в виде временных диаграмм. Задание 6. Исследование Т-триггера. Открываем файл  Рис. 3.10 Частота выходных импульсов в 2 раза ниже частоты входных. Поэтому Т-триггеры используются как делители частоты на 2 или счетчики по модулю 2. В виде ИМС триггеры этого типа не выпускаются. Их можно легко создать на основе D- и JK-триггеров. Задание 7. Исследование универсального JK - триггера. Для исследования функционирования JK-триггера открываем файл

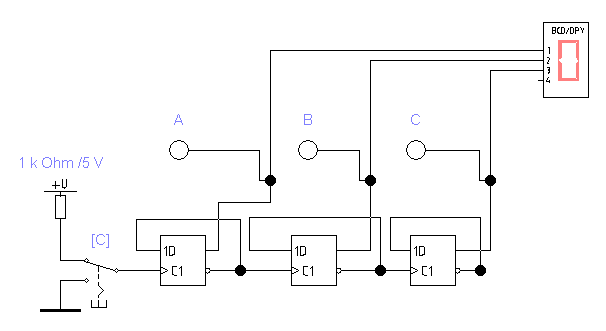

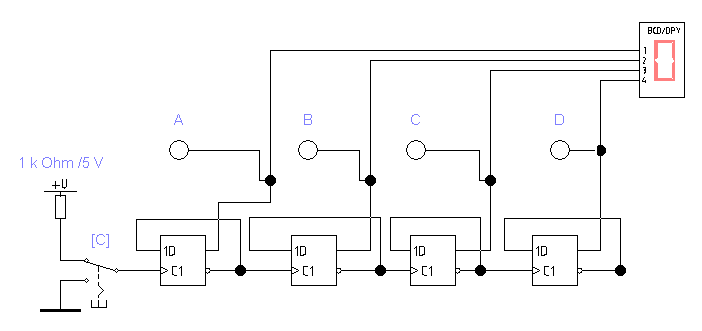

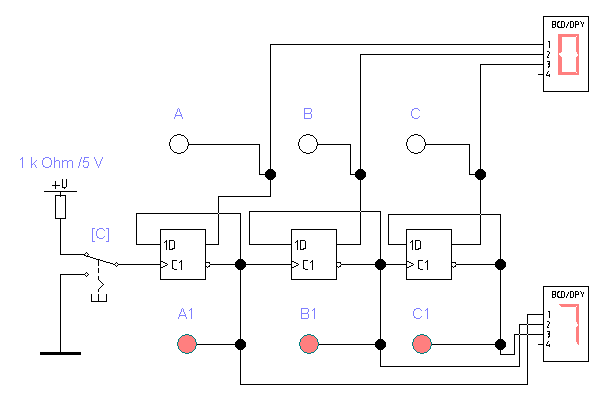

Рис. 3.11 При условии наличия нулевых сигналов на входах J, K, С триггер сохраняет свое состояние; сигнал на входе J = 1 включает триггер в состояние логической «1» (Q = 1) по окончании тактового импульса С = 1; сигнал на входе К = 1 сбрасывает триггер (Q = 0) по срезу тактового импульса С = 1; при наличии сигналов J = К = 0 поступление тактового импульса не вызывает изменений в состоянии триггера; Вывод: На базе JK-триггера можно создать: синхронный RS-триггер. Если принять, что J = S, К = R, а комбинацию J = К = 1 считать запрещенной. JK-триггер будет реагировать на изменение входных сигналов лишь в момент среза тактового импульса на входе С. Счетный Т-триггер. В этом триггере входы J и К соединяют между собой и подают на них напряжение логической единицы, так что J = К = 1, а вход С обозначают как Т. Тогда каждый тактовый импульс на входе синхронизации С = Т = 1 изменяет состояние триггера на противоположное. D-триггер. D-триггер может быть выполнен на базе JK-триггера включением на входах J, К элемента НЕ, который обеспечивает выполнение условий J = К '= D. В этом случае триггер запоминает сигнал на входе D в момент тактового импульса и держит его до следующего тактового импульса ("delay"-задержка). Поэтому D-триггер может использоваться как элемент памяти. Лабораторная работа № 4 Исследование счетчиков 1. Цель работы Изучение структуры и функционирования схемных разновидностей счетчиков, овладение методами их проектирования, приобретения навыков исследования с помощью персональных компьютеров. 3. Порядок выполнения лабораторной работы Задание 1. Построить и исследовать схему трехразрядного двоичного суммирующего счетчика с последовательным переносом на D – триггерах. Для построения схемы двоичного суммирующего счетчика руководствуются общими принципами их построения:  показания с двоичного счетчика снимаются с прямых выходов триггеров; показания с двоичного счетчика снимаются с прямых выходов триггеров; разряды двоичного счетчика строятся на двухступенчатых Т-триггерах или D-триггерах в счетном режиме; разряды двоичного счетчика строятся на двухступенчатых Т-триггерах или D-триггерах в счетном режиме; число разрядов n двоичного счетчика для заданного модуля М находят из выражения, число разрядов n двоичного счетчика для заданного модуля М находят из выражения,  где - знак округления до целого числа; где - знак округления до целого числа; счетные импульсы асинхронного суммирующего счетчика поступают на Т - вход только первого (младшего) разряда; счетные импульсы асинхронного суммирующего счетчика поступают на Т - вход только первого (младшего) разряда; сигналы переноса передаются асинхронно (последовательно во времени) с прямых выходов (для счетчиков на двухступенчатых Т - триггерах) и с инверсных выходов (для счетчиков на D - триггерах с динамическим управлением по фронту синхросигнала) соседних младших разрядов на Т - входы соседних старших; сигналы переноса передаются асинхронно (последовательно во времени) с прямых выходов (для счетчиков на двухступенчатых Т - триггерах) и с инверсных выходов (для счетчиков на D - триггерах с динамическим управлением по фронту синхросигнала) соседних младших разрядов на Т - входы соседних старших; изменение состояний триггеров в счетчиках на двухступенчатых Т-триггерах происходит по спаду (из 1 в 0), а в счетчиках на D - триггерах в счетном режиме - по фронту (из 0 в 1) входных импульсов. изменение состояний триггеров в счетчиках на двухступенчатых Т-триггерах происходит по спаду (из 1 в 0), а в счетчиках на D - триггерах в счетном режиме - по фронту (из 0 в 1) входных импульсов.Откройте файл  Рис. 4.1 Внимательно анализируем открытую схему. Включаем моделирование. Нажимая кнопку (выключатель) С, следим за состоянием светодиодов на выходах D - триггеров и по цифровому индикатору. Составьте таблицу состояний счетчика для серии последовательных тактов выключателя С, начиная со значения 0 цифрового индикатора. Чертим временную диаграмму работы счетчика. Задание 2. Увеличьте разрядность счетчика до 4-х. Для этого модернизируем схему асинхронного счетчика, добавив четвертый разряд так, как это показано на рис. 4.2.  Рис. 4.2 Запускаем моделирование. Составляем таблицу состояний счетчика (табл. 1) для серии последовательных тактов, начиная со значения 0 цифрового индикатора. Дайте объяснение процессам в схеме рис. 4.2. Таблица 1

Задание 3. Построить и исследовать схему трехразрядного двоичного вычитающего счетчика с последовательным переносом на D – триггерах. В двоичном вычитающем счетчике каждый вычитающий импульс уменьшает состояние счетчика на единицу. Сигналы межразрядной связи называются займами. По правилу двоичного вычитания заем из старшего разряда с единичным значением возникает при условии, если все младшие триггеры находятся в нулевом состоянии. После этого все они переключаются в состояние "1", а старшие - в состояние "0". Для создания вычитающих счетчиков чаще используют один из следующих способов:  в приведенных суммирующих счетчиках информацию снимать не с прямых, а с инверсных выходов триггеров; в приведенных суммирующих счетчиках информацию снимать не с прямых, а с инверсных выходов триггеров; сигналы займа снимаются с инверсных выходов двухступенчатых Т - триггеров или с прямых выходов D - триггеров в счетном режиме. сигналы займа снимаются с инверсных выходов двухступенчатых Т - триггеров или с прямых выходов D - триггеров в счетном режиме.Число, соответствующее значению кода на прямых выходах триггера счетчика (NПР), связано с числом, которое соответствует значению кода на инверсных выходах (NИНВ) триггеров, следующим выражением:  . .В таблице 2 приведен пример связи числа NПР с числом NИНВ трехразрядного двоичного счетчика. Таблица 2

Открываем файл  Рис. 4.3 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||