Схемотехника лаб. 1 Мухаметов. Исследование и синтез устройств комбинационного типа Мультиплексоры и демультиплексоры

Скачать 52.39 Kb. Скачать 52.39 Kb.

|

|

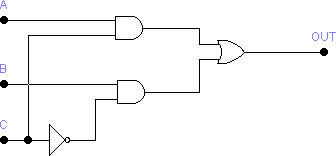

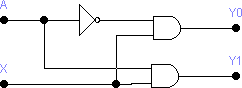

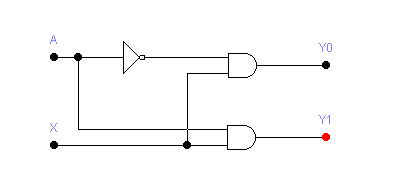

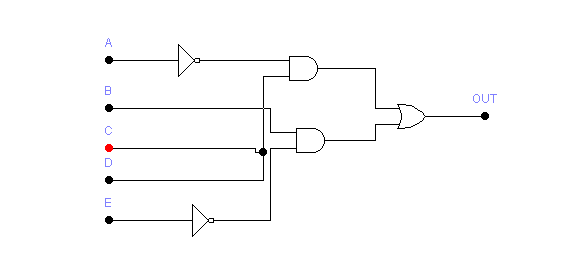

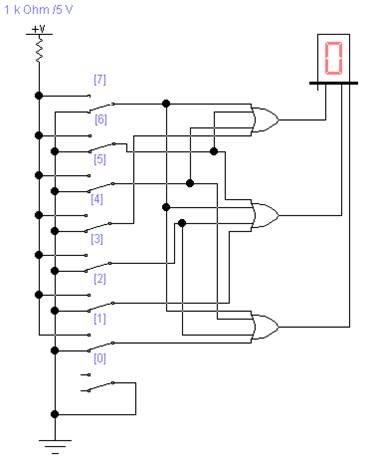

Мухаметов Тахир ВТиПО-21-2у Лабораторная работа №1Цель работы: Исследование и синтез устройств комбинационного типа Мультиплексоры и демультиплексорыНазначение мультиплексоров – коммутировать в заданном порядке сигналы, поступающие с нескольких входных шин на одну выходную. У мультиплексора может быть, например, 16 входов и один выход. Для выбора любого из 16 каналов необходимо иметь 4 входа селекции (24 = 16), на которые подается двоичный адрес канала. Так, для передачи данных от канала номер 9 на входах селекции необходимо установить код 1001. В силу этого мультиплексоры часто называют селекторами или селекторами-мультиплексорами. Мультиплексоры применяются, например, в МП 18088 для выдачи на одни и те же выводы МП адреса и данных, что позволяет существенно сократить общее количество выводов микросхемы; в микропроцессорных системах управления мультиплексоры устанавливают на удаленных объектах для возможности передачи информации по одной линии от нескольких установленных на них датчиков. На рисунке 3.3 приведена схема двухканального мультиплексора, состоящего из элементов ИЛИ, НЕ и двух элементов И.  Рисунок 3.3 - Схема двухканального мультиплексора Результаты моделирования двухканального мультиплексора, показывают, что его выходной сигнал описывается булевым выражением ОUТ=ВС'+АС, т.е. сигнал из канала А проходит на выход при адресном входе С=0, а из канала В – при С=1, что и соответствует логике работы мультиплексора. Демультиплексоры в функциональном отношении противоположны мультиплексорам. С их помощью сигналы с одного информационного входа распределяются в требуемой последовательности по нескольким выходам. Выбор нужной выходной шины, как в мультиплексоре, обеспечивается установкой соответствующего кода на адресных входах. При тадресных входах демультиплексор может иметь до 2m выходов. Принцип работы демультиплексора поясним с помощью схемы на рисунке 3.4, на котором обозначено: Х – информационный вход, А – вход адреса, YО, Y1 – выходы. Схема содержит два элемента И и один элемент НЕ. Из рисунка 3.18 нетрудно видеть, что при А=0 сигнал информационного входа передается на выход Y0, а при А=1 на выход Y1  Рисунок 3.4 - Схема демультиплексора Шифраторы и дешифраторыШифраторы (кодеры) используются чаще всего для преобразования десятичных чисел в двоичный или двоично-десятичный код, например, в микрокалькуляторах, в которых нажатие десятичной клавиши соответствует генерации соответствующего двоичного кода. Поскольку возможно нажатие сразу нескольких клавиш, в шифраторах используется принцип приоритета старшего разряда. Дешифратор (декодер) – устройство с несколькими входами и выходами, у которого определенным комбинациям входных сигналов соответствует активное со стояние одного из выходов, т.е. дешифратор является обращенным по входам демультиплексором, у которого адресные входы стали информационными, а бывший информационный вход стал входом разрешения. Поэтому часто дешифраторы называют дешифраторами-демультиплексорами и наоборот. Дешифраторы и демультиплексоры в виде серийных ИМС средней степени интеграции широко используются в информационно-измерительной технике и микропроцессорных системах управления, в частности, в качестве коммутаторов распределителей информационных сигналов и синхроимпульсов, для демультиплексирования данных и адресной логики в запоминающих устройствах, а также для преобразования двоично-десятичного кода в десятичный с целью управления индикаторными и печатающими устройствами. Дешифраторы как самостоятельные изделия электронной техники имеют 4, 8 или 16 выходов. Если требуется большее число выходов, дешифраторы наращиваются в систему. Цифровой компараторЦифровые компараторы (от английского compare – сравнивать) выполняют сравнение двух чисел А, В одинаковой разрядности, заданных в двоичном или двоично-десятичном коде. В зависимости от схемного исполнения компараторы могут определять равенство А==В или неравенства А<В, А>В. Результат сравнения отображается в виде логического сигнала на одноименных выходах. Цифровые компараторы применяются для выявления нужного числа в цифровых последовательностях, для отметки времени в часовых приборах, для выполнения условных переходов в вычислительных устройствах, а также в адресных селекторах. Устройство контроля четностиОперация контроля четности двоичных чисел позволяет повысить надежность передачи и обработки информации. Ее сущность заключается в суммировании по модулю 2 всех разрядов с целью выяснения четности числа, что позволяет выявить наиболее вероятную ошибку в одном из разрядов двоичной последовательности. Например, если при передаче кода 1001 произойдет сбой во втором разряде, то на приемном пункте получим код 1101 – такую ошибку определить в общем случае затруднительно. Если же код относится к двоично- десятичному (8-4-2-1), то ошибку легко обнаружить, поскольку полученный код (десятичный эквивалент – число 13) не может в принципе принадлежать к двоично-десятичному. Обнаружение ошибок путем введения дополнительного бита четности происходит следующим образом. На передающей стороне передаваемый код анализируется и дополняется контрольным битом до четного или нечетного числа единиц в суммарном коде. Соответственно суммарный код называется четным или нечетным. В случае нечетного кода дополнительный бит формируется таким образом, чтобы сумма всех единиц в передаваемом коде, включая контрольный бит, была нечетной. При контроле четности все, естественно, наоборот. Например, в числе 0111 число единиц нечетно. Поэтому при контроле нечетности дополнительный бит должен быть нулем, а при контроле четности – единицей. На практике чаще всего используется контроль нечетности, поскольку он позволяет фиксировать полное пропадание информации (случай нулевого кода во всех информационных разрядах). На приемной стороне производится проверка кода четности. Если он правильный, то прием разрешается, в противном случае включается сигнализация ошибки или посылается передатчику запрос на повторную передачу. Схема формирования бита четности для четырехразрядного кода содержит четыре элемента Исключающее ИЛИ, выполняющий функции сумматоров по модулю 2 (без переноса) и состоит из трех ступеней. На первой ступени попарно суммируются все биты исходного кода на входах А, В, С, D. На второй ступени анализируются сигналы первой ступени и устанавливается четность или нечетность суммы входного кода. На третьей ступени полученный результат сравнивается с контрольным сигналом на входе Е, задающим вид используемого контроля, в результате чего на выходе F формируется пятый дополнительный бит, четности, сопровождающий информационный сигнал в канале передачи. Контрольные вопросы и заданияЧто такое мультиплексор, каково его назначение? Mультипле́ксор — устройство, имеющее несколько сигнальных входов, один или более управляющих входов и один выход. Мультиплексор позволяет передавать сигнал с одного из входов на выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов Используя методику анализа двухканального мультиплексора с по- мощью логического преобразователя, исследуйте внутреннюю структуру сдвоенного четырехканального мультиплексора 74153. Из сопоставления обозначений выводов этой ИМС и ее отечественного аналога К155КП2 следует, что их функциональное назначение таково: А, В – адресные входы, 10, 20 – инверсные входы разрешения первого и второго мультиплексоров, 1С0...1СЗ и 2С0...2СЗ, IY и 2Y – входы и выходы первого и второго мультиплексоров соответственно. Что такое демультиплексор, для решения каких задач его можно применить? Демультиплексор — это логическое устройство, предназначенное для переключения сигнала с одного информационного входа на один из информационных выходов. Таким образом, демультиплексор в функциональном отношении противоположен мультиплексору. На схемах демультиплексоры обозначают через DMX или DMS. C помощью логического преобразователя, проведите исследования демультиплексора на рисунке 3.4.  Синтезировать мультиплексор с 5 информационными входами.  Реализовать функцию из лабораторной №1 задание №7, используя 16-канальный мультиплексор. Синтезировать демультиплексор с 3 адресными входами.  Что такое шифратор, при решении каких задач он используется? Шифратор — логическое устройство, выполняющее логическую функцию — преобразование позиционного n-разрядного кода в m-разрядный двоичный, троичный или k-ичный код. Синтезировать приоритетный шифратор на 10 входов.  При решении каких задач цифровой техники используется дешиф- ратор? При подаче на входы двоичного числа появляется сигнал на определенном выходе, номер которого соответствует входному числу. Дешифраторы имеют широкое применение. В частности, они используются в устройствах, печатающих на бумаге выводимые из цифрового устройства числа или текст. Синтезировать трехразрядный дешифратор на 6 или 5 выходов. Какие функции выполняет цифровой компаратор, в каких устройст- вах он может быть использован? Цифрово́й компара́тор или компара́тор ко́дов логическое устройство с двумя словарными входами, на которые подаются два разных двоичных слова равной в битах длины и обычно с тремя двоичными выходами, на которые выдаётся признак сравнения входных слов, — первое слово больше второго, меньше или слова равны. При этом выходы «больше», «меньше» имеют смысл, если входные слова кодируют числа в том или ином машинном представлении. Часто цифровые компараторы не имеют выходов «больше», «меньше», а только выход «равно». Синтезировать двухразрядный цифровой компаратор и проверить его работу. Синтезировать четырехразрядный цифровой компаратор и прове- рить его работу. Какое назначение имеют формирователи кода четности, где они могут быть использованы? они исправляют одиночную ошибку и находят двойную. используются там где код Хэмминга достаточен Какая форма контроля четности чаще всего используется на практике, в частности, в Вашем компьютере, если в нем установлены модули ОЗУ с нечетным числом микросхем? На практике чаще всего используется контроль нечетности, поскольку он позволяет фиксировать полное пропадание информации (случай нулевого кода во всех информационных разрядах). Синтезировать устройство генерации контрольного разряда для восьмиразрядного кода при контроле на четность. Синтезировать устройство генерации контрольного разряда для восьмиразрядного кода при контроле на нечетность. Синтезировать устройство контроля восьмибитного числа по не- четности. Синтезировать устройство контроля восьмибитного числа по чет- ности. |