Лекции по ВМСС. Конспект лекций по курсу "Электронные вычислительные машины, системы и сети"

Скачать 3.89 Mb. Скачать 3.89 Mb.

|

|

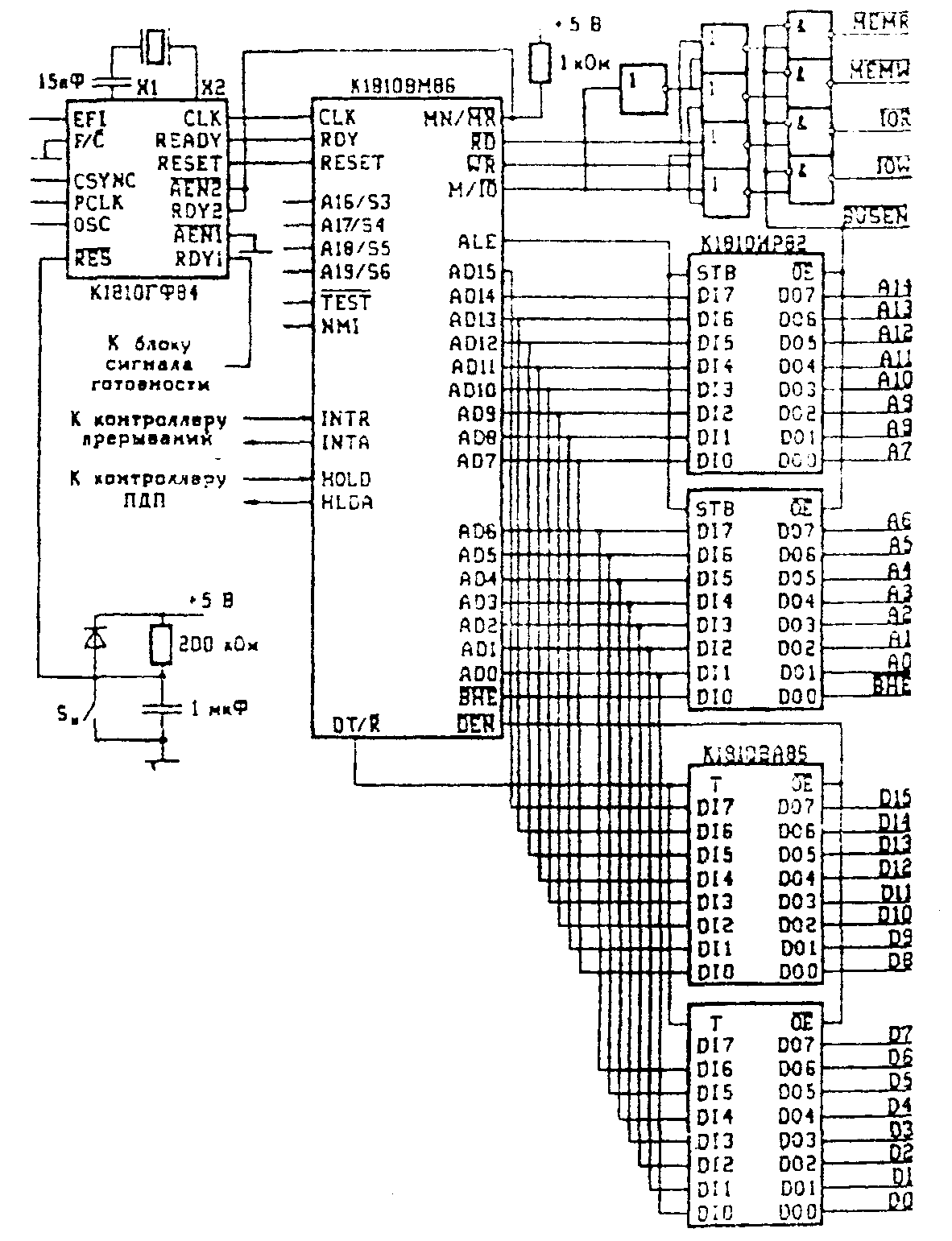

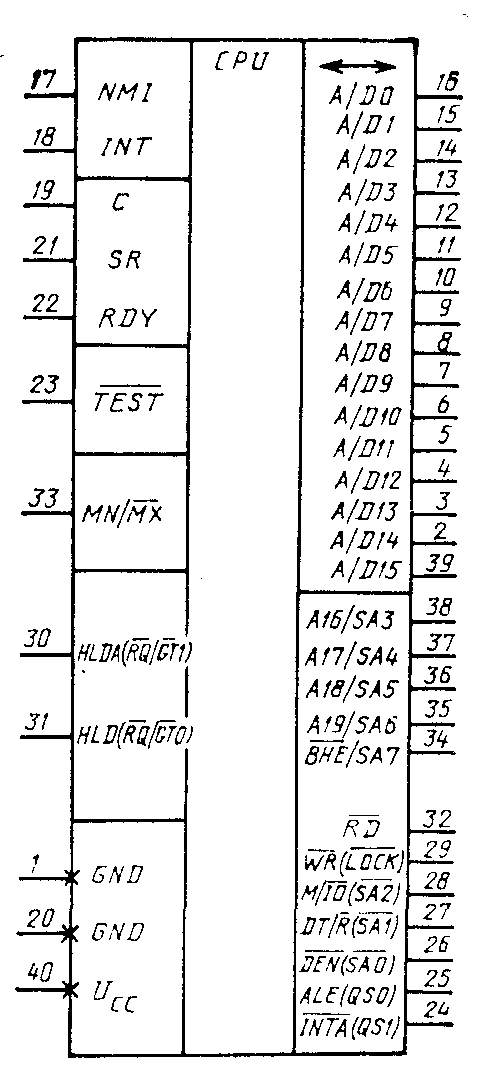

ЗАКЛЮЧЕНИЕ Мы рассмотрели структуру процессора 80286 и формат команд. В следующей лекции мы обратимся к самим командам. Процессор 80286, работающий в реальном режиме, практически аналогичен микропроцессору 8086, поэтому литературные источники по микропроцессору 8086 относятся и к процессору 80286. Центральный процессор При разработке структуры блока ЦП возникают задачи разделения (демультиплексирования) шины адреса/данных (ШАД), буферирования шин адреса (ША) и шин данных (ШД), а также формирования системных управляющих сигналов для блоков памяти и внешних устройств. Первая задача решается с помощью ИС К1810ИР82/83, выполняющих функции адресной защелки. Так как сигнал ВНЕ формируется в том же интервале времени, что и адресные сигналы, то его также необходимо зафиксировать в защелке. Поэтому изображенные на рис. 4 два 8-битовых регистра К1810ИР82 обеспечивают запоминание 15 разрядов адреса. Для доступа к памяти максимальной емкостью 1 Мбайт необходимо подключить еще один регистр, на который подаются оставшиеся старшие разряды AD15, A19/S 6 — A16/S3. Вторая задача решается с помощью двунаправленных 8-битовых шинных формирователей К1810ВА86/87, которые усиливают сигналы системной шины данных. Третья задача может быть решена с помощью комбинационных логических схем, которые формируют требуемые управляющие сигналы на основе сигналов RD, WR и M/IO, вырабатываемых МП. Если в системе используется адресное пространство ввода — вывода, изолированное от пространства памяти, то целесообразно сформировать сигналы, аналогичные сигналам на выходах системного контроллера К580ВК28: MEMR, MEMW, IOR, IOW. Эти сигналы управляют запоминающими и внешними устройствами подобно тому, как это делается в системах, построенных на основе МП К580ВМ80. Роль формирователей сигналов могут выполнять элементы ИЛИ-НЕ (рис. 4) или дешифратор на три входа (например, К155ИД7). Если же в МПС ввод — вывод организован с отображением на память, то сигнал М/IO не используется и на ЗУ и ВУ подаются сигналы RD и WR после усиления. Используемые усилители и формирователи должны обеспечивать три выходных состояния, чтобы можно было организовать прямой доступ к памяти. В этом случае после перевода МП в состояние захвата эти усилители переходят в третье состояние по сигналу РМ (BUSEN), поступающему от контроллера ПДП. Если захват шин и обмен данными по ПДП не предусмотрен, то необходимость в таком переключении отпадает.  рис. 4 Схема ЦП на баз МП К1810ВМ86 в минимальном режиме 4. Назначение выводов МП  рис. 3 Условное графическое обозначение К1810ВМ86 Назначение выводов БИС зависит от режима работы МП . Восемь выводов имеет двойное обозначение, причем обозначения в скобках соответствуют максимальному режиму. В табл. 2 приведено назначение выводов МП, являющихся общими для обоих режимов, в табл. 3 - назначение выводов, используемых только в минимальном режиме, а в табл. 4 - используемых только в максимальном режиме. Буквой z отмечены трехстабильные выходы, которые переводятся в третье (высокоомное) состояние при переходе МП в режим состояния захвата; в скобках приведены альтернативные обозначения выводов, встречающиеся в литературе. Таблица 2

Таблица 3

Таблица 4

|