Лекции по ВМСС. Конспект лекций по курсу "Электронные вычислительные машины, системы и сети"

Скачать 3.89 Mb. Скачать 3.89 Mb.

|

|

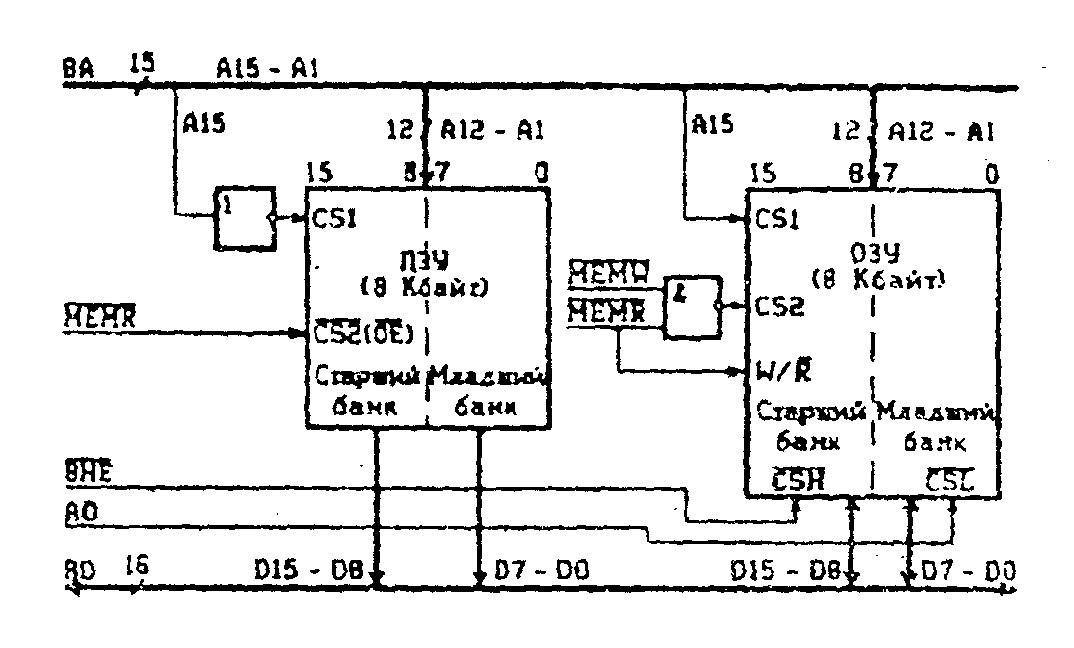

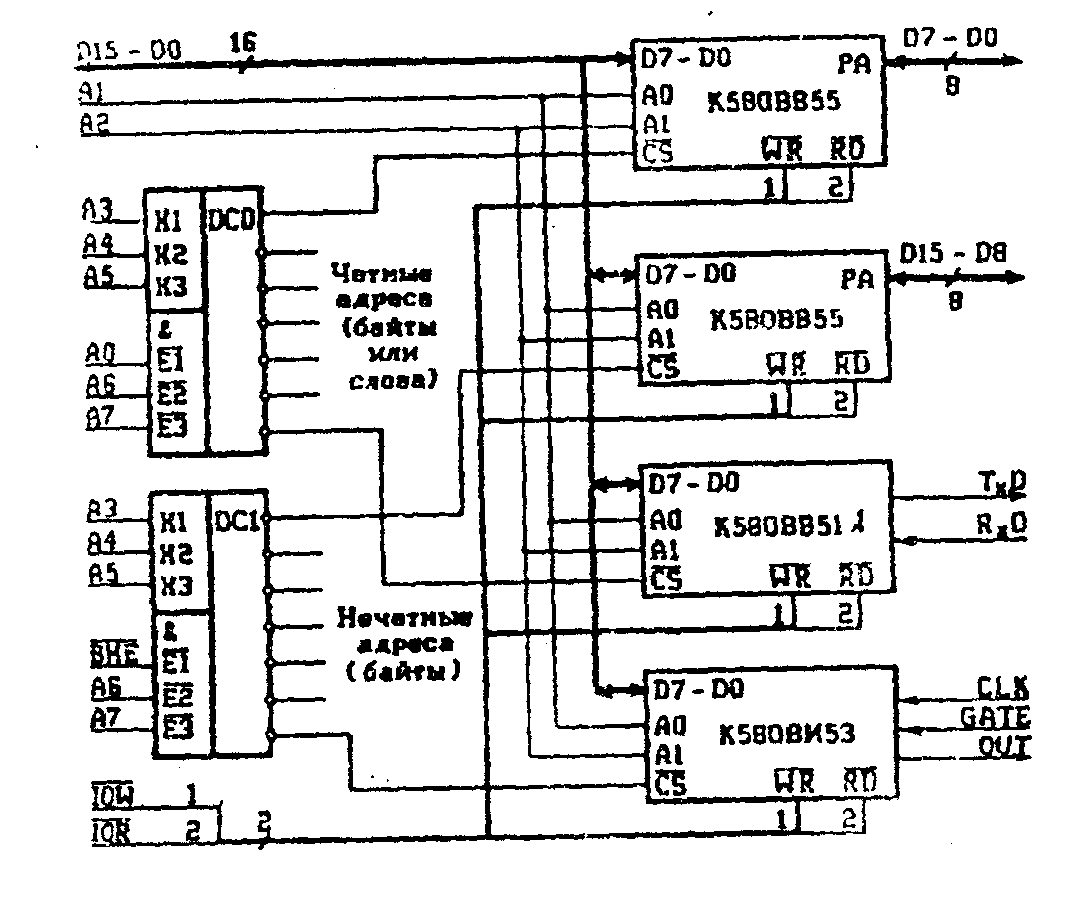

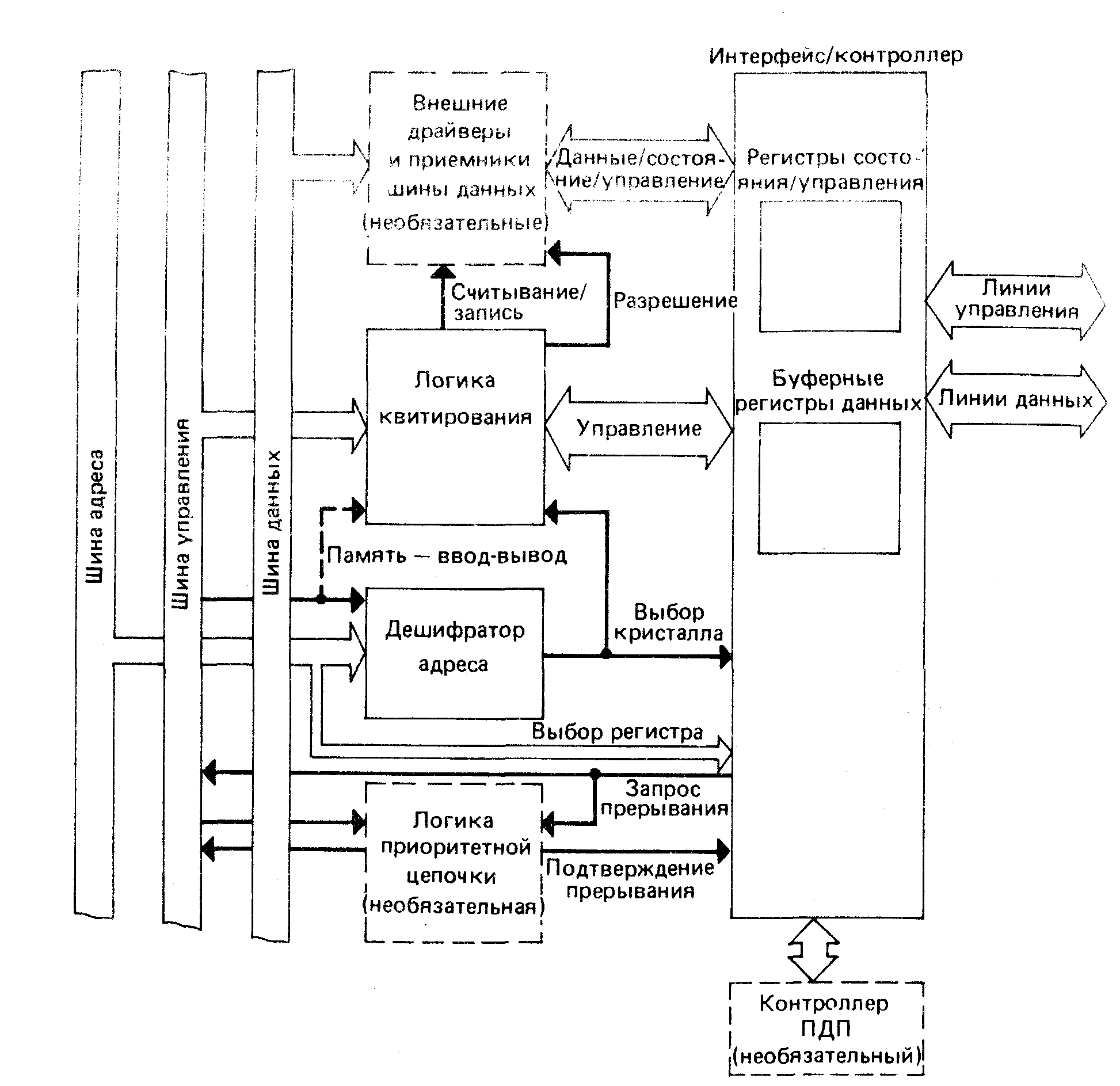

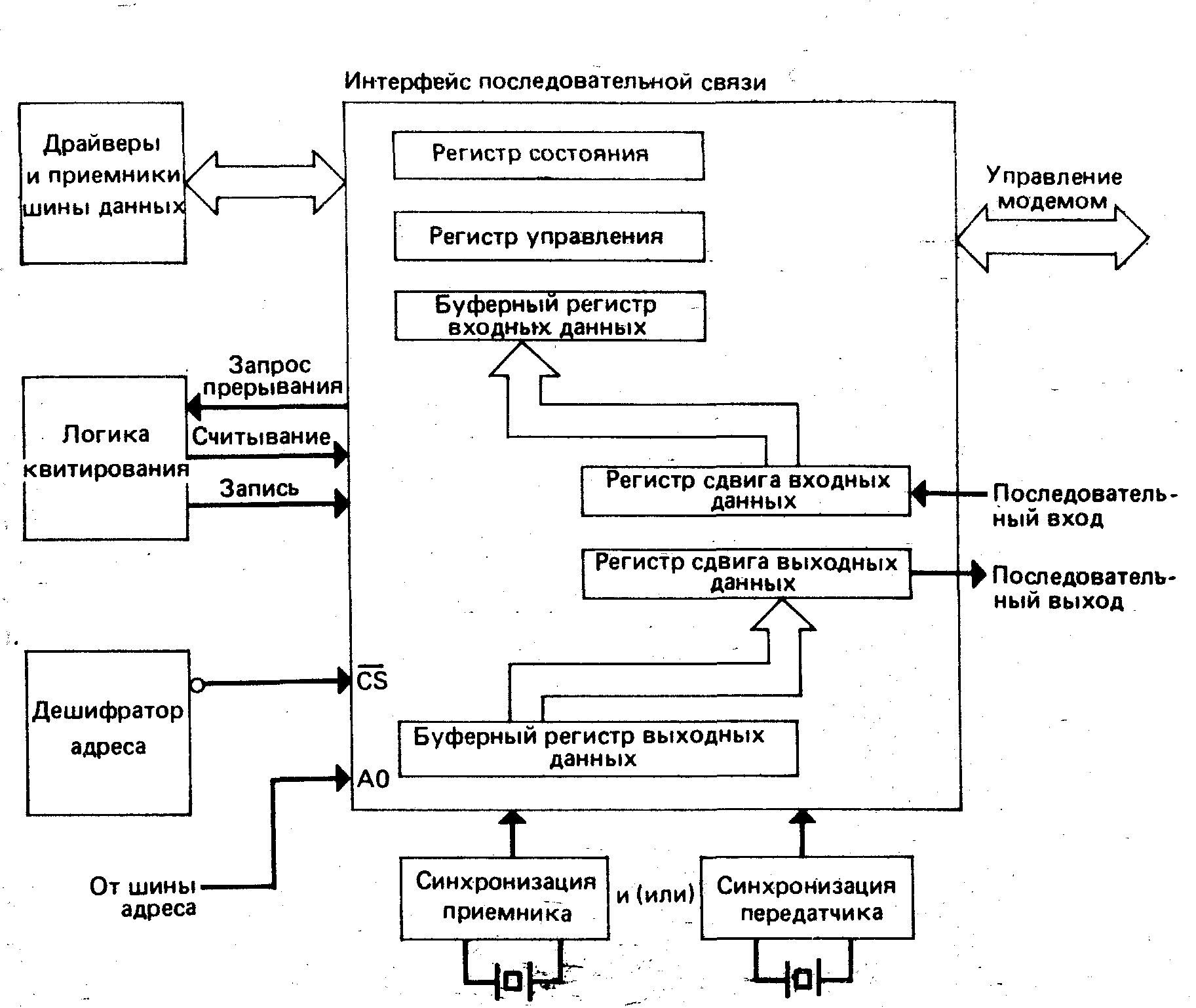

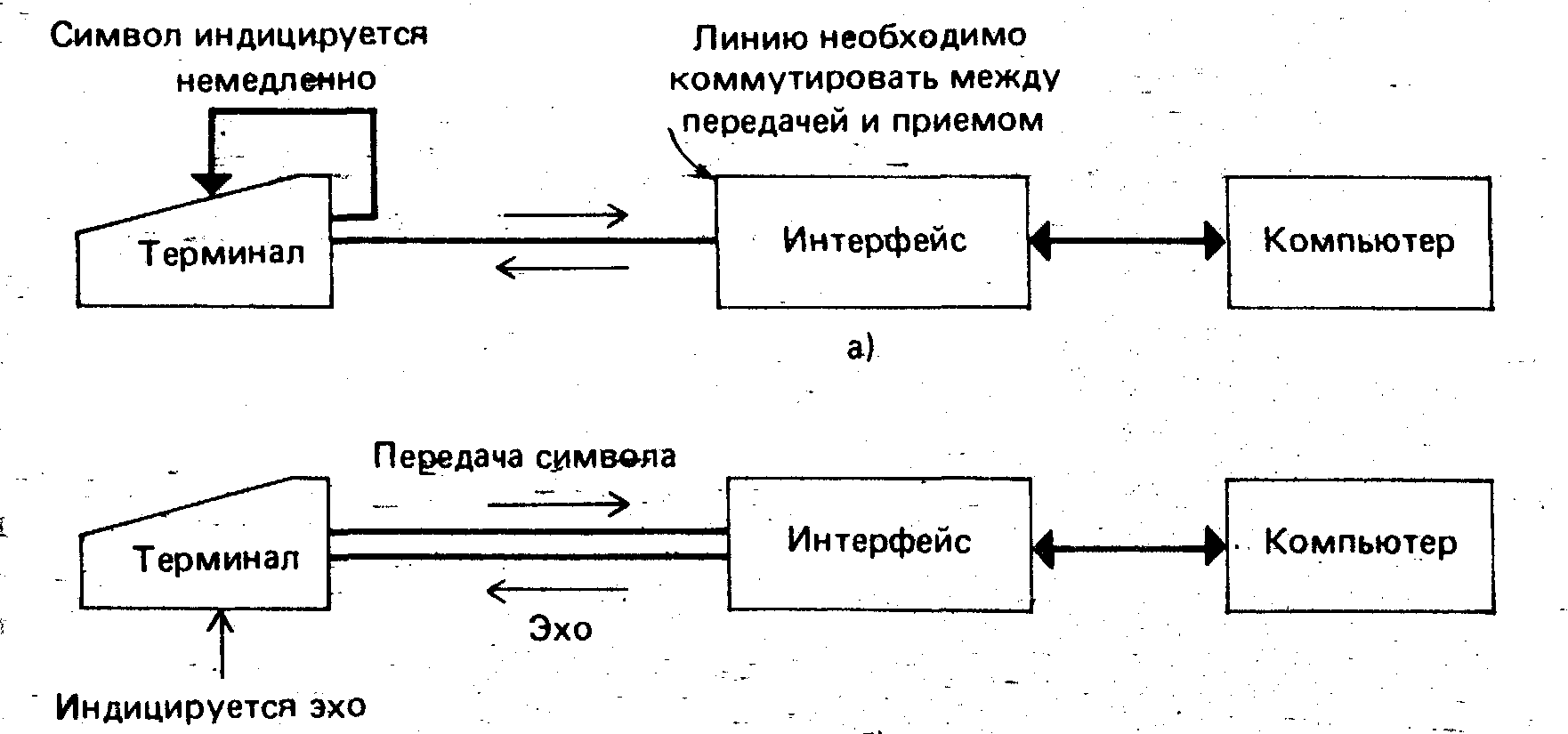

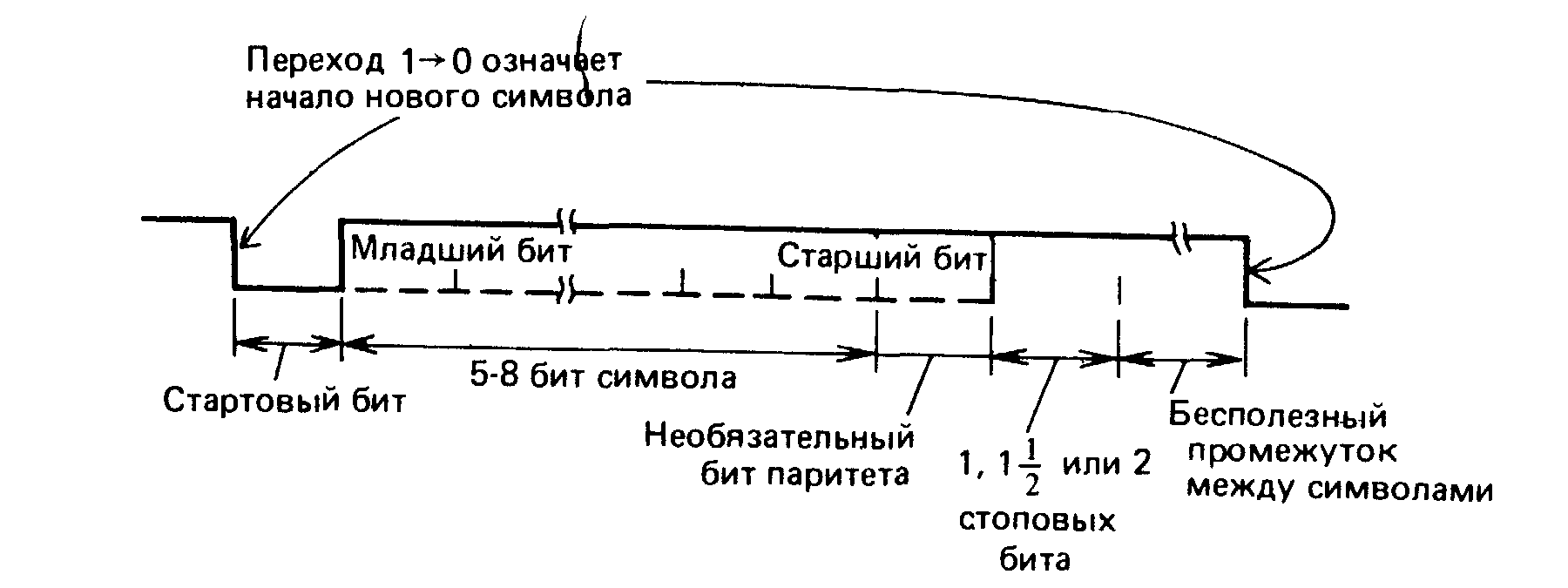

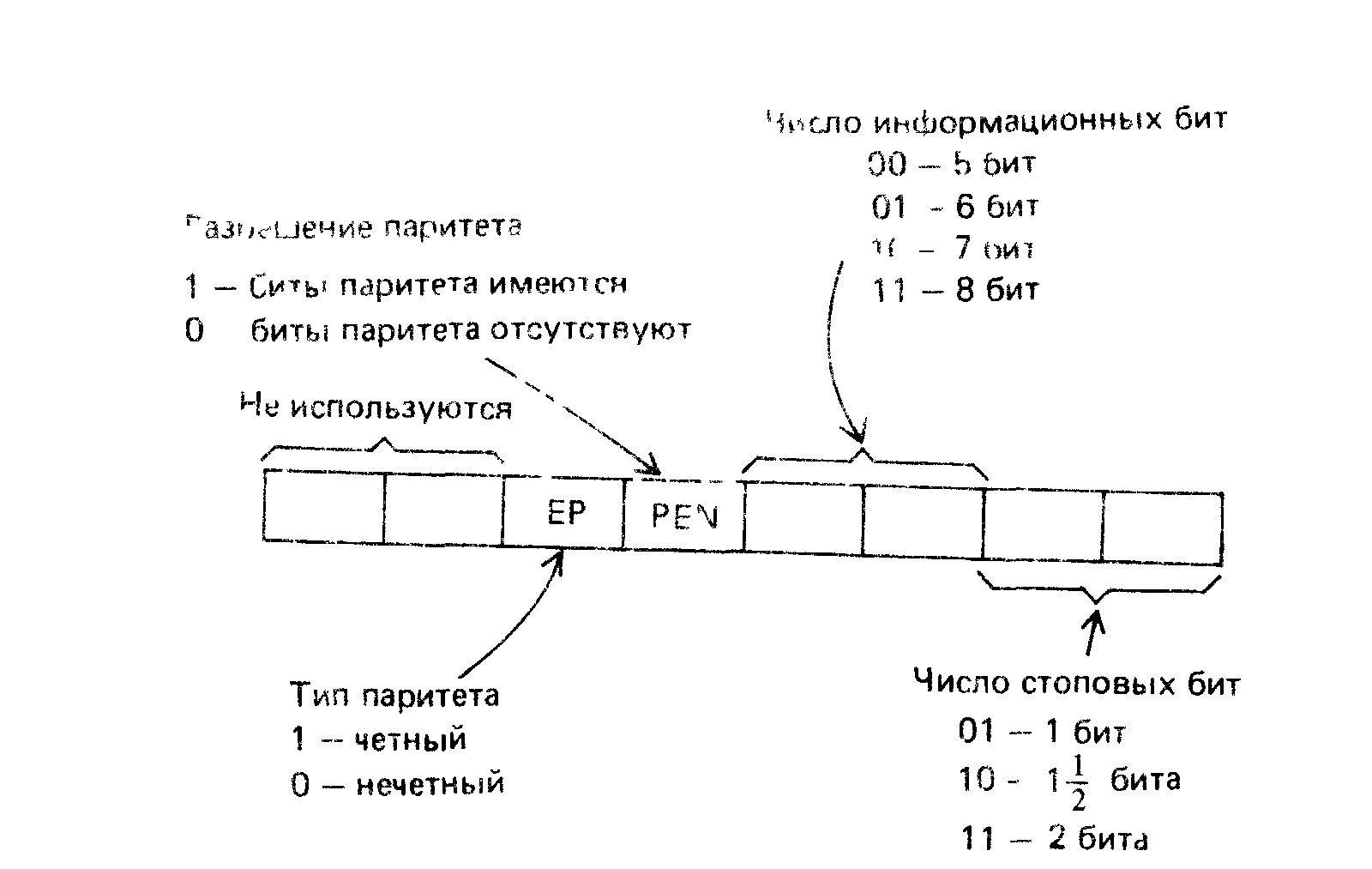

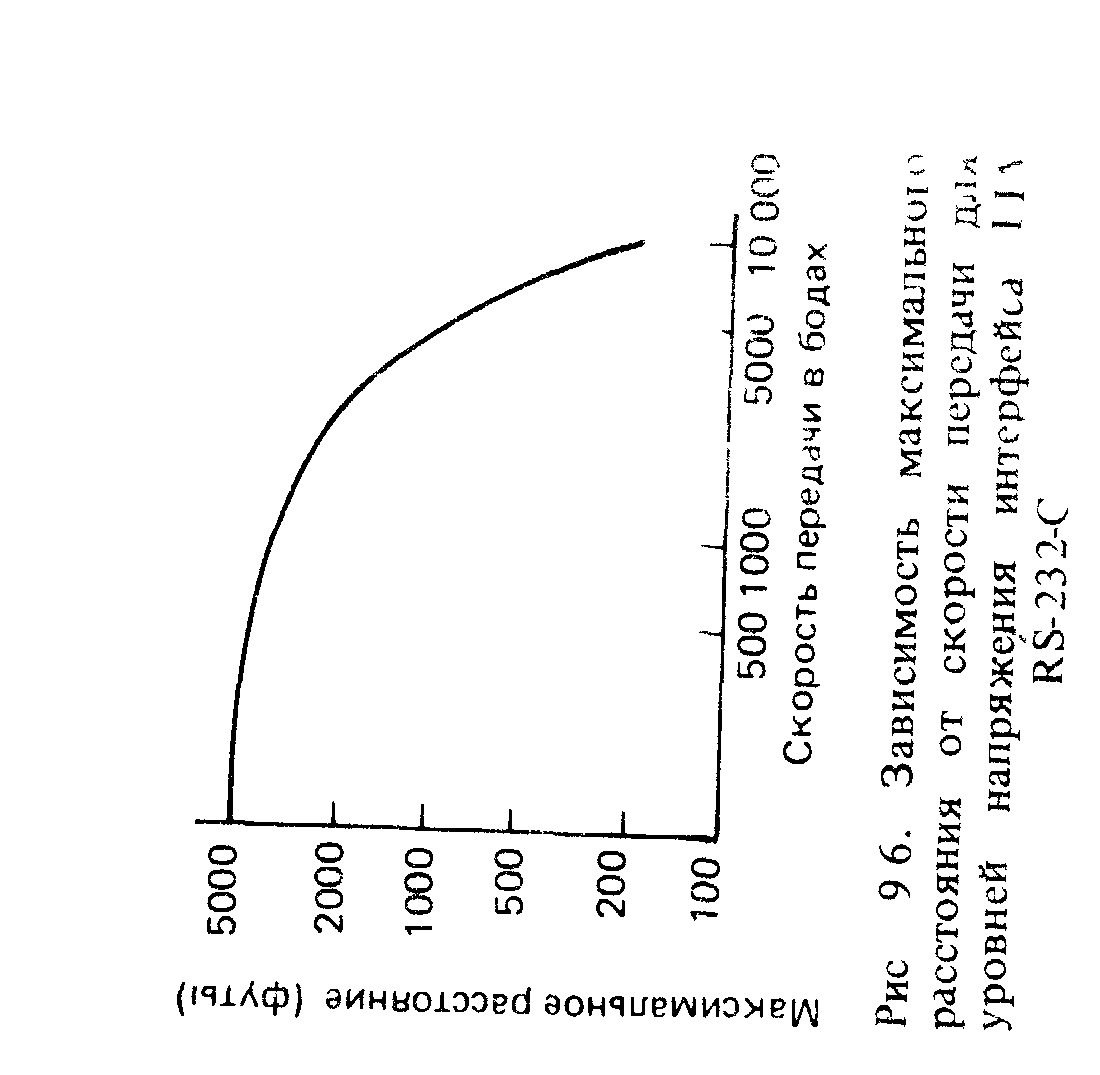

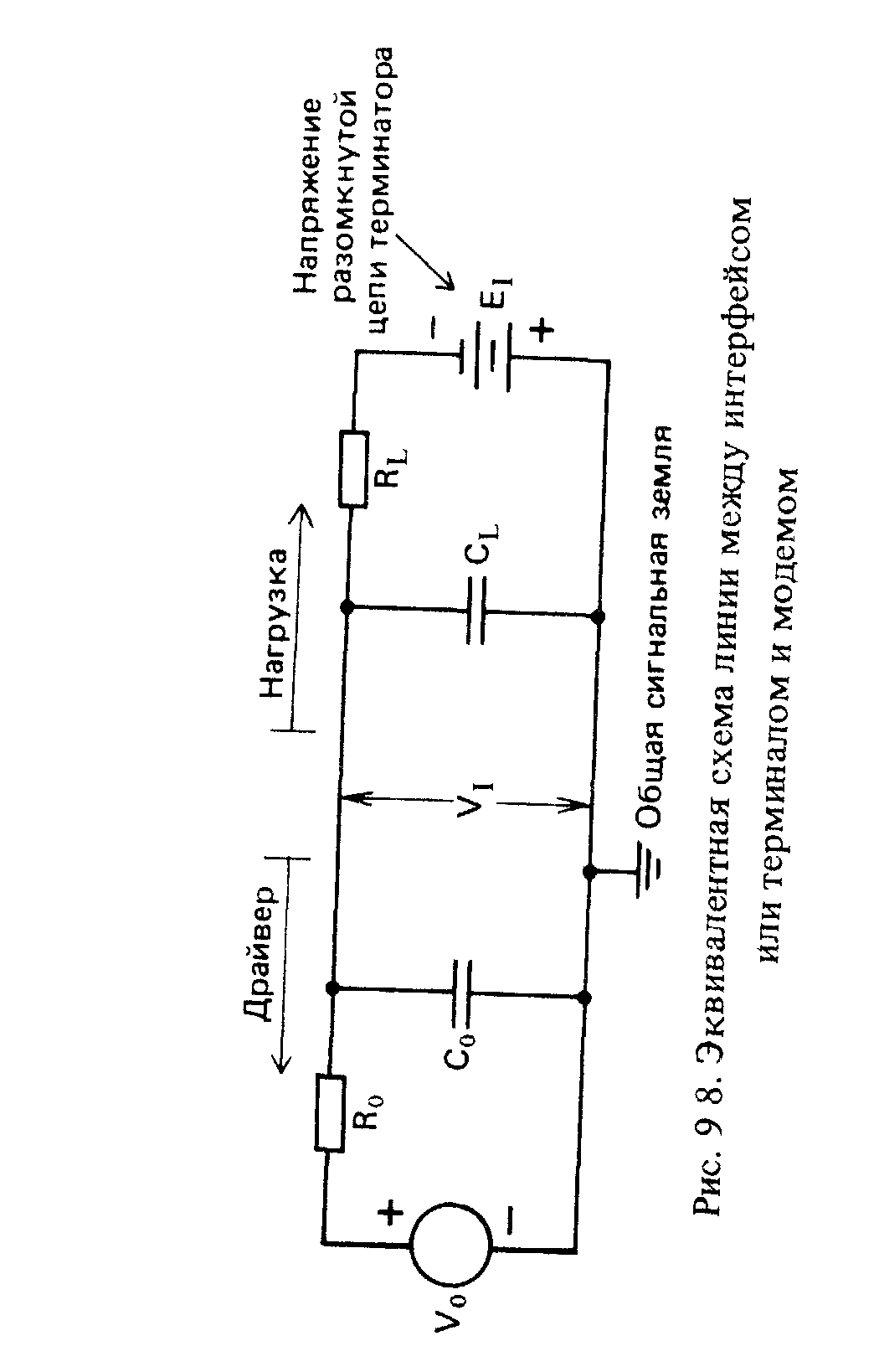

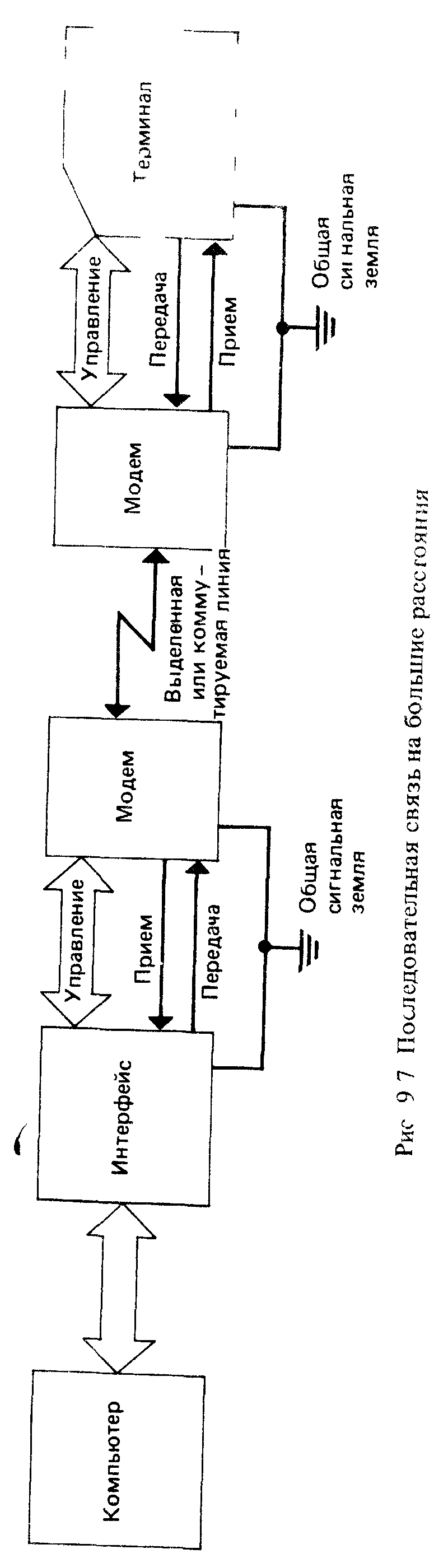

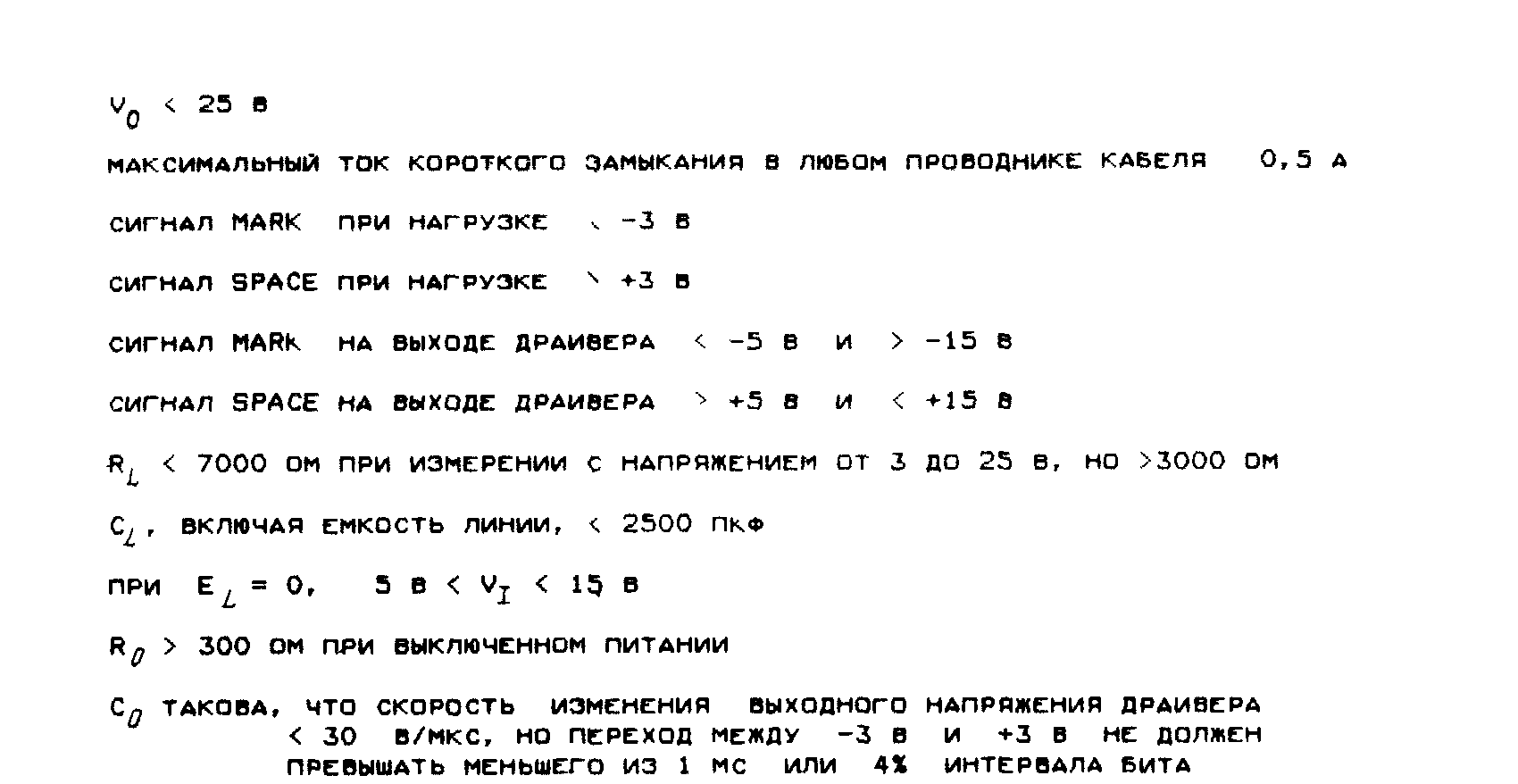

Подключение блоков памяти С этой целью память выполняется в виде двух банков (рис. 5) младшего, подключаемого к линиям данных D7 — DO и содержащего байты с четными адресами (А0 = 0), и старшего, соединенного с D15 — D8 и содержащего байты с нечетными адресами (А0=1). Чтобы каждое слово передавалось за один цикл шины, слова располагают только с четных адресов. Напомним, что адресная линия АО совместно с линией разрешения старшего банка ВНЕ обеспечивает следующие варианты пересылок по шине данных: А0 = 0, ВНЕ = 0 — пересылается слово; А0 = 0, ВНЕ = 1 —пересылается только младший байт: A0 = l, BHE = 0 — пересылается только старший байт; А0 = 1, ВНЕ = 1 —устройство не выбрано. Выработка сигнала ВНЕ и указанный порядок пересылок реализуются микропроцессором автоматически. При чтении из ЗУ в любом случае на шину данных будет подаваться слово, из которого МП при необходимости выберет требуемый байт и поместит его в регистр, указанный в выполняемой команде. Поэтому сигналы ВНЕ и АО на ПЗУ не подаются. При записи в ЗУ необходимо различать старший и младший байты (иначе может происходить разрушение информации, хранящейся в соседнем байте). Для этого сигналы ВНЕ и АО подаются на входы CSH и CSL выбора старшего и младшего банков ОЗУ. Процесс обращения к ПЗУ стробируется сигналом MEMR, а к ОЗУ - сигналами MEMR и MEMW, объединенными с помощью логического элемента И-НЕ. Блок ПЗУ может быть, например, выполнен на основе двух включенных параллельно БИС К573РФ4 емкостью 8 Кбайт каждая, а блок ОЗУ — на основе восьми БИС К537РУ10 емкостью 2 Кбайт каждая. Адресные входы А12 — АО каждой пары БИС соединены параллельно и подключены к адресным линиям А13 — А1. Оставшаяся свободной линия А14 используется для различения блоков ПЗУ (А14=0) и ОЗУ (А14 = 1). В общем случае для различения блоков ПЗУ и ОЗУ, а также для раздельной адресации страниц этих блоков осуществляется дешифрация старших адресных линий, например с помощью ИС К155ИД4.  рис. 5 Схема подключения блоков памяти Подключение внешних устройств При подключении внешних устройств также возникает проблема передачи слов или отдельных байтов по шине данных (ШД). К устройствам, которые осуществляют обмен байтами и поэтому подключаются к младшей или старшей половине ШД, относятся, в частности, все программируемые БИС. В этом случае отдельно дешифруются четные и нечетные адреса ВУ (рис. 6), и полученные таким образом сигналы выбора CS подаются на соответствующие входы БИС. Устройства с четными адресами подключаются к младшей половине ШД (или ко всей ШД), а устройства с нечетными адресами — к старшей половине ШД. Если, например, необходимо передавать слова с помощью БИС интерфейса К580ВВ55, то параллельно включается две такие БИС, входы, CS которых соединены с разными дешифраторами адреса. При этом имеется возможность передавать не только слова, но и отдельные байты, т. е. обращаться индивидуально к каждой БИС. Если в этом нет необходимости, то входы CS обеих БИС можно подключить к одному выходу верхнего дешифратора DC. Если в системе реализуется ввод — вывод, отображенный на память, то могут потребоваться дополнительные дешифраторы. При этом целесообразно применять биполярные программируемые ПЗУ, которые хотя и уступают дешифраторам по быстродействию, но обеспечивают полное дешифрирование многобитового адреса одной БИС. Кроме того, появляется возможность изменения адресов ввода — вывода путем замены такой ПЗУ без изменения монтажа. При использовании ВУ, ориентированных на передачу байтов, может оказаться целесообразным преобразование двухбайтовой ШД в однобайтовую. Это, в частности, требуется для организации прямого доступа к памяти с помощью БИС контроллера ПДП К580ВТ57 и для пересылки блоков данных между ЗУ и ВУ с помощью цепочечных команд. В последнем случае ввод — вывод должен быть организован с отображением на адресное пространство памяти. Устройства, подключаемые к однобайтовой шине данных, могут получать четные или нечетные адреса произвольно.  рис. 6 Интерфейс МП К1810ВМ86 с портами ввода/вывода 9 ИНТЕРФЕЙСЫ ВВОДА-ВЫВОДА Интерфейсы памяти и ввода-вывода связаны с логикой управления шиной. Между ней и интерфейсами находятся только электрические проводники шины; следовательно, интерфейсы должны быть спроектированы для передачи и приема сигналов, совместимых с логикой управления шиной и ее временной диаграммой. При наличии сходства интерфейсов памяти и ввода-вывода между ними имеются и существенные различия. В данной главе рассматриваются интерфейсы ввода-вывода, а памяти и ее интерфейсам посвящена гл. 10. Интерфейс ввода-вывода должен выполнять следующие функции: 1. Интерпретировать сигналы адреса и выбора между памятью и вводом-выводом, чтобы определить обращение к нему, и в случае такого обращения определить, к каким регистрам происходит обращение. 2. Определять, выполняется ввод или вывод; при выводе воспринять с шины выходные данные или управляющую информацию, а при вводе поместить на шину входные данные или информацию о состоянии. 3. Вводить или выводить данные в подключенное устройство ввода-вывода и преобразовывать параллельные данные в формат, воспринимаемый устройством, или наоборот. 4. Посылать сигнал готовности, когда данные восприняты или помещены на шину данных, информируя процессор о завершении передачи. 5. Формировать запросы прерываний и (при отсутствии в логике управления шиной управления приоритетными прерываниями) принимать подтверждения прерываний и - выдавать тип прерывания. 6. Принимать сигнал сброса и реинициализировать себя и, возможно, подключенное Устройство.  Рис. 9.1. Схема типичного интерфейса ввода-вывода Схема типичного интерфейса ввода-вывода показана на рис. 9.1. Главные функции интерфейса сводятся к преобразованию сигналов между системной шиной и устройством ввода-вывода и реализации буферов, необходимых для удовлетворения двух наборов временных ограничений. Значительная часть функций интерфейса выполняется блоком, находящимся на рисунке справа. Часто он реализуется в виде микросхемы, но иногда функции этого блока могут быть разбросаны по нескольким приборам. Очевидно, его функции полностью определяются устройством ввода-вывода, с которым должен взаимодействовать интерфейс. Интерфейс можно разделить на две части, взаимодействующие с устройством и с системной шиной. Первая из них определяется'устройством, а вторые части всех интерфейсов в данной системе довольно похожи, так как они связаны с одной и той же шиной. В них должны быть шинные драйверы и приемники, схемы преобразования интерфейсных сигналов управления в соответствующие квитирующие сигналы и схемы для дешифрирования появляющихся на шине адресов. В системах с микропроцессорами 8086/8088 подключение к шине данных можно осуществить приемопередатчиками 8286, которые применяются и в логике управления шиной. Однако основные интерфейсные устройства имеют встроенные драйверы и приемники, которых достаточно в небольших, одноплатных системах. Логику квитирования нельзя спроектировать, не зная управляющих сигналов, необ-ходимых основному интерфейсному устройству, а эти сигналы в различных интерфейсах варьируются. Обычно эта логика должна воспринимать сигналы считывания/записи, определяющие направление передачи, и выдавать для микросхем 8286 сигналы ОЕ и Т. В максимальном режиме в нее подаются сигналы lOWC (или AIOWC) и ХЖС от контроллера шины, а в минимальном режиме — сигналы RD, WR и М/Ю (или IO/M) . Через эту логику должны также проходить линии запроса прерывания, готовности и сброса. Иногда управляющие линии шины проходят через логику квитирования неизменными (т. е. подключаются прямо к основному интерфейсному устройству) . Дешифратор адреса должен принимать адрес и, возможно, бит, показывающий нахождение адреса в адресном пространстве ввода-вывода или в адресном пространства ; памяти. В системе с минимальным режимом этот бит можно взять с линии М/Ю (или Ю/М), а в системе с максимальным режимом выбор памяти или ввода-вывода определяется линиями IOWC и IORC . Когда дешифратор определяет обращение к интерфейсу, дешифратор должен выдать в основное интерфейсное устройство сигналы о том, что оно выбрано и к какому регистру производится обращение. Определяющие регистр биты могут быть младшими битами адреса, но часто они генерируются в интерфейсном устройстве из сигналов считывания/записи и адреса. Пусть, например, имеется два регистра А и В, из которых можно считывать, и два регистра С и D, в которые можно записывать. Иногда для задания регистра можно использовать сигналы считывания и записи и бит шины адреса следующим образом: Запись Считывание Бит 0 адреса Выбираемый регистр О 1 0 А О 1 1 В 1 0 0 С 1 0 1 D Если в системе вместо контроллера прерываний применяется приоритетная цепочка, в каждом интерфейсе потребуются логика цепочки (см. рис. 6.14, б) и логика формирования типа прерывания. Кроме того, интерфейс может быть связан с контроллером ПДП. Многие интерфейсы рассчитаны на обнаружение минимум двух видов ошибок. Так как связывающие интерфейс с устройством линии почти всегда подвержены помехам, при передаче информационных байт к ним обычно добавляются биты паритета. При использовании четного паритета бит паритета устанавливается так, чтобы общее число единиц, включая и бит паритета, было четным. В случае нечетного паритета число единиц должно быть нечетным. По мере приема байт осуществляется контроль паритета и при наличии ошибки устанавливается определенный бит в регистре состояния. Некоторые интерфейсы контролируют избыточные байты, которые помещаются после блоков данных. Второй вид ошибок, которые могут обнаруживать большинство интерфейсов, это ошибка перегрузки. Когда компьютер вводит данные, он считывает их из буферного регистра входных данных. Если по какой-то причине содержимое этого регистра заменяется новыми данными до того, как они введены компьютером, возникает ошибка перегрузки. Такая же ошибка возникает, когда данные помещаются в буферный регистр выходных данных до того, как в устройство передано текущее содержимое регистра. Ошибка перегрузки, как и ошибка паритета, вызывает установку определенного бита состояния. Интерфейсы можно классифицировать в соответствии со способом взаимодействия их со своими устройствами ввода-вывода. В § 9.1 рассматриваются интерфейсы таких устройств, которые передают и принимают информацию последовательно; затрону также вопрос о связи на большие расстояния; § 9.2 посвящен интерфейсам, которые взаимодействуют с устройствами в параллельном формате. В § 9.3 обсуждаются интерфейсы, обеспечивающие синхронизацию внешних или внутренних событий или подсчитывают внешние события. В § 9.4 показано проектирование интерфейса устройства с клавиатурой и индикатором. Наконец, в § 9.5, 9.6 речь идет о быстродействующей связи с обсуждением контроллеров ПДП и накопителя на гибком диске. В главу включены несколько примеров, в которых описываются интерфейсные микросхемы фирмы Intel, имеющие только восемь линий данных. Поэтому проще считать, что в примерах используется микропроцессор 8088. Микросхемы можно подключать и к 16-битной шине микропроцессора 8086, но так как в нем байты с нечетными адресами передаются по 8 старшим битам шины, в интерфейсе потребуются некоторые модификации и(или) нововведения. Поэтому в § 9.4 - 9.6 предполагается 8-битная шина микропроцессора 8088, а в § 9.7 указаны те изменения, которые необходимо осуществить при подключении устройств к 16-битной шине микропроцессора 8086. Далее, везде, кроме § 9.7, рассматривается система с минимальным режимом работы, а в § 9.7 показаны модификации, необходимые для системы с максимальным режимом работы. 9.1 ИНТЕРФЕЙСЫ ПОСЛЕДОВАТЕЛЬНОЙ СВЯЗИ Многие устройства ввода-вывода передают информацию в или из компьютера последовательно, т. е. по одному биту, по паре проводников, причем каждый бит занимает определенный временной интервал. Типичная конфигурация последовательного, интерфейса показана на рис. 9.2. Регистр состояния содержит информацию о состоянии текущей передачи (например, об ошибках), а регистр управления хранит информацию о режиме работы интерфейса. Буфер входных данных подключен к регистру сдвига с последовательным входом и параллельным выходом. В операции ввода биты по одному подаются в регистр сдвига, а после приема символа информация передается в буферный регистр входных данных и ожидает ввода в ЦП. (Обычно одним данным является буквенно-цифровой символ, который далее называется просто символом, но это не обязательно.) Буферный регистр выходных данных аналогично подключен к регистру сдвига с параллельным входом и последовательным выходом. Вывод осуществляется выдачей данных в буфер выходных данных, передачей их в регистр сдвига и последующим сдвигом данных на последовательную выходную линию. Хотя имеется несколько способов адресации четырех регистров порта, будем полагать, что из регистра состояния можно только считывать, а в регистр управления - только записывать. Следовательно, активный сигнал на линии считывания идентифицирует либо регистр состояния, либо буферный регистр входных данных, а линию АО можно использовать для различения этих регистров. Аналогично сигналы записи, и АО допускают выбор одного из остальных двух регистров. Интерфейс на рис. 9.2 имеет отдельные линии для передачи и приема информации. Когда для двух направлений сигналов применяются различные линии, связь называется дуплексной. Такая система может передавать и принимать одновременно. Терминалы и другие последовательные устройства, подключенные к компьютеру дуплексной системой, обычно посылают каждый символ в компьютер без его индикации. Компьютер сразу же посылает символ обратно (как эхо) и терминал индицирует его. Потерь времени при этом не возникает, так как эхо-символы можно передавать одновременно с вводом в компьютер новых символов. Пользователь осуществляет визуальную проверку не только того, что он ударил по правильной клавише, не и того, что компьютер получил  Рис. 9.2. Последовательный интерфейс правильный символ. В полудуплексной связи для ввода и вывода применяется одна и та же линия. Здесь напечатанный на терминале символ индицируется одновременно с передачей в компьютер и принцип эхо-печати не применяется. Если компьютер принимал символы, а затем "хочет" передавать их (или наоборот), линию связи необходимо скоммутировать, на что уходит некоторое время. Хотя дуплексная связь и не требует комму'  Рис. 9.3. Основные режимы передачи: полудуплексный (а) и дуплексный (б) тации и обеспечивает эхо-передачу, для нес нужна дополнительная линия Два рассмотренных режима связи иллюстрируются рис. 9.3. Многие терминалы и интерфейсы допускают коммутацию для полудуплексной связи и имеют отдельные контакты для души к,. ной связи.Если устройство, например принтер, требует только односторонней связи, достаточно полудуплексной связи, а коммутация не нужна. Имеются два основных вида последовательной связи. При асинхронной последовательной связи символы разделяются специальными двоичными наборами, а при сип хронной должны быть специальные символы "синхронизации" в начале каждого сообщения и специальные "холостые" символы для "заполнения времени", когда информация не передается. Асинхронная передача допускает любые промежутки между символами, а в синхронной передаче символы должны точно размещаться, даже если некоторые символы не содержат информации. Максимальная скорость передачи информации синхронной линии выше, чем асинхронной линии с той же двоичной скоростью, так как при асинхронной передаче каждый символ содержит дополнительные биты. С другой стороны, частоты синхронизации передатчика и приемника могут быть не точно одинаковыми (пока они находятся в допустимых пределах) , так как специальные наборы допускают ресинхронизацию в начале каждого символа. При синхронной передаче действия должны быть синхронными, так как именно это определяет положение каждого бита. Следовательно, помимо данных требуется передавать сигналы синхронизации. 9.1.1 Асинхронная связь Формат асинхронного символа на рис. 9.4 показывает, что символ содержит закодированную информацию и несколько дополнительных бит. До начала передачи символа линия должна находиться в состоянии 1, которое часто называется состоянием маркера Переход из этого состояния в состояние 0, или пробел, отмечает начало символа. Первый бит всегда содержит 0 и называется стартовым битом. Затем следуют 5-8 информационных битов, первым из которых является младший бит символа. После информационных бит находится необязательный бит четного или нечетного паритета. Число последних стоповых бит может быть 1, Г/2 или 2. Хотя число информационных бит, тип паритета (если он есть) и число стоповых бит могут изменяться от одной передачи (т. е. последовательности символов) к другой, эти параметры в одной передаче являются константами. В некоторых интерфейсах параметры программируются с помощью регистров управления, а в других определяются положениями переключателей. Если параметры программируются, в интерфейсе появляется регистр управления, аналогичный показанному на рис. 9.5. В нем биты 0 и 1 определяют  Рис. 9.4. Формат стандартной асинхронной передачи  Рис. 9.5. Типичный регистр управления для определения формата символа число сюпивых биг, биты 2 и 3 - число информационных бит, а бит 4 показывает наличие или отсутствие бита паритета. Если бит 4 содержит 1, бит 5 определяет тип паритета. В передатчике необходим генератор синхронизации, определяющий интервал каждого бита посредством регулирования временных огрезков между сдвигами в регистрах сдвига. После выдвигания всех бит передатчик обычно выводит маркер, пока не будет готов к передаче следующий символ. В приемнике также необходим генератор синхронизации для измерения интервала между сдвигами, так чтобы входной сигнал опрашивался в правильные моменты. Обычно частоты генераторов в 16, 32 или 64 раза больше двоичной частоты. Если множитель равен 16, после обнаружения перехода 1-0 в начале , символа приемник должен отсчитать 8 импульсов синхронизации и опросить вход. При обнаружении 0 он считаем, что переход вызван стартовым битом, а не помехой. Затем, приемник опрашивает вход через интервалы в 16 периодов импульсов синхронизации до ввода всех бит символа, включая и стоповые биты, после чего он прекращает опрос и ожидает следующего перехода 1-0. Важно отметить, что ЦП не выдает и не принимает стартовый и столовый биты, а также бит паритета. При выводе передатчик вводит эти биты в каждый символ, а при вводе приемник удаляет их из принятых данных. Такой формат позволяет передатчику вводить между символами промежутки любой : длины, а приемнику ресинхронизировать себя в начале каждого символа. Без этого механизма ресинхронизации два генератора выйду из режима синхронизации и приемник будет опрашивать вход неправильно. При наличии ресинхронизации приемник должен учитывать скорость передачи бит только для одного символа. Неправильный опрос возникает только тогда, когда две частоты синхронизации столь различны, что сдвиг в приемнике выполняется в неверный момент времени уже через несколько бш после стартового бита. Если же это происходит, появляется большая вероятность того, что приемник обнаружит нулевой бит на месге стопового. Когда вместо стопового бита обнаруживается 0, возникает так называемая ошибка кадра. Таким образом, большинство асинхронных последовательных интерфейсов должны обнаруживать три вида ошибок: паритета, перегрузки и кадра. Сигналы синхронизации передачи и приема, которые определяют временные соотношения в интерфейсе, не обязательно должны быть одними и теми же и не обязательно должны иметь одинаковую частоту. Но имеются очевидные достоинства в единой синхронизации для формирования всех необходимых в интерфейсе импульсов синхронизации. Рели двоичные скорости передачи и приема различны, электронные схемы uу оборот) Устройства, которые выполняют прием и передачу данных в формате рис. 9.4, пара лельно-последовательное и последовательно-параллельное преобразования и обнаруживают ошибки паритета, перегрузки и кадра, называются универсальными асинхронным приемопередатчиками (УАПП или UART). Многие фирмы выпускают микросхемы УАПП и их разработки стандартизованы. Усилия фирм, выпускающих микропроцессоры, направлены на разработки законченных и универсальных интерфейсов. Иногда УАПП является только небольшой частью интерфейса, который может реализовать большинство видов связи. 9.1.2 Синхронная связь Передаваемый синхронно символ также состоит из 5-8 бит с необязательным битом паритета, но не имеет стартового и стоповых бит. Все символы содержат одинаковое число бит n и время передачи разделяется на интервалы из n бит каждый. Опросом р приемнике управляет та же самая синхронизация, которая применяется для генерирования бит, что гарантирует синхронность двух процессов. Передатчик должен передавать символ в течение каждого n-битного интервала. Если символ к началу интервала отсутствует, возникает недогрузка и передатчик вводит холостой символ. В зависимости от системы приемник может интерпретировать холостые символы как ошибки недогрузки. Проблемы запуска или коммутации в асинхронной системе не существует, так как передатчик просто выдает в линию маркер до готовности начала передачи. Если помеха вызывает случайный переход 1-0, фиксируется ложный сигнал, когда первый опрос не обнаруживает стартового бита, и система ожидает следующего перехода 1-0. В синхронной передаче проблема запуска после включения или другого нарушения оказывается более сложной. Все передачи должны начинаться с серии символов синхронизации, которые нельзя спутать с другими символами. Обычно они совпадают с холостыми символами в коде ASCII символ синхронизации кодируется как 0010110. Приемник, который должен знать код символа синхронизации, проверяет каждый бит по мере его появления и, когда последовательность бит точно соответствует битам в символе синхронизации, полагает, что началась передача. Затем он считает следующие символы передаваемой информацией или пытается соотнести один или несколько из них с символом синхронизации. Так как помеха может вызвать ложную идентификацию символа синхронизации, в большинстве систем требуется, чтобы передача начиналась серией символов синхронизации. В этом случае приемник не фиксирует начала передачи до поступления нужного числа символов синхронизации. Ненужные холостые символы и символы синхронизации удаляет приемник или программа ввода. Допускается программирование числа информационных бит, наличия и вида паритета, числа и кодов символов синхронизации. В интерфейсе потребуются специальные регистры для хранения символа синхронизации и другой информации о формате. 9.1.3 Стандарты физической связи Все более широкое применение компьютеров требует оборудования, обеспечивающего связь человек — компьютер и компьютер — компьютер на длинные и короткие расстояния. Так как в этом вопросе смыкаются интересы фирм, производящих телефонное и связное оборудование и компьютеры, были установлены некоторые определения и стандарты. Они касаются, в основном трех аспектов: скорости передачи, электрических характеристик, определения и обозначения линий. Скорости передачи измеряются в битах (в секунду (hps) и в бодах; бод это число дискретных \иювий, передаваемых в одну секунду Если в любой момент времени может быть только одно из двух возможных условий обе cкopocти совпадаю! Такая ситуация характерна для машинных интерфейсов, так как они обычно вводят и выводят только единицы и нули; поэтому в данной книге оба термина считаются синонимами. Но следует отметить, что многие линии связи допускают в каждый момент одно из четырех или более условий. Например, сигнал с фазовой модуляцией может иметь одну из 4 фаз; тогда каждая фаза представляет собой два бита и скорость передачи в битах в секунду оказывается в два раза выше скорости в бодах. Наиболее широко применяются следующие стандартные скорости передачи в бодах: 110, 300, 600, 1200, 1800, 2400, 4800, 9600 и 19 200. Большинство терминалов с дисплеем могут работать с любой из этих скоростей вплоть до 9600 бод, а терминалы с принтерами ограничены быстродействием печатающего механизма. Пишущие машинки обеспечивают скорость 110 бод, а некоторые точечно-матричные принтеры могут принимать до 2400 бод. В большинстве интерфейсов скорости передачи и приема устанавливаются раздельно и часто эти скорости программируются. В качестве примера рассмотрим асинхронную передачу, в которой каждый символ состоит из стартового бита, 7 информационных бит, бита паритета и одного стопового бита. Если скорость передачи линии равна 1200 бод, то максимальное число символов, которое она может передать в секунду, равно 1200/10 = 120. Максимальная скорость достигается только при отсутствии промежутков между символами. Синхронная же линия со скоростью 1200 бод и без паритета может передать 4 символа синхронизации и сообщение из 100 символов за время 7(100+4)/1200= 0,6067 с Следовательно, за секунду можно передать 100/0,6067 = 165 информационных символов. Стандарты на электрические характеристики и определения линий устанавливают в основном две организации: внутренние — Ассоциация Электрической Промышленности (EIA), и международные — Международный Консультативный Комитет по Телефонии и Телеграфии (CCITT), являющийся подразделением ООН. Наибольший интерес для нас представляет стандарт RS-232-C, аналогичный стандарту CCITT V.24. Он регламентирует передачу последовательных двоичных потоков между интерфейсами или терминалами и связным оборудованием. Расстояние, на которое можно передать выходной двоичный поток интерфейса или терминала до появления серьезных искажений, зависит от скорости передачи и электрических характеристик линии связи. Типичная зависимость, показывающая максимальное расстояние как функцию скорости передачи для несбалансированной экранированной пары с погонной емкостью 55 пкф/м, приведена на рис. 9.6. Видно, что максимальное расстояние быстро уменьшается при скорости выше 1000 бод; при скорости 9600 бод оно составляет около 125 м. Если рабочая точка находится ниже кривой на рис. 9.6, связного оборудования не требуется и дуплексное соединение может состоять из трех проводников передающая линия, приемная линия и общая сигнальная земля. Если рабочая точка находится выше кривой, необходимо применять связное оборудование, как показано на рис. 9.7. С обеих сторон линии связи располагаются аналогичные устройства для модуляции бит, подаваемых в линию, и демодуляции бит, приходящих из линии. Такие устройства модулятор/демодулятор называют модемами. Обычно линией связи служит телефонная линия, которая может быть прямой (или выделенной) или коммутируемой. Эквивалентная схема одной из линий между интерфейсами или терминалом и модемом показана на рис. 9.8. Электрические параметры RS-232-C определены в терминах     Рис. 9.9. Основные электрические параметры интерфейса RS-232-C этой схемы и представлены на рис. 9.9. Если интерфейс или терминал передают информацию в модем, они считаются драйвером, а модем - нагрузкой; при приеме информации их роли меняются. В любом случае различные компоненты эквивалентной схемы должны удовлетворять спецификациям, сформулированным на рис. 9.9. Отметим, что сигналы данных инвертированы в том смысле, что 1 представляется меньшим напряжением, чем 0. Что представляет собой драйвер для вывода данных: часть основного интерфейсного устройства или отдельную схему, зависит от интерфейса и длины линии. На рис. 9.10 показана схема преобразования сигналов ТТЛ-уровней и стандарта RS-232-C. |