|

|

Лекции по ВМСС. Конспект лекций по курсу "Электронные вычислительные машины, системы и сети"

Лекция Программируемый периферийный интерфейс

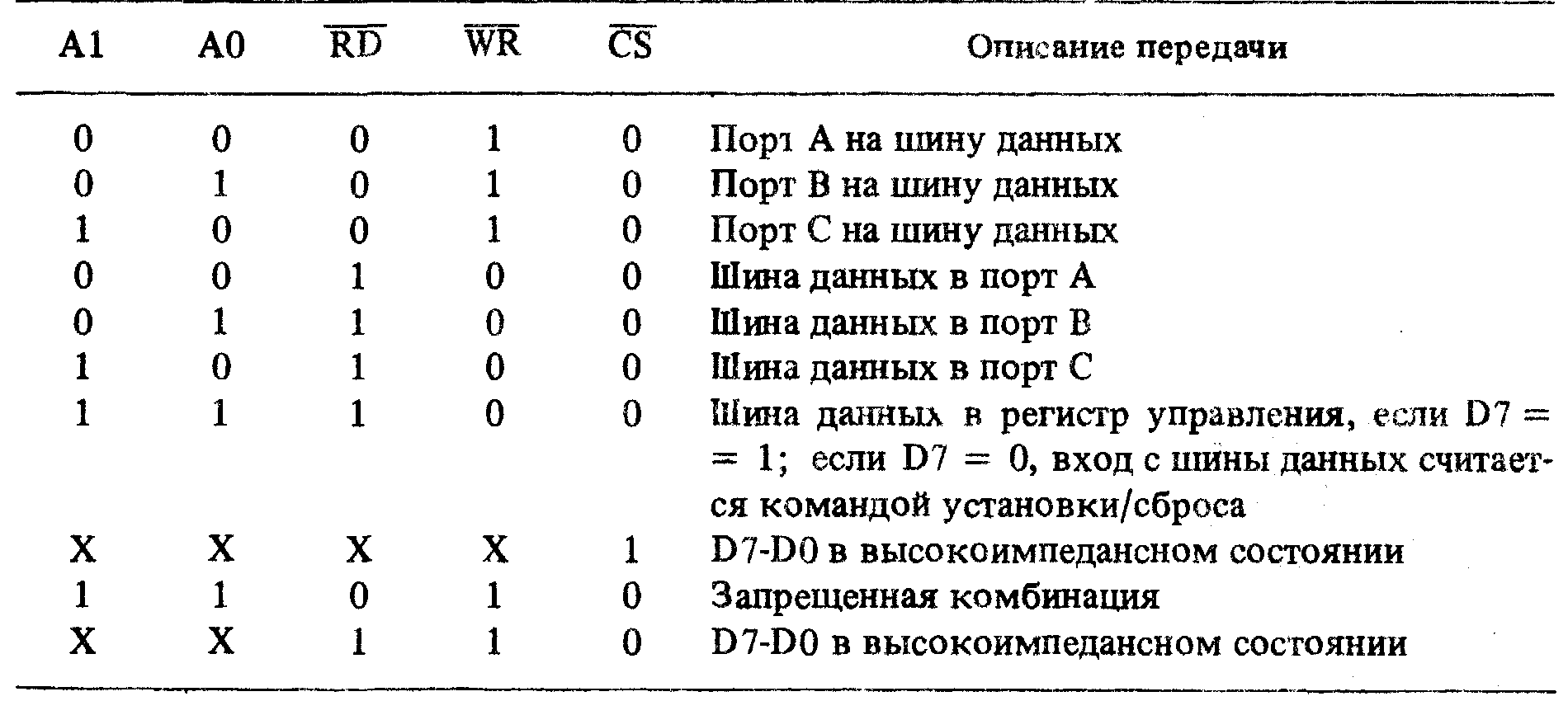

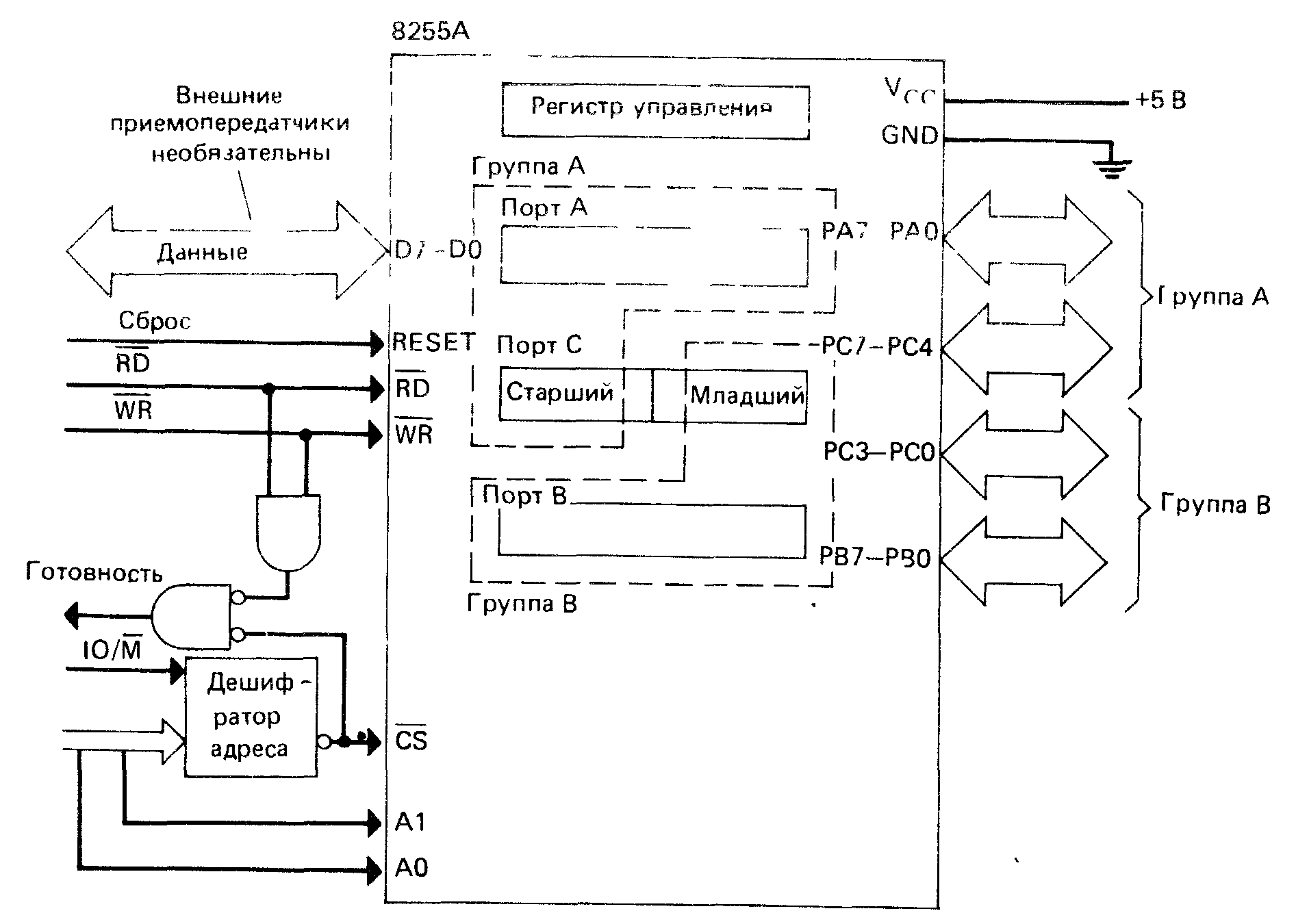

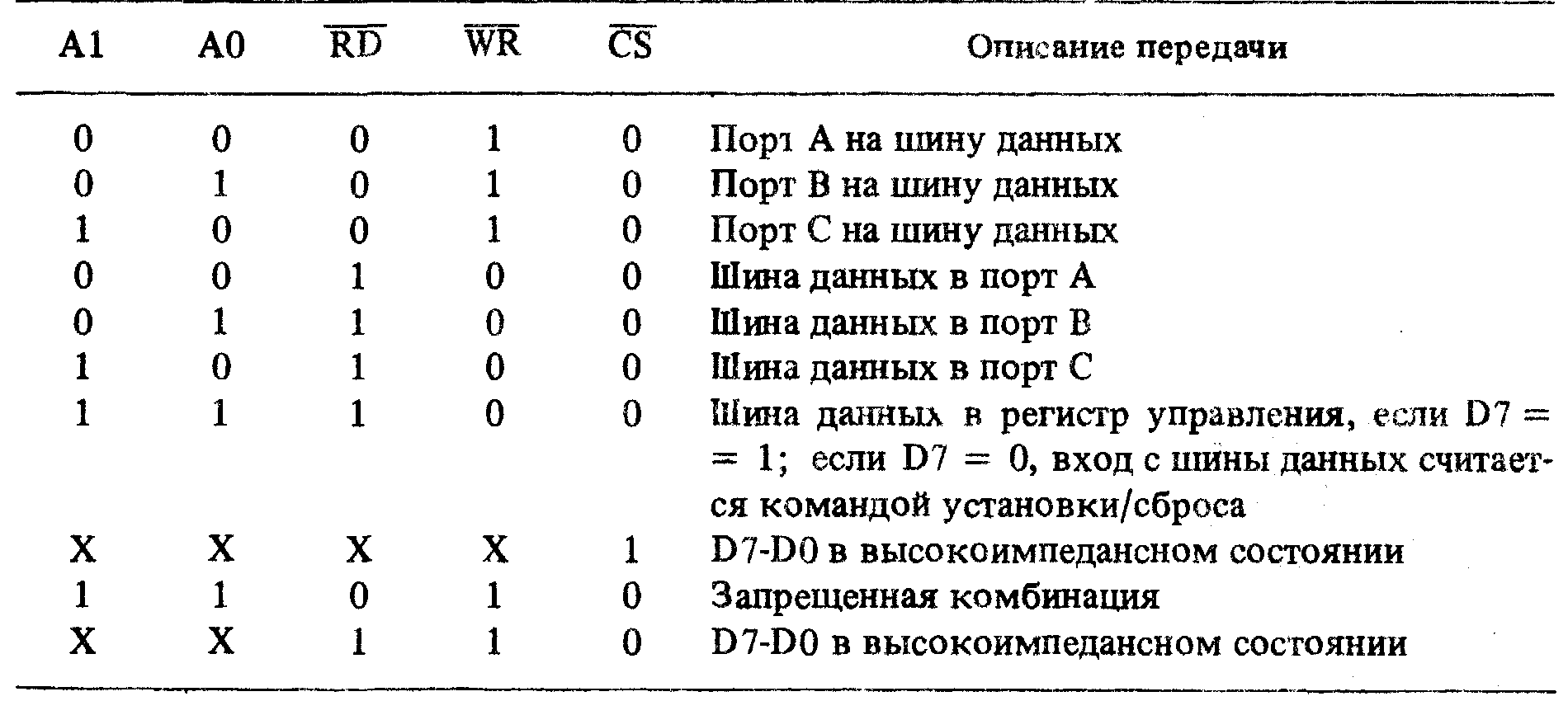

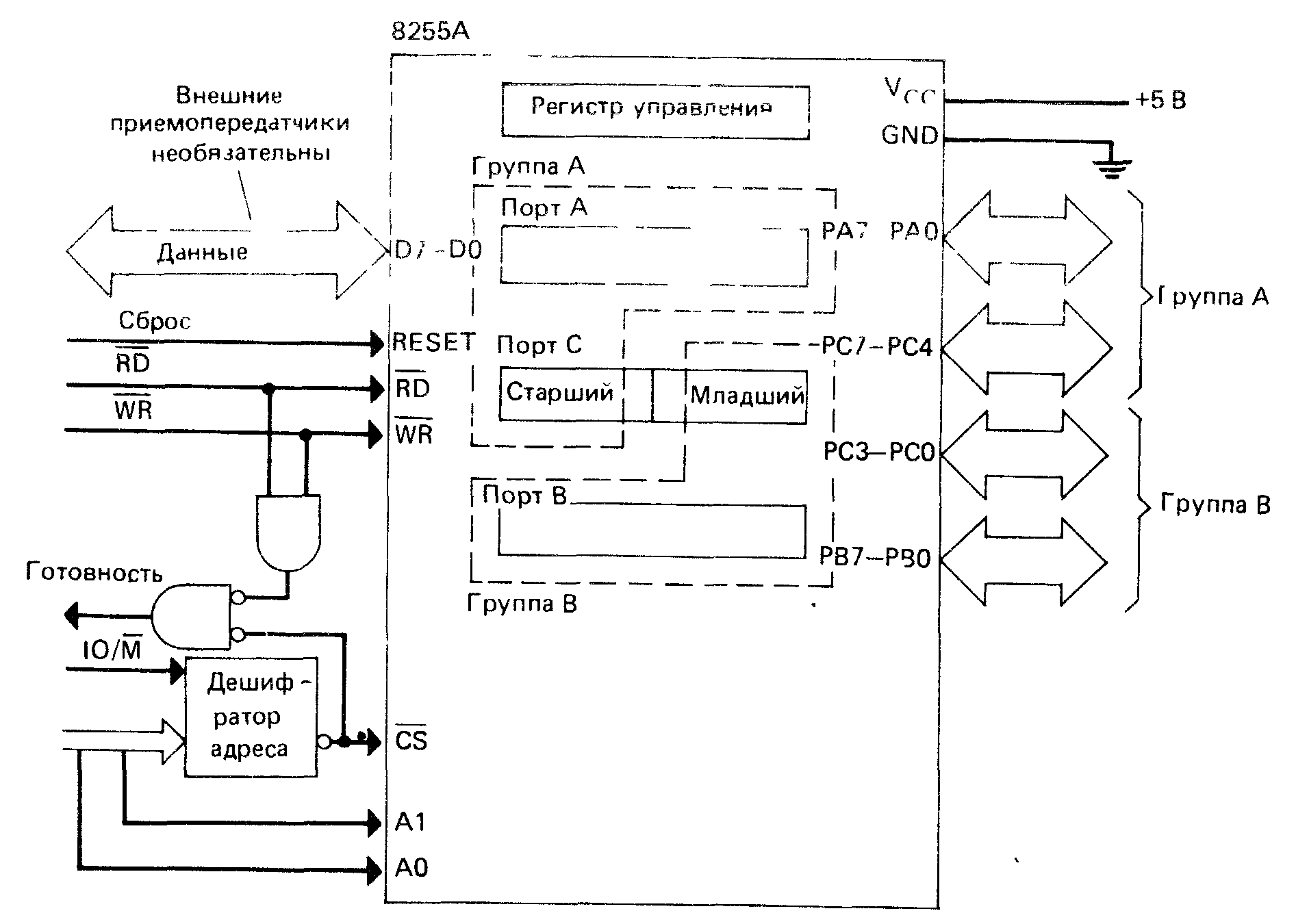

Примером параллельного интерфейса служит микросхема 8255А программируемого периферийного интерфейса. Как показано на рис. 9.21, она имеет регистр управления и три отдельно адресуемых порта А, 3 и С. Обращение к 8255А определяет сигнал CS, а направление обращения - сигналы RD и WR\ Адресуемый регистр определяют сигналы на входах А1 и АО. Следовательно, младший адрес порта, назначаемый 8255А, должен быть кратным 4. Полная адресация 8 25 5 А содержится в табл 9.2

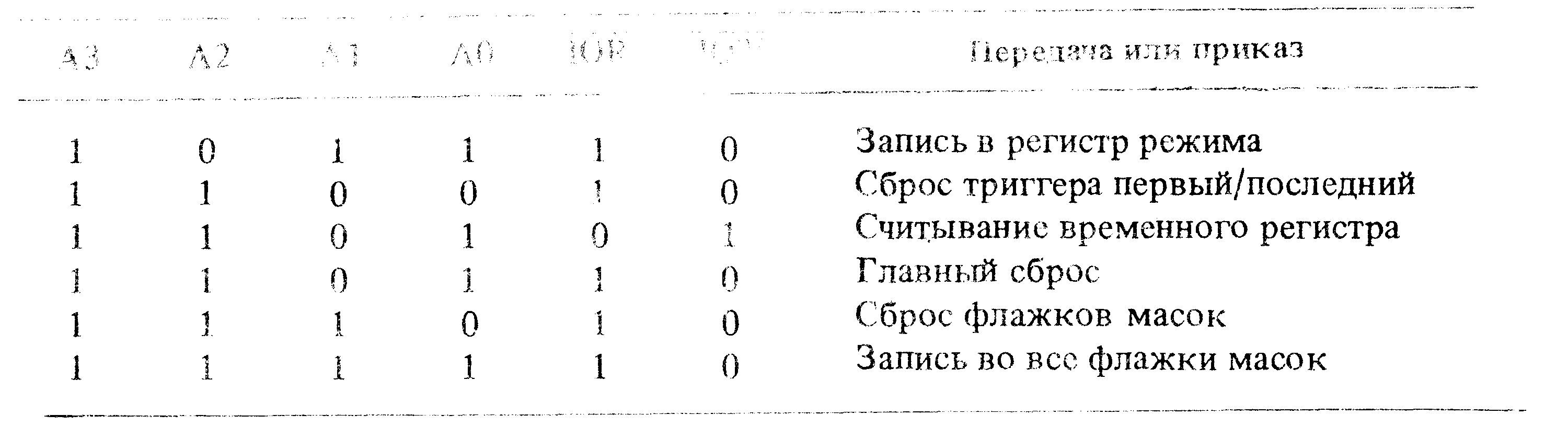

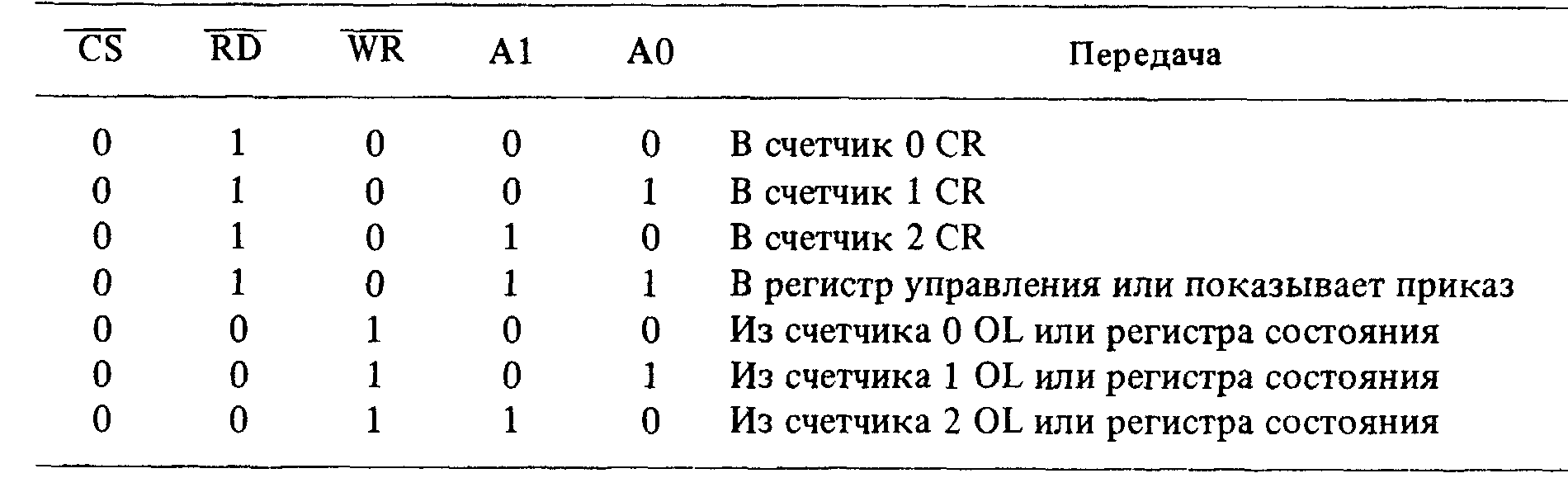

Таблица 9.2

Адресация микросхемы 8255А

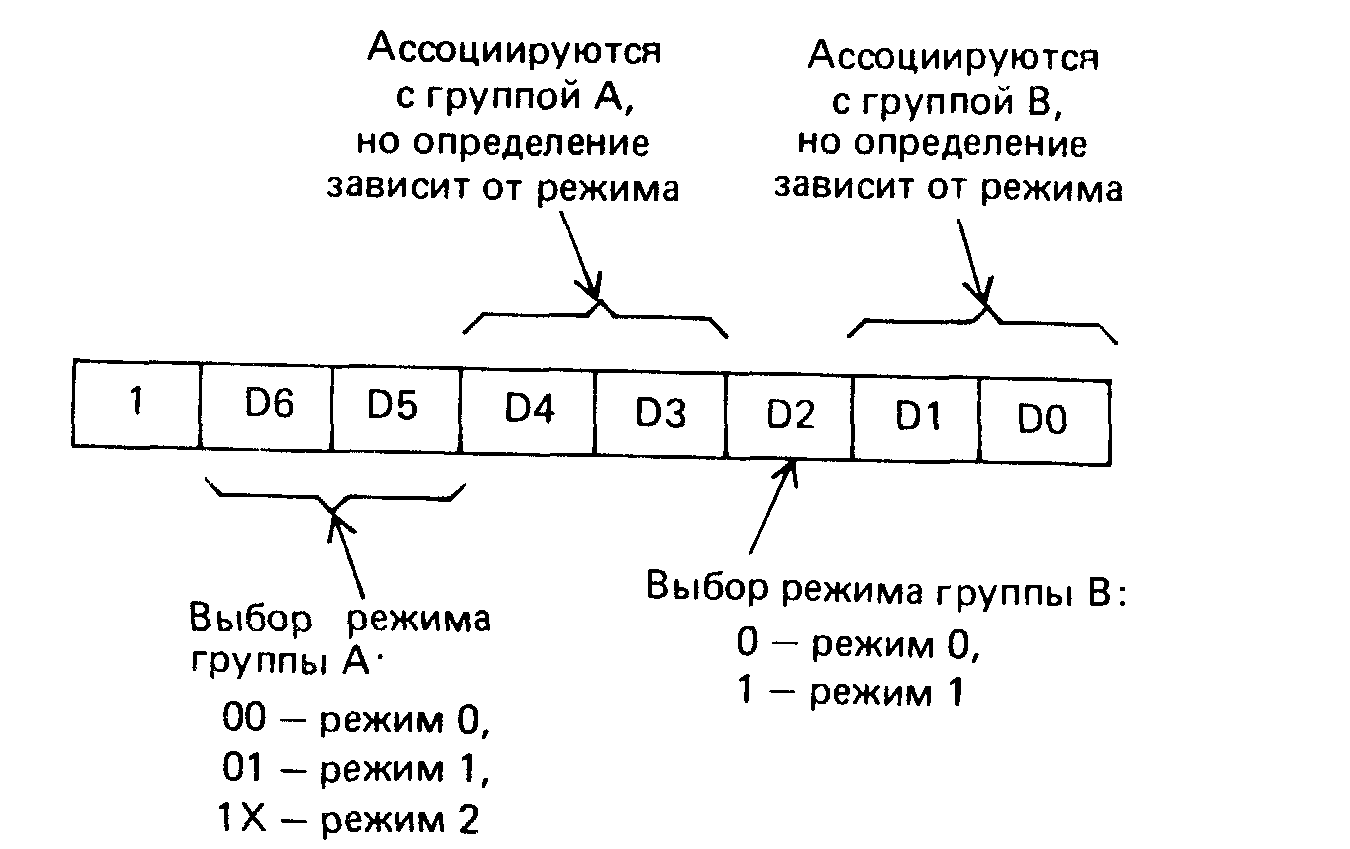

Так как биты порта С иногда используются как биты управления, 8 25 5 А спроектирован так, что в них можно выводить по отдельности, пользуясь командой установки/сброса. Когда 8255А принимает байт, направляемый в его регистр управления, он анализирует бит 7 данных. Если этот бит содержит 1, данные передаются в регистр управления; если же бит 7=0, данные считаются командой установки/сброса и применяются для установки или сброса определяемого командой бита порта С, Биты 3-1 дают номер изменяемого бита, а бит 0 показывает сброс или установку. Остальные биты не используются.

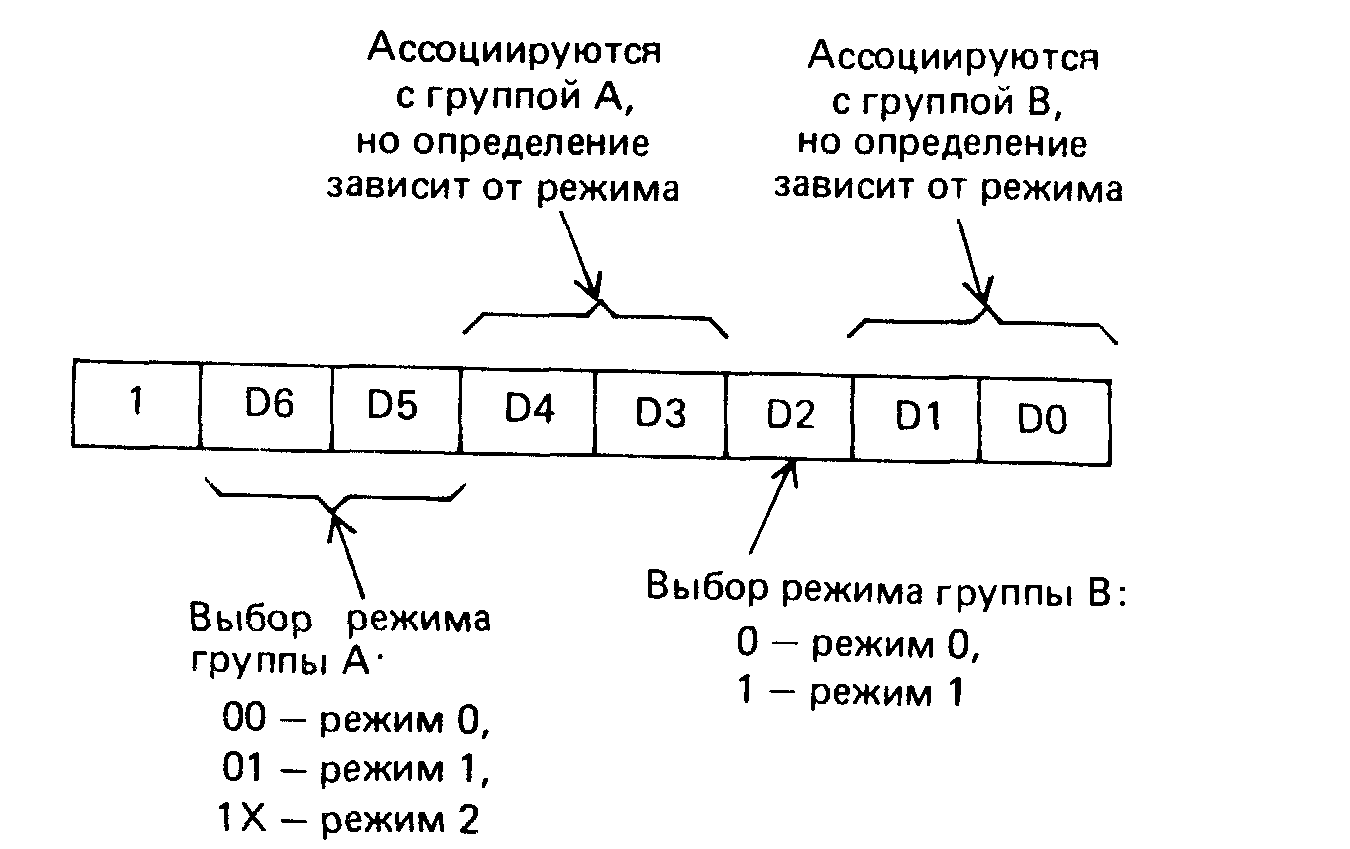

Биты трех портов выведены на контакты, которые подключаются к устройству ввода-вывода. Они разделены на группы А и В, причем группу А образуют биты порта А и 4 старших бита порта С, а группу В - порт В и 4 младших бита порта С. Группа А может работать в трех режимах (О, 1, 2), а группа В - в двух режимах (0 и 1). Режимы определяются содержимым регистра управления, формат которого приведен на рис. 9.22.

Рис. 9.21. Схема интерфейса 8255А

Режим 0. В этом режиме группа разделяется на два набора. В группе А этими набора ми являются порт А и старшие 4 бита порта С, а в группе В - порт В и младшие биты порта С. Каждый набор можно использовать для ввода или вывода, но не для двунаправленных передач. Биты D4, D3, D1 и DO в регистре управления определяют, какие наборы предназначены для ввода, а какие - для вывода. Эти биты ассоциируются с наборами следующим образом:

Рис. 9 22. Формат регистра управления микросхемы 8255А

D4 iiopi A

D3 старшая половина порта С,

D1 - порт В,

DO - младшая половина порта С

Если бит содержит 0, соответствующий набор применяется для вывода, а в противном случае для ввода

Режим 1. Когда в этом режиме работаем группа порт А используется для ввода или вывода в соответствии с битом D4 (D4 =- 1 указывает ввод), d старшая половина порта С применяется для сигналов квитирования и управления.

При вводе старшим битам пота С назначены следующие названия и определения-

РС4 STB^ - сигнал 0 на этом контакте заставляет РА7-РАО "стробироваться" в порт А.

РС5 1ВРд — показывает, что входной буфер заполнен. Устанавливается в 1, когда порт А содержит данные, которые еще не введены в процессор. Когда действует сигнал 0, устройство может вводить в интерфейс новый байт.

РС6,РС7 - применяются для вывода сигналов управления в устройство или ввода состояния из устройства. Если бит D3 в регистре управления содержит 0, эти линии выходные; в противном случае - входные. При выводе:

РС4,РС5 - выполняют те же функции, что и РС6, РС7 при вводе.

РС7 ОВРд - показывает, что выходной буфер заполнен. Формирует сигнал 0 в устройство, когда порт А выводит в устройство новые данные.

РС6 АСКд - устройство подает 0 на этот вход, когда оно восприняло данные из порта А.

В режиме 1 с группой А ассоциируется РСЗ, обозначаемый INTRn. Этот сигнал применяется как линия запроса прерывания и подключается к одной из линий IR системной шины. При вводе в порт А на этом выходе формируется сигнал 1, когда новые данные помещаются в порт А (т. е. им управляет РС4), и сигнал 0, когда процессор считывает данные. При выводе на выходе INTRn формируется сигнал 1, когда содержимое порта А воспринято устройством, и сигнал 0, когда процессор загружает новые данные. Если группа В находится в режиме 1, порт В является входным или выходным в зависимости от состояния бита D1 регистра управления (D1 = 1 определяет порт В входным). При вводе РС2 и РС1 обозначаются STBo и IBFg; они выполняют для группы В те же функции, что и сигналы STBn и 1ВРд для группы А. Аналогично при выводе РС1 и РС2 обозначаются OBFg и АСК„. Выход РСО превращается в INTRg и используется аналогично ' INTR^. Разрешением прерываний для группы А управляют РС4 в режиме ввода и РС6 в режиме вывода. Например, в режиме ввода прерывание для группы А разрешается установкой РС4 и запрещается сбросом РС4 с помощью команды установки/сброса. Аналогично разрешением прерываний для группы В управляет установка/сброс РС2.

Режим 2. В данном режиме может работать только группа А, хотя в ней для генерирования запросов прерываний используется РСЗ. В режиме 2 порт А становится двунаправленным, а 4 старших бита порта С определяются следующим образом:

< РС4 STB* - сигнал 0 на этой линии заставляет данные с РА7-РАО стробироваться в порт А.

РС5 1ВРд - формируется сигнал 1, когда в порт А загружаются новые данные 1 с линий РА7-РАО, и сигнал 0, когда процессор считывает данные. РС6 АСКд - показывает, что устройство готово воспринимать данные с линий ;РА7-РАО.

w "i Jbt д формирует сигнал , » i^i ,р >це (.ор 3ii р) лш. в иор1 А ио^ s данные., и с й''нал d, когда данные принягы устройством.

Когда гpyппа А находится в режиме 2, группа В может работать в peжиме О или 1 если группа В находится в режима 0 только РС2 РГО можно использовать для ввода или вывода, ».>к к» к Р*'3 лужи! запросом прерываний л ^>i р^ппы \ Обычно ei то птш A pd6oi4ti з режиме \ РС2 РГО по гклю »йе1ся к контактам управления и < остояния ' i po^tiai. коюр<\> ik/. соединено к ;'я:иям fit рта А Для эт.^л же целей мижч тоимеьять "я порт В

Во всех тех режимах порт С отражает сигналы на линиях РС7-РСО и его можно считать командой WR.

9 2.2 Пример использования

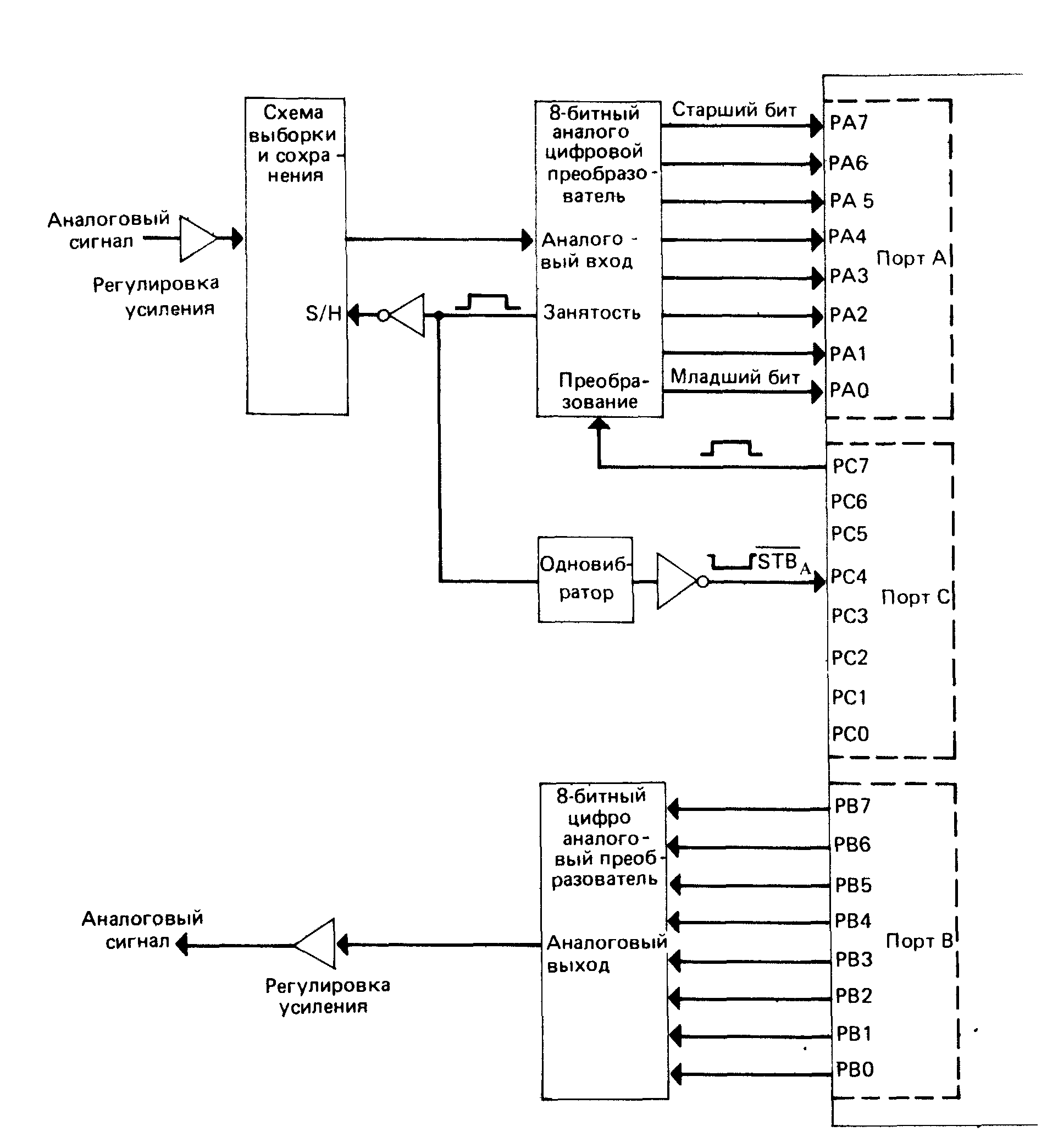

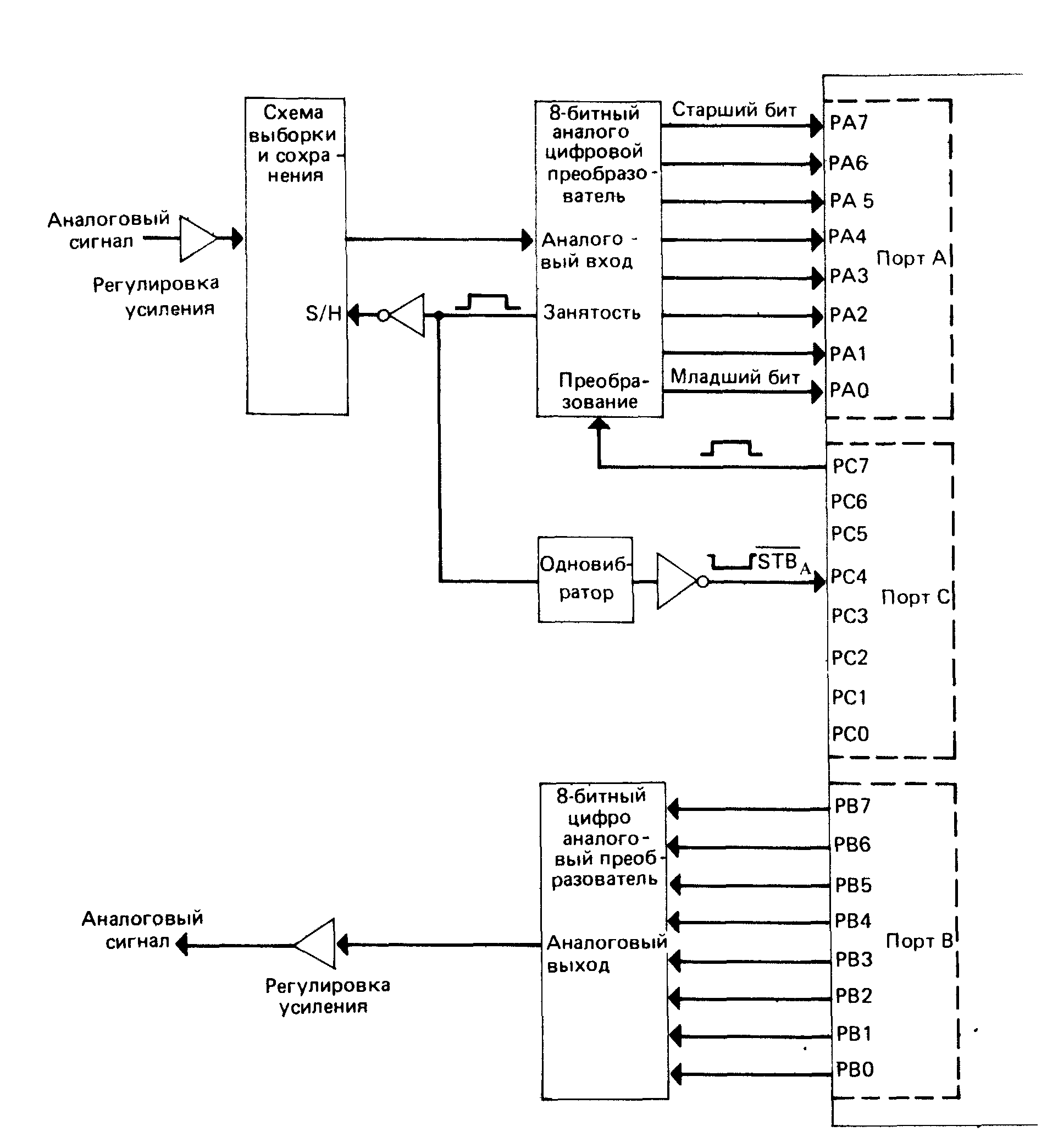

На рис. 9.23 показано возможное подключение микросхемы 8255А к аналого-цифровой и цифро-аналоговой подсистемам. Так во время аналого-цифрового преобразования аналоговое напряжение должно оставаться неизменным, необходима схема выборки i-го сохранения. Группа А работает на ввод в режиме 1. Преобразование инициируется сигналом на выходе РС7, это стимулирует преобразователь выдать сигнал занятости. Линия занятости подключена на .вход управления выборкой и сохранением (S/H) я на вход одновибратора, запускаемого спадающим фронтом. Пока сигнал занятости имеет высокий уровень, схема выборки и сохранения поддерживает постоянный выход, а когда в конце преобразования сигнал занятости снимается, запускается одновибратор. Его выход инвертируется и подается на вход 8ТВд (РС4) микросхемы 825 5А. Он заставляет цифровой отсчет стробироваться в порт А. В цифро-аналоговой части подсистемы порт В работает как выходной в режиме 0; он подключен непосредственно на двоичный вход цифро-аналогового преобразователя. Квитирование здесь не применяется.

Предположим, что порты А, В и С и регистр управления имеют адреса FFF8, I FF9 FFFA и FFFB. Тогда команды

MOV AL.10110000В OUT DX,AL

заставляют порт А работать в режиме 1, порт В - в режиме 0, а РС7 быть выходом. Следующий фрагмент формирует импульс на входе запуска аналого-цифрового преобразователя.

MOV DX,OFFFBH

MOV AL,00001111B

OUT DX,AL

MOV AL,00001110B

OUT DX,AL

Здесь первая команда загружает в регистр DX адрес, ассоциируемый с командой установки/сброса, который coвпадает с адресом регистра управления Следующие две команды формируют сигнал Ю -=• 1, а последние две

сигнал РС7 = 0. Фрагмент программного ввода преобразованных данных имеет вид

MOV DX.OFFFAH AGAIN: IN AL,DX

TEST A L.,001 OOOOOB JZ AGAIN MOV DX.OFFF8H IN AL,DX

Рис. 9.23. Интерфейс аналого-цифровой и цифро-аналоговой подсистем с применением микросхемы 8255А

Для вывода байта из регистра AL в цифро-аналоговый преобразователь требуются только две команды.

MOV DX.OFFF9H

OUT DX,AL

Как только байт появляется в порту В, его биты сразу подаются на входы цифро-аналогового преобразователя, который в свою очередь сразу же преобразует их в аналоговый сигнал.

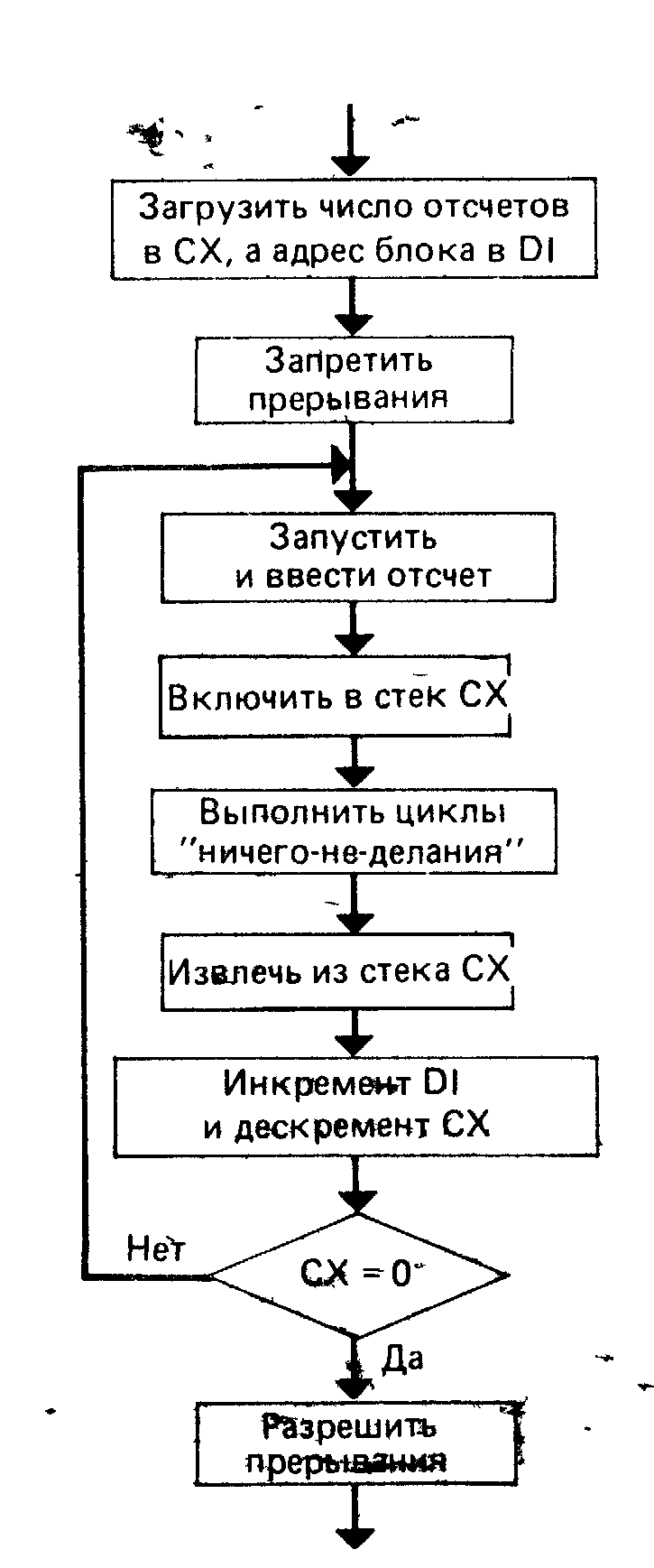

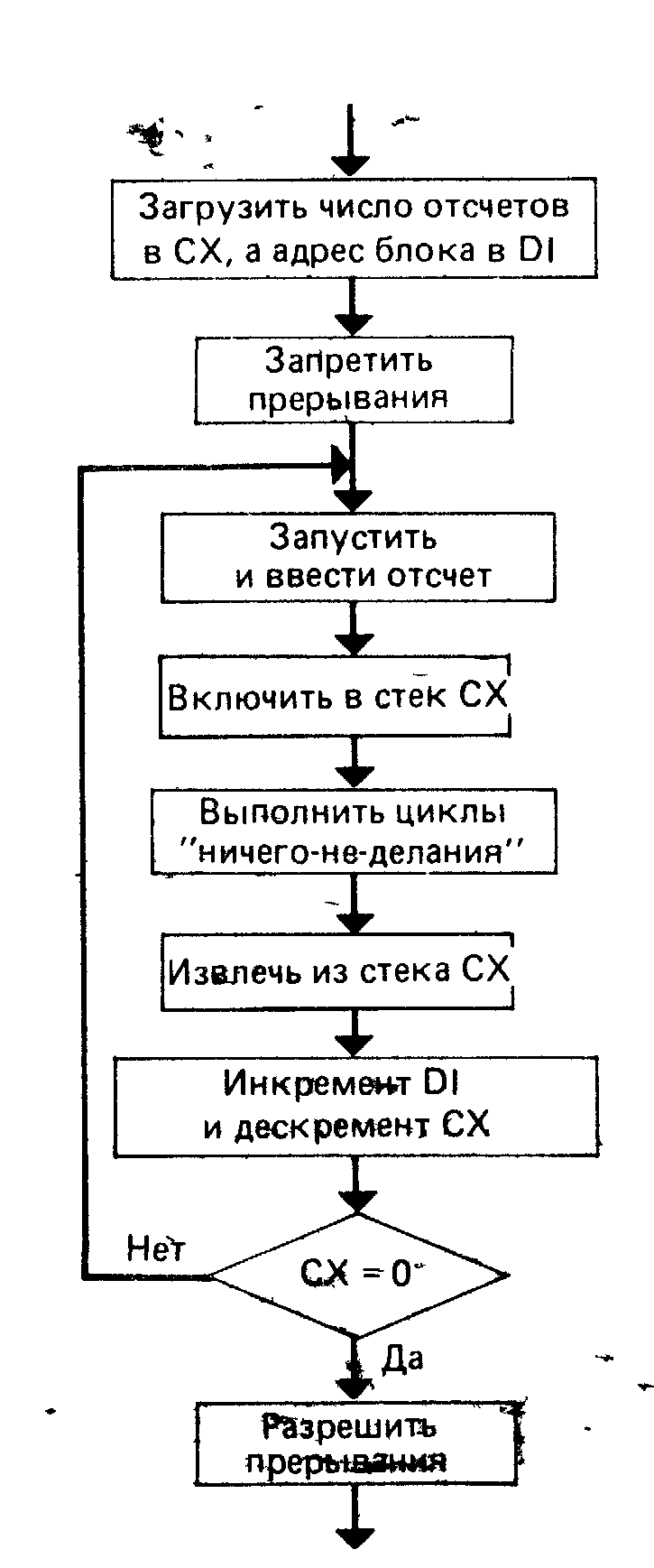

В данном примере предполагается, что синхронизация преобразований осуществляется программой и что коэффициенты усиления входного и выходного аналоговых усилителей регулируются. Чтобы получить от программы равномерное распределение входных и выходных отсчетов, необходимо учитывать времена выполнения команд. Между

отсчетами выполняются одни и те же команды и общее время их выполнения точно известно Прерыва-ния необходимо запретить, так как они случайным образом вводят выполнение разного числа команд Интервал между отсчетами можно скорректировав с помощью цикла "ничего-не-делания", например

MOV CX,N IDLE NOP

LOOP IDLE

между вводами или выводами. Схема ввода с программной синхронизацией отсчетов аналого-цифрового преобразования представлена на рис. 9.24

Часто в аналого-цифровой и цифро-аналоговой подсистеме применяются программируемые генераторы синхронизации и усилители, что позволяет более точно управлять расположением отсчетов и цифро-аналоговых выходов, а также динамически изменять усиление Кроме того, в такую подсистему часто вводят контроллер ПДП для увеличения скорости ввода и вывода.

На рис 9.23 показаны только 8-битные преобразователи, имеющие разрешающую способность 1 из 256. Если диапазон входного или выходного напряжений равен -10 . . . +10 В, разрешающая способность составляет

20/256= 0,078В.

Для улучшения разрешающей способности применяются 10-, 12- или 14-битные преобразователи. В этом случае приходится пользоваться комбинацией портов А и С или В и С (см упр. 14) или параллельно включать две микросхемы 8255А (см. § 9.7).

Лекция ПРОГРАММИРУЕМЫЕ ТАЙМЕРЫ И СЧЕТЧИКИ СОБЫТИЙ .

Довольно часто требуется устройство формирования временных интервалов для процессора и внешних устройств, подсчета внешних событий и ввода показаний в процессор, а также генерирования внешней синхронизации, которую может программировать процессор. Такое устройство называется программируемым интервальным таймером/счетчиком событий. Некоторыми областями применение такого устройства являются:

прерывание операционной системы с разделением времени через равномерные интервалы, чтобы она осуществляла переключение программ;

вывод точных временных сигналов с программируемыми периодами в устройство ввода-вывода (например, в аналого-цифровой преобразователь);

программируемая генерация скорости передачи в бодах;

измерение временной задержки между внешними событиями;

подсчет числа появлений событий во внешнем эксперименте и ввод показания в компьютер;

Рис. 9.25. Типичный интервальный таймер/счетчик событий

прерывание процессора после появления запрограммированного числа внешних событий.

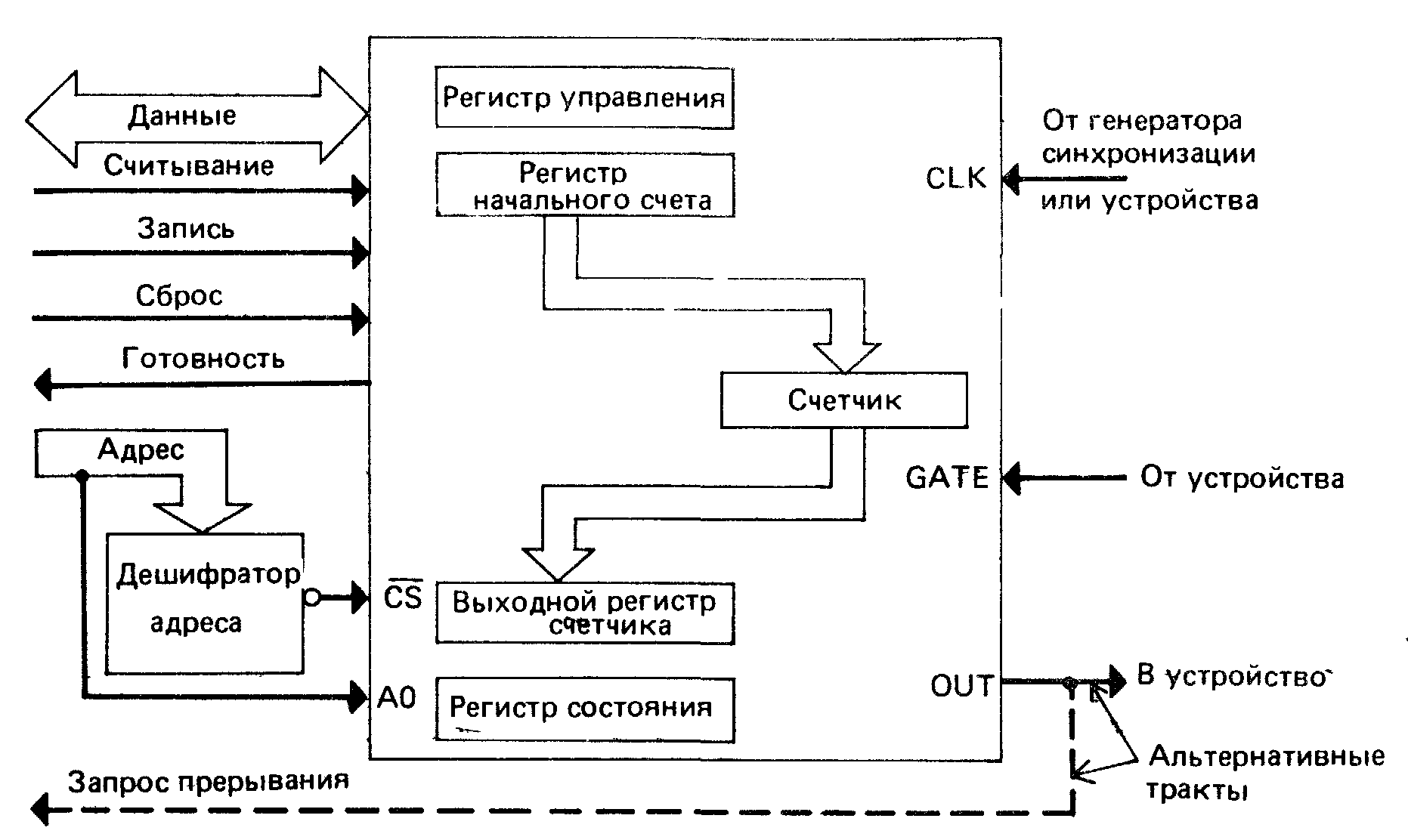

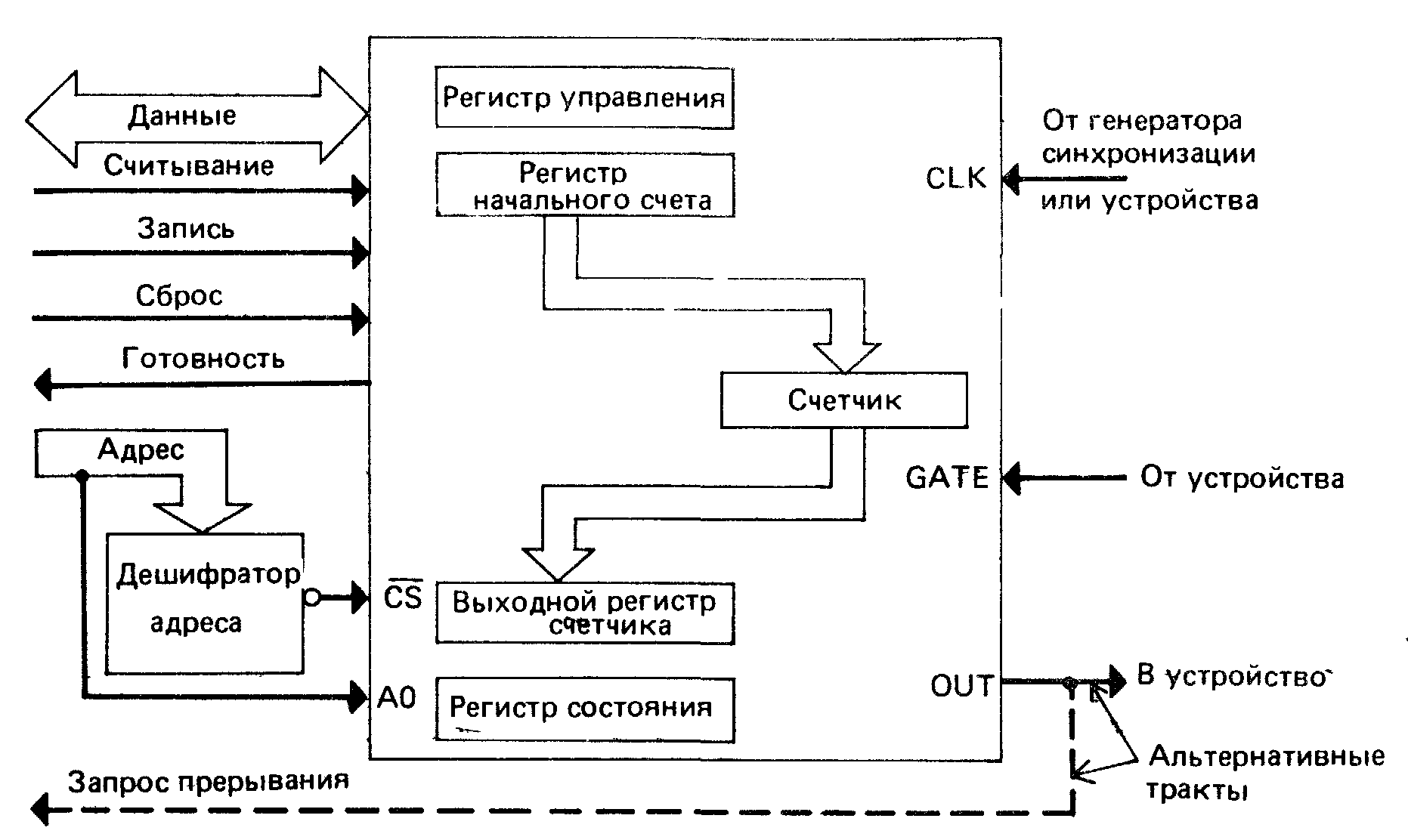

Типичная организация интервального таймера/счетчика событий показана на рис. 9.25. Слева находятся четыре доступных компьютеру регистра: два верхних являются выходними портами, а два нижних - входными. Сам счетчик прямо процессору не доступен, но может инициализироваться из регистра начального счета и считывается посредством передачи его содержимого в выходной регистр счетчика. Счетчик запускается с начального значения и отсчитывает до 0. Вход CLK определяет скорость счета, сигнал GATE разрешает и запрещает вход CLK и, возможно, выполняет другие функции, а выход OUT-становится активным при достижении счетчиком 0 или, возможно, при подаче сиг-нала АТЕ. Выход OUT подключается к линии запроса прерывания в системной шине, поэтому прерывание возникает при достижении счетчиком 0; его же можно подключить к устройству ввода-вывода для инициирования необходимых действий.

Устройство вводит значение в регистр начального счета, передает его в счетчик и выполняет счет "назад" (т. е. вычитание) импульсами со входа CLK. Текущее содержимое счетчика в любой момент можно ввести в процессор, не нарушая работы счетчика, посредством передачи его в выходной регистр счетчика с последующим считыванием из этого -регистра. При буферировании содержимого счетчика не требуется вводить его в процессор немедленно. Индикация нуля в счетчике обычно фиксируется на выходе OUT и в одном бите' регистра состояния. Поэтому для обнаружения нуля допускается применять Программный ввод-вывод и ввод-вывод по прерываниям.

Регистр управления определяет режим работы и выполняет другие функции. Режим точно определяет, что происходит при достижении счетчиком 0 и (или) при подаче сигнала на вход GATE. Возможными действиями являются:

вход GATE применяется для разрешения и запрещения входа CLK;

вход GATE вызывает реинициализацию счетчика;

[i. вход GATE прекращает счет и формирует высокий уровень на выходе OUT;

- при достижении 0 счетчик выдает сигнал OUT и останавливается;

при достижении 0 счетчик выдает сигнал OUT и автоматически реинициализируется из регистра начального счета.

Режимы могут также определяться комбинациями перечисленных возможностей Рассмотрим, например, применение интервального таймера в операционной системе разделением времени. В этом случае на вход CLK подаются сигналы синхронизации, ) выход OUT подключается к линии запроса прерывания, возможно, немаскируемой прерывания. Вход GATE здесь не требуется. При включении системы в регистр начальщ го счета загружается значение

начальный счет == частота синхронизации Х Т,

где Т - продолжительность каждого временного кванта в секундах. Задается такой режим, что при достижении счетчиком 0 содержимое регистра начального счета вновь загружается в счетчик, а выход OUT становится активным. Поскольку сигнал OUT используется как запрос прерывания, процедура прерывания для переключения программ будет выполняться с интервалом Т секунд.

9.3.1 Программируемый интервальный таймер

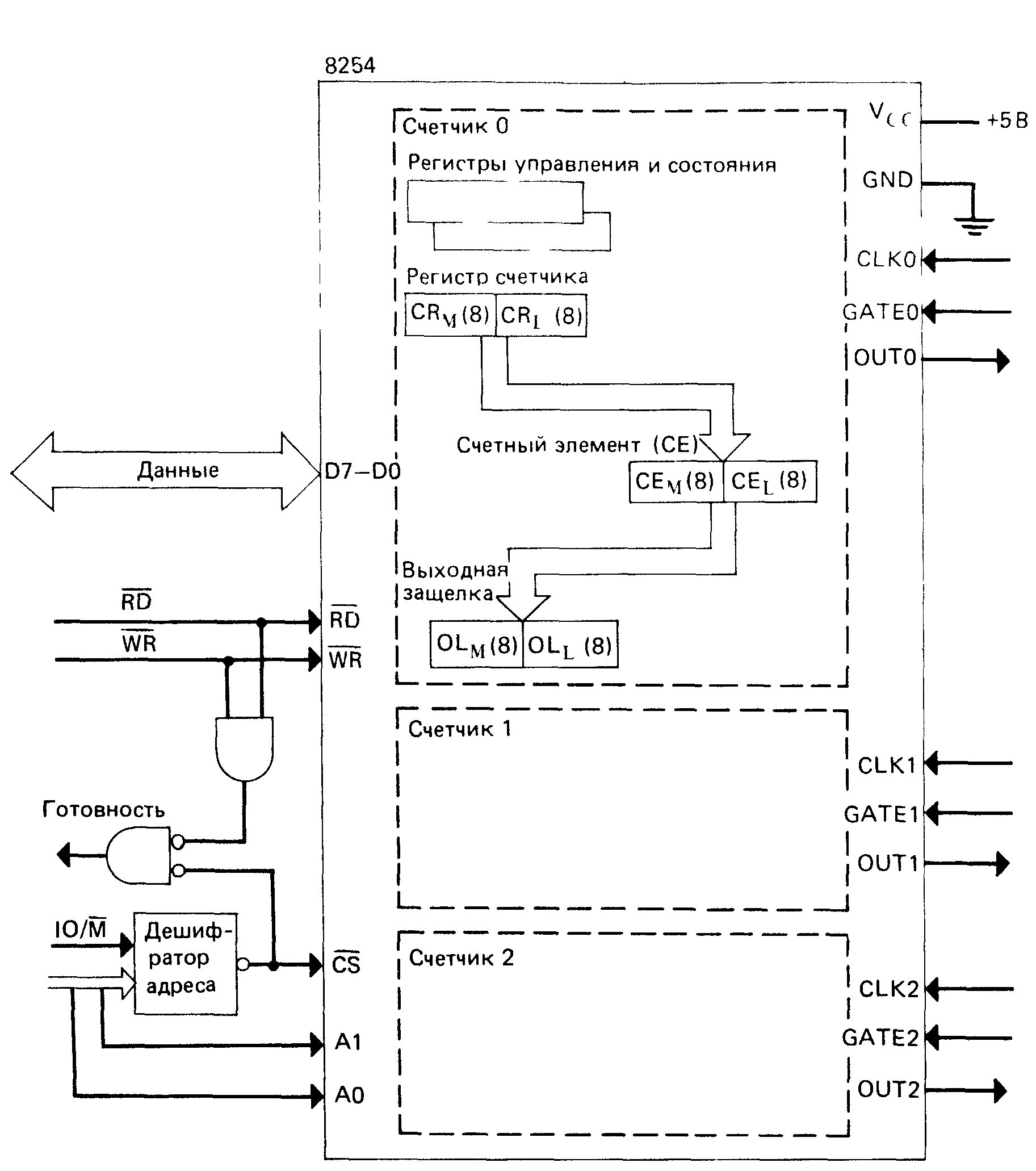

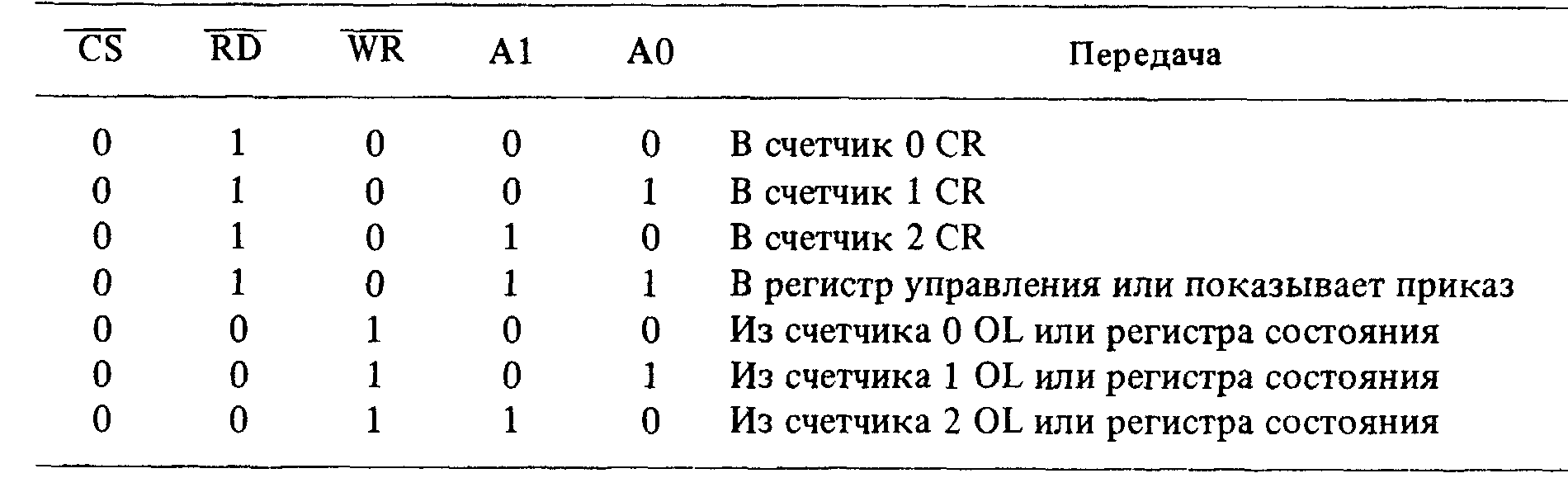

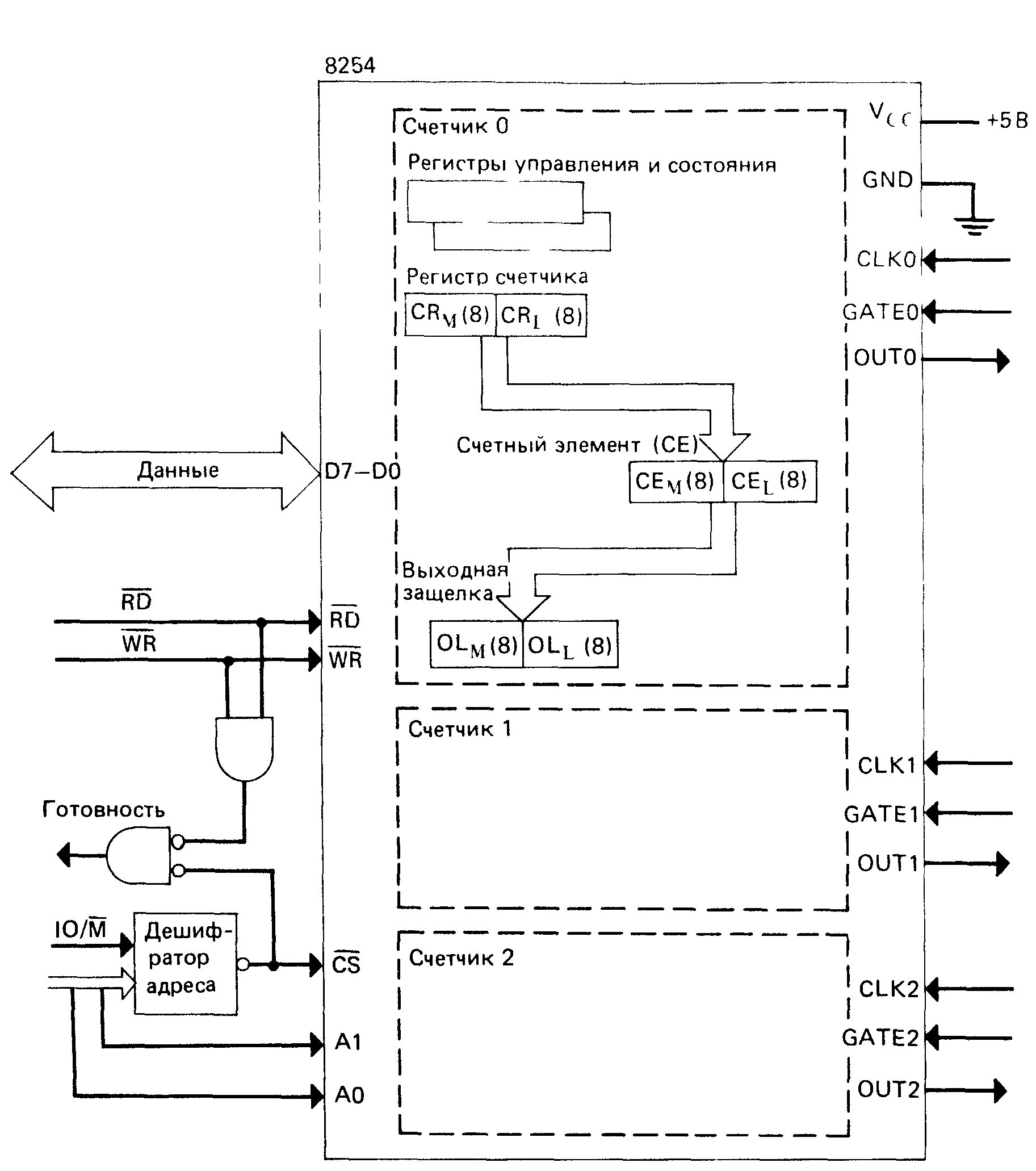

На рис. 9.26 представлена схема интервального таймера/счетчика событий 8254 фирмы Intel. В нем имеются три одинаковые счетные схемы со своими входами CLK и GATE и выходом OUT. Каждая схема имеет регистр управления и состояния, регистр счетчика (CR) для приема начального счета, счетного элемента (СЕ) , который выполняет счет, но непосредственно процессору недоступен, и выходного регистра-защелки (OL) для фиксации содержимого СЕ, так что его может считать процессор. Полагается, что CR, СЕ и OL представляют собой пары 8-битных регистров. (Реальные схемы несколько отличаются от приведенных, но для программиста рисунок абсолютно точен.)

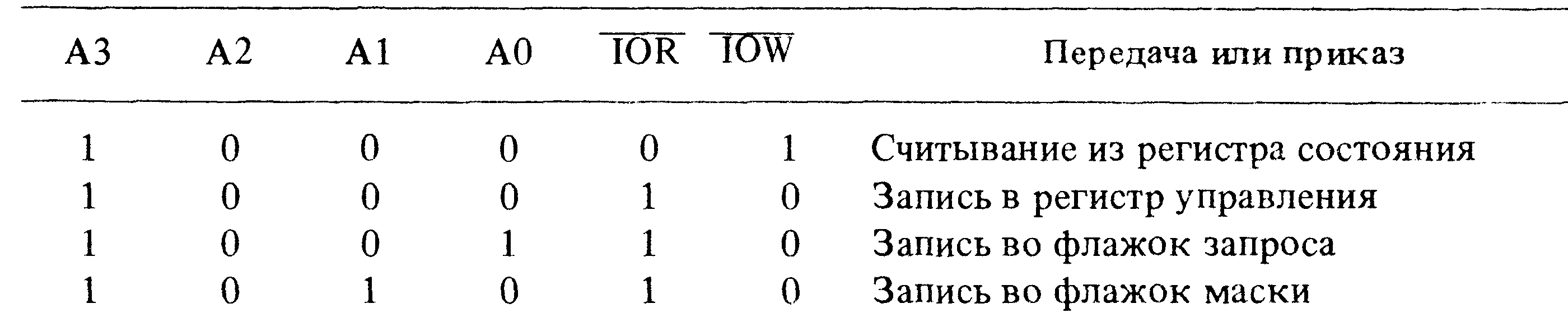

Обращения к регистрам производятся в соответствии с табл. 9.3.

Таблица 9.3

Обращения к регистрам таймера/счетчика 8254

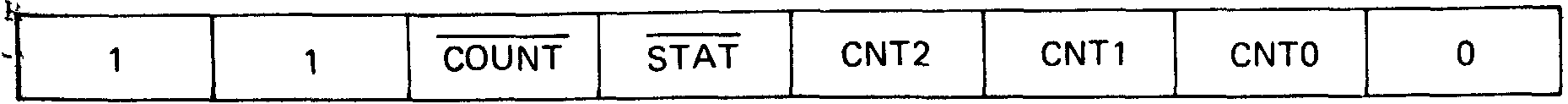

Все остальные комбинации приводят к тому, что линии данных переводятся в высокоимпедансное состояние. Когда А1 = АО = 1, выполнение записи в регистр управления или выдачи приказа зависит от старшего бита выводимого байта. В последних трех комбинациях считывание OL или регистра состояния определяет предыдущий приказ.

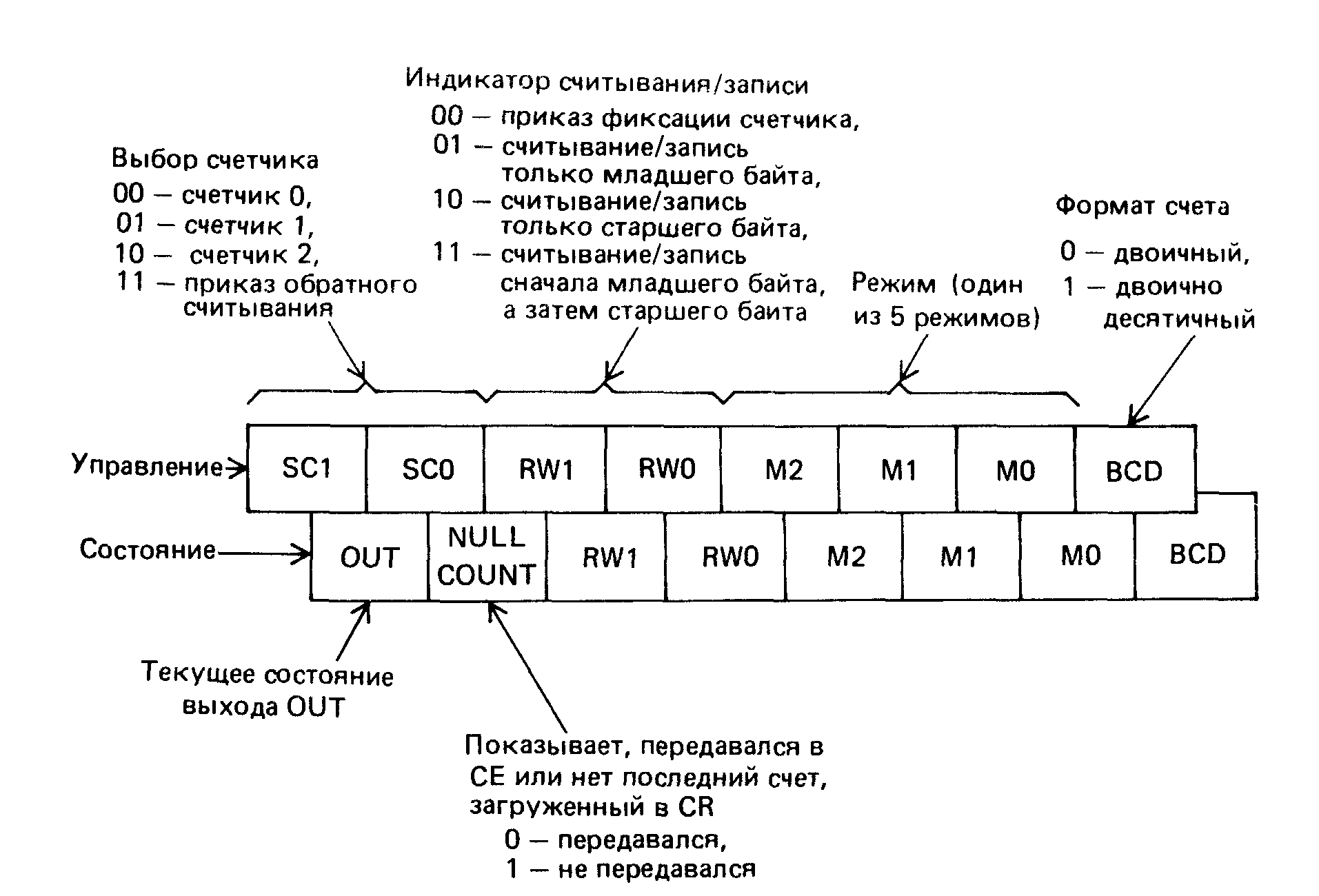

Имеются два вида приказов. Приказ фиксации счетчика заставляет соответствующий OL зафиксировать содержимое СЕ счетчика, определяемого двумя старшими битами приказа. Приказ обратного считывания фиксирует комбинацию СЕ или "готовит" комбинацию регистров состояния для считывания. Подготовка регистра состояния означает

Рис. 9.26. Схема таймера/счетчика 8254

его считывание, когда в следующей операции считывания осуществляется ввод из счет-' чика. Состояния 00, 01 и 10 двух старших бит показывают приказ фиксации счетчика, а состояние 11 - приказ обратного считывания. В приказе фиксации биты 5 и 4 должны быть нулевыми, а остальные биты не используются. Приказ обратного считывания имеет следующий формат:

IL Если бит COUNT = 0, фиксируются СЕ всех счетчиков, биты CNT которых содержат 1. |всли, например, CNTO = CNT2 = 1 и CNT1 = 0, то СЕ в счетчиках 0 и 2 фиксируются, "»в счетчике 1 не фиксируется. Аналогично STAT = 0 вызывает подготовку регистров

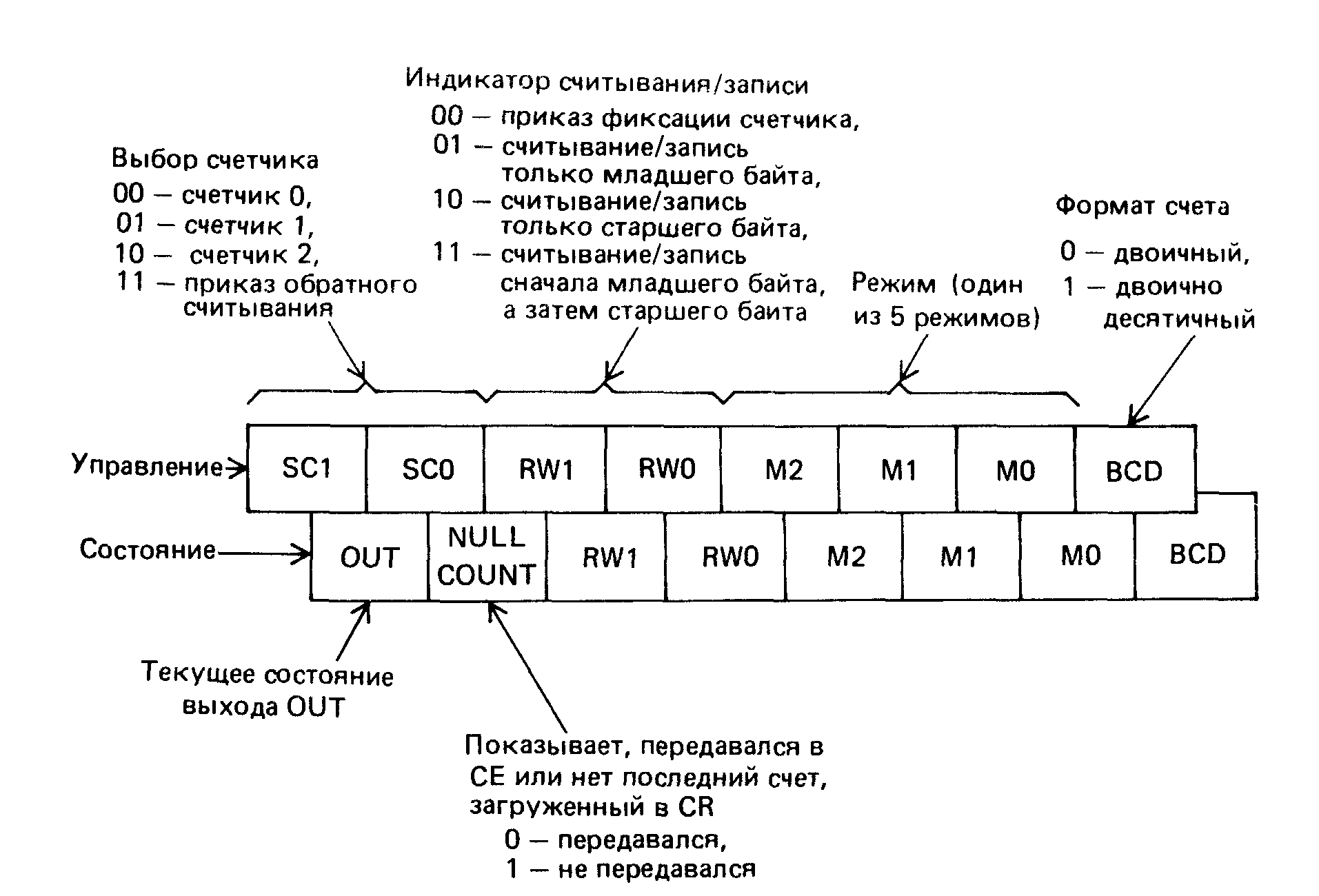

Рис 9 27 Регистры управления и состояния счетчиков

состояний счетчиков для ввода. Действия по фиксации и подготовке допускается указывать в одном приказе.

Форматы регистров управления и состояния показаны на рис. 9.27. Если два старших бита равны 1, они задают приказ обратного считывания; в противном случае они определяют счетчик. Если указан счетчик и биты 5-4 содержат нули, то имеет место приказ фиксации, который направляется в регистр управления выбираемого старшими битами счетчика. Когда же комбинация в битах 5-4 отличается от 00, она указывает тип ввода из OL или вывода в CR. Комбинация 01 идентифицирует операции считывания/записи из (в) OL^/CR, комбинация 10 - из (в) OLix/CRv» и комбинация 11 - выполнение операций парами (первый байт из (в) OLi /CRi и второй из (в) OLn/CR^i) Запись одного байта в CR вызывает сброс другого байта Биты 1, 2 и 3 определяют режим, а бит 0 определяет формат счета.

Таймер/счетчик имеет следующие режимы работы (через N обозначен начальный счет)

Режим 0 (прерывания по концу счета) . Сигнал GATE = 1 разрешает счет, a GATE = О запрещает счет, причем GATE не влияет на выход OUT. Содержимое CR передается в СЕ по первому импульсу CLK после того, как процессор осуществил запись в CR, независимо от сигнала на входе GATE Импульс, который загружает СЕ, не учитывается при счете На выходе OUT формируется низкий уровень при записи в регистр управления, который сохраняется до достижения счетчиком 0. Режим 0 предназначен в основном для счета событий.

Режим 1 (аппаратно перезапускаемый одновибратор). После загрузки значения N в CR переход 0 -* 1 на входе GATE вызывает загрузку СЕ, переход 1 -»0 на выходе OUT и запускает счет. Когда счетчик достигает 0, на выходе OUT формируется высокий уровень; таким образом, результатом является отрицательный импульс на выходе OUT с продолжительностью N периодов синхронизации

Ре&им 2 <гчрч' v-и^й nil ерьиышй гаймер) Посл„ шрузки значения N в CR следующий импульс синхроь^ации осуществляет передачу из CR в СЕ На выходе OUT возникаем переход 1 -^ 0. когда счетчик достигает 0 низкий уровень сохраняется в течение одною импульса CJ-K Згпсм на выходе OUT. появляется высокий уровень, производится повюрная загрузка СГ из CR, в результате на выходе 01Л появляется отрицательный импульс через N гакгов синхронизации Сигоал GAU --- 1 разрешает счет, а GATi U запрещаег Переход 0 " 1 на входе GAJ 1 вызыв^ г реинициализацию счета следующим импульсом < инхрони-)авд'и Данный pt-л.л vi применяется для реализации периодического интервального ыймера

Режим 3 (генератор прямоугольного сигнала). Аналогичен режиму 2, но на выходе От формируется низкий уровень при достижении половины начального счета; этот уровень сохраняется до достижения счетчиком 0. Как и прежде, сигнал GATE разрешает и запрещает счет, а его переход 0 -* 1 рсинициализирует счет Этот режим применяется в генераторах, определяющих скорость передачи в бодах.

Режим 4 (программно-запускаемый строб) . Аналогичен режиму 0, но на выходе OUT в процессе счета действую высокий уровень, а при достижении счетчиком 0 появляется отрицательный импульс с продолжительностью в один такт синхронизации

Режим 5 (аппаратно-запускаемый строб с перезапуском) После загрузки CR переход 0 ^ 1 на входе GATF вызывает передачу из CR в СЕ следующим импульсом CLK. В процессе счета на выходе OUT действует высокий уровень, а при достижении счетчиком 0 формируется отрицательный импульс с продолжительностью в один период CLK Сигнал GATE может в любой момент времени реинициализировать счет.

Начальное значение счета 0 во всех режимах интерпретируется как 216 или Ю4 в зависимости от формата счета. Мы привели общие принципы работы микросхемы 8254, а подробное описание содержится в фирменных материалах.

MOV DX.OFFE9H MOV AL.,0 OUT DX,AL

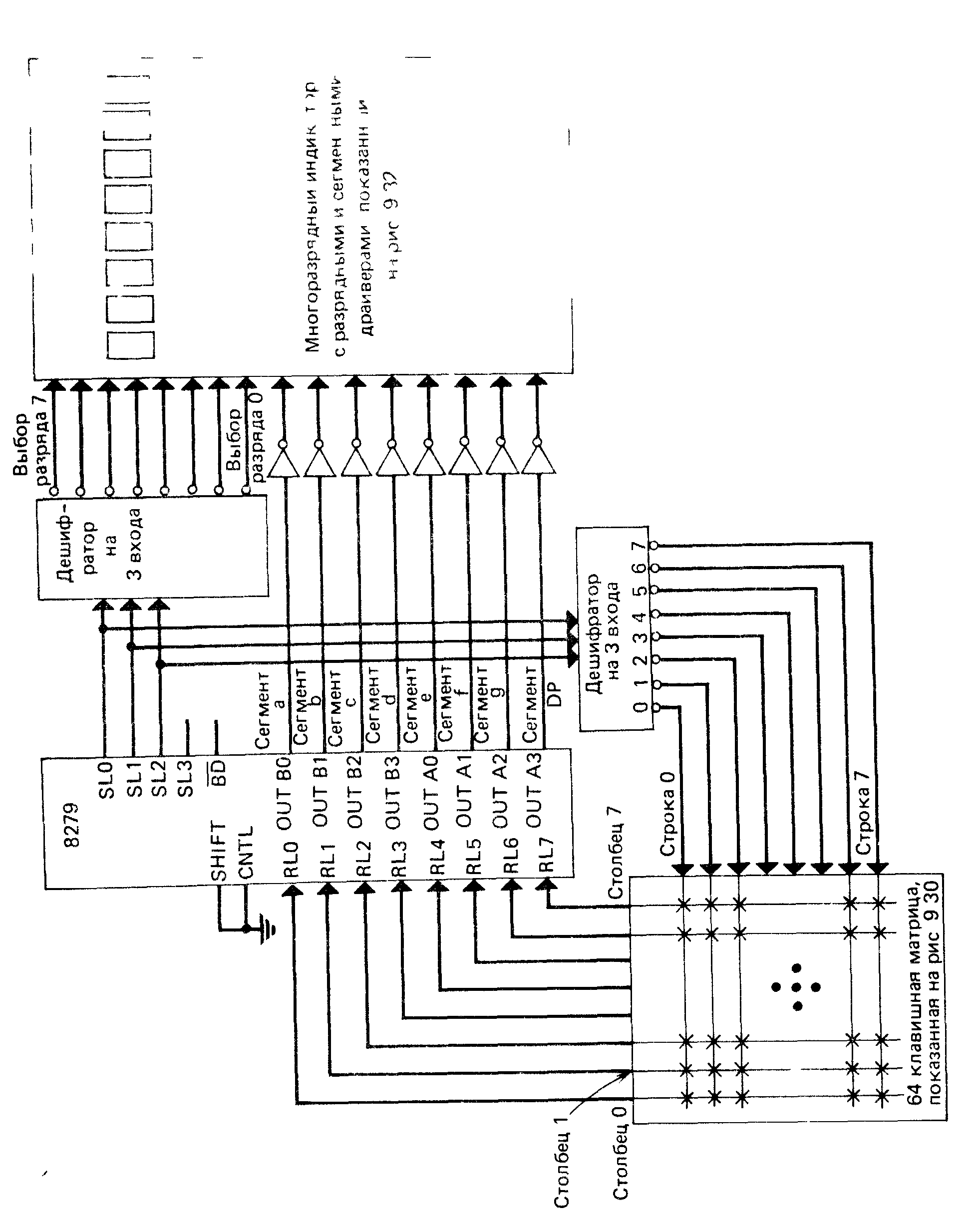

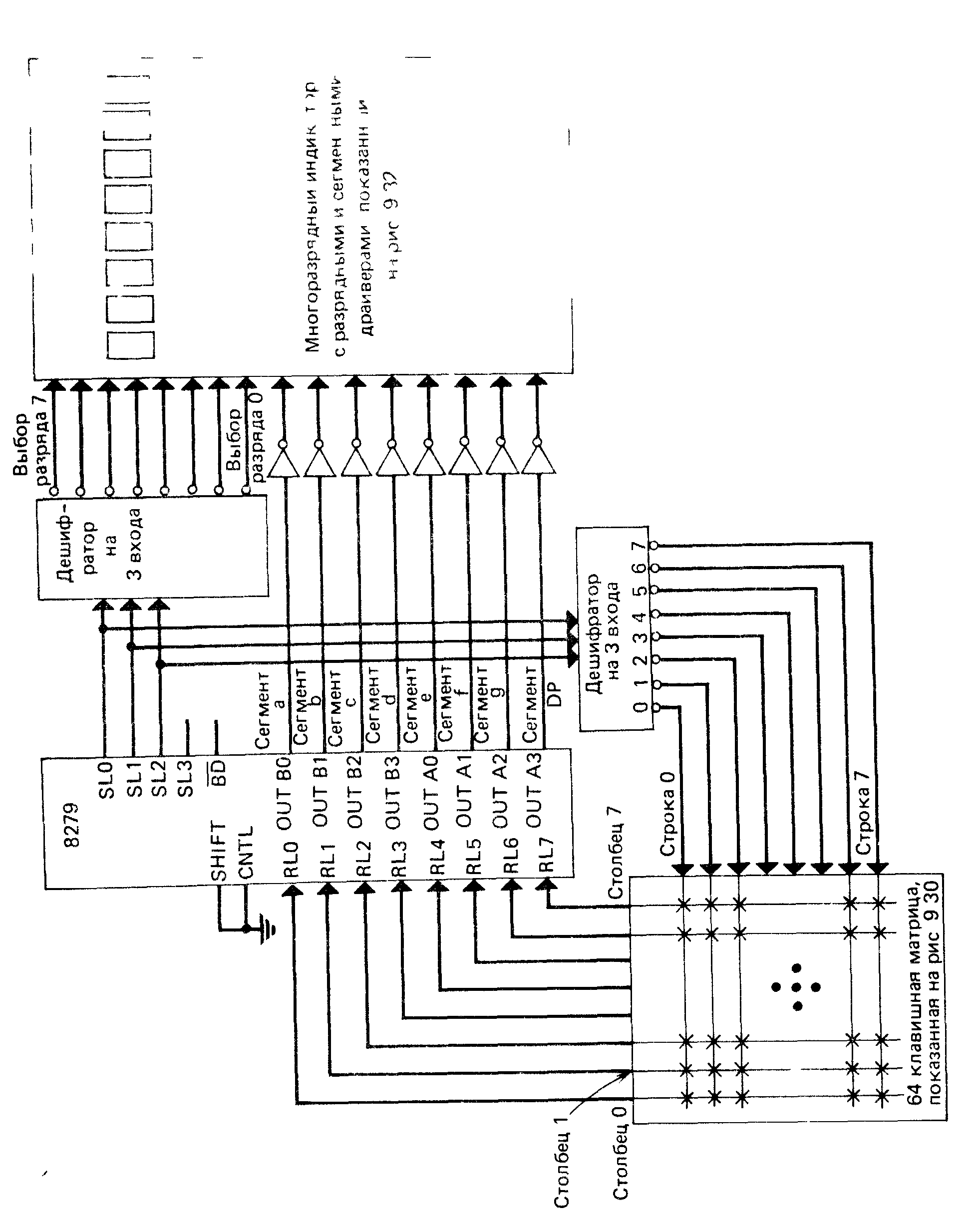

Рис 9 35 Применение контроллера 8279 в интерфейсе клавиатуры и многоразрядного индикатора

Таким образом, символы, сформированные нажатыми клавишами, можно считать через память I IFO Далее приведен программный фрагмент, в котором применяется программный ввод вывод для ввода восьми кодовых слов и запоминания их в 8 байтном массиве KFYS (первый байт находи гся по старшему адресу)

МПу SI 8

MOV DX.OFFE9H

M0\/ A L,01000000 В

OUT OX.AL ^БХ7 MOV ПХОГГГ9Н !f l г •N М. ПХ

tls AL,Ot h

JZ IDLE

MOV DX,OFFE8H

IN AL,DX

MOV KEYS[SI-1],AL

DEC SI

JNZ NEXT

Первая команда инициализирует счетчик в SI, следующие )ри задаю г ввод iio кт. но-му адресу как ввод из HI О Очередные три команды, начиная с mcskh IDL1 , загтавля ют процессор ожидать до готовности ввода, а находящиеся за ними еще три команды передают введенные данные в KbYS Последние две команды вызывают повторение последовательности до тех пор, пока не будут введены восемь символов

Для индикации символов процессор должен сначала выдать приказ записи в '1амя!ь индикатора, а затем выводить в нее данные Следующий фрагмеш индицирует восемь цифр, которые хранятся, начиная с DIGITS (младшая цифра хранится по меньшему ал. pecv)

MOV S1.8

MOV DX,OFFE9H MOV AL,10010000В OUT DX,AL MOV DX.OFFFSH AGAIN MOV AL,DIGi"[b(Si 1 j OUT DX,AL DEC SI JNZ AGAIN

Первая команда образует в SI счетчик цифр, следующие 1ри выводят прикчз записи в память индикатора, а находящаяся за ними команда члгрул'-^ к в DX а фее буферной^ регистра данных Последние команды образуют цикл вывода п'(фр в ш мять индг каюра

9.5. КОНТРОЛЛРРЫ ПРЯМОГО ДОСТУПА К ПАМЯТИ

В гл 6 было показано, что контроллер ПДП может стагь ведущим шины и управлягь передачей данных между ингерфейсом ввода-вывода и памятью или интерфейсом внешней памяти и памягью В процессе передачи он должен помещать адрес t н-г тину, а также выдавать и принимать сигналы квитирования iai\, л.'к эго целае! логика управления ши ной Назначение коптролл1ра ПДП осущестпячь последовательное п.. передач (i e передачу блока) по<редством пропусков ("кражи") циклов шины

Обычно контроллер ПДП рассчитан на обслуживание одною или нескольких интерфейсов ввода-вывода или внешней памяти и каждый интерфейс подключается к контроллеру набором проводников Часть контроллера ПДП, предназначенная для обслужи вания одного интерфейса, называется каналом

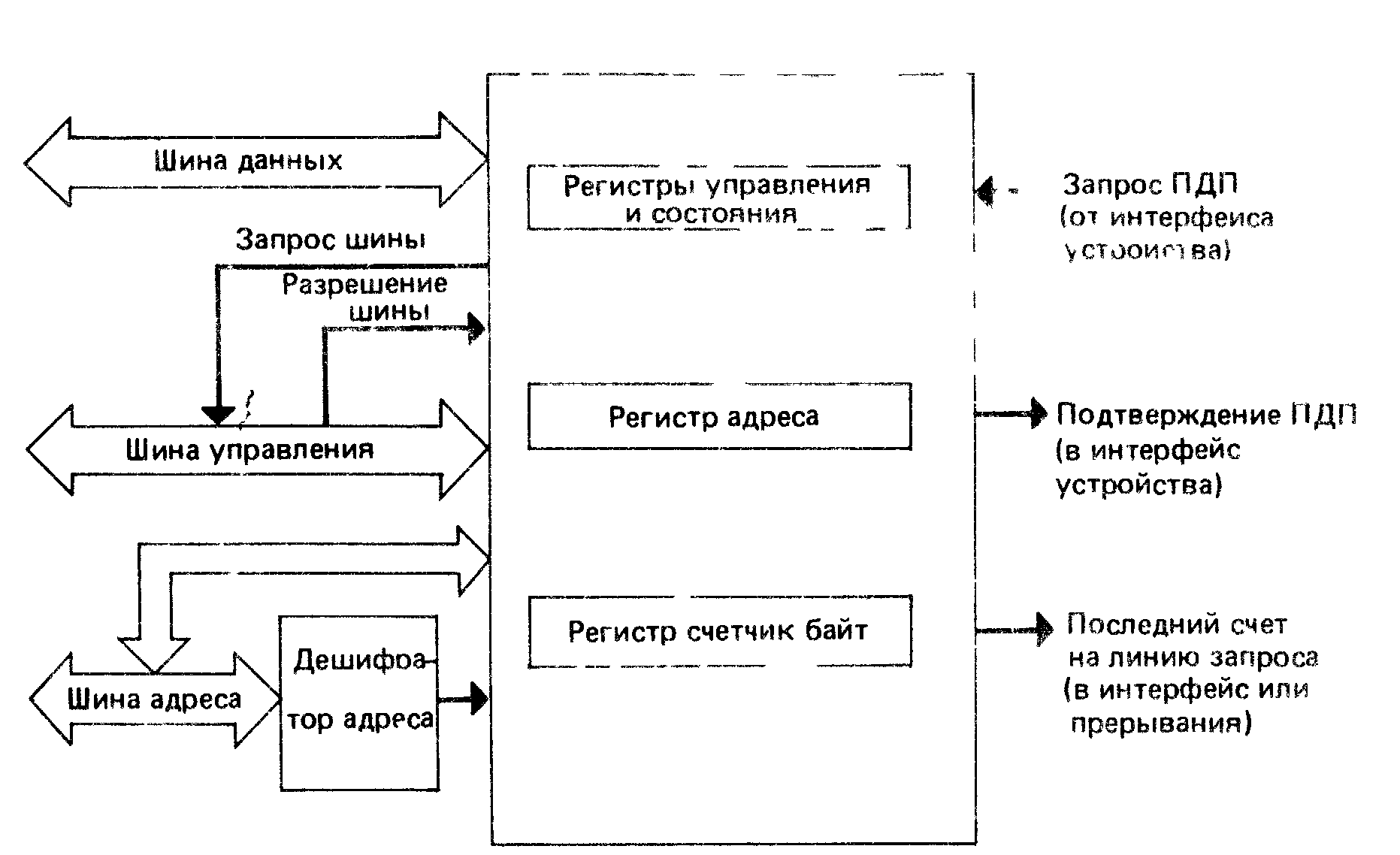

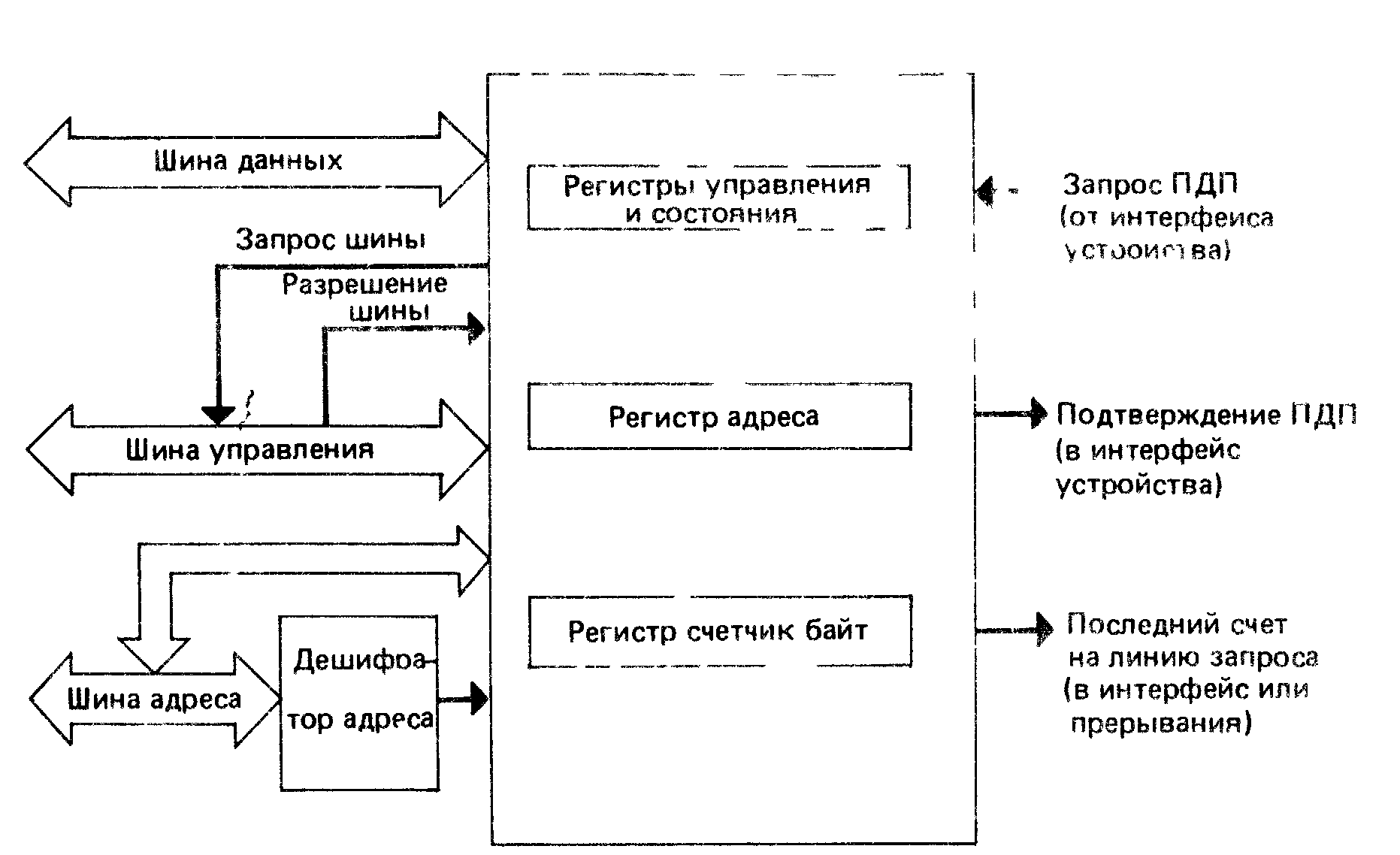

Общая организация одноканального контроллера ПДП и его основные связи показа ны на рис 9 36 Кроме обычных регистров управления и состояния, в каждом канале должны быгь регистр адреса и счетчик байт (или слов) Иницьачтпаиия контроллера со-

? Рис 9.36. Общая организация контроллера ПДП

стоит в загрузке в эти регистры начального (конечного) адреса массива в гамяти, который служит буфером, и числа передаваемых байт (слов) При вводе в памягь при наличии данных интерфейс делает запрос ПДП Затем контроллер формируег запрос шины и при получении разрешения шины выводит содержимое регистра адреса на шину адреса, посылает подтверждение в интерфейс и выдает сигналы считывания ввода-вывода и записи в память После этого интерфейс помещает данные на шину данных и снимае! свой запрос Когда память воспринимает данные, она возвращает в контроллер сигнал готовности; контроллер осуществляет инкремент (декременг) регистра адреса, декремент счетчика байт (слов) и снимает запрос шины При достижении счегчиком нуля процесс прекращается и выдается сигнал в процессор как запрос прерывания или в ишер-феис для извещения о том, что передачи завершены Вывод реализуется аналогично, но контроллер выдает сигналы записи ввода-вывода и считывания из памяти, а данные пе редаются в другом направлении.

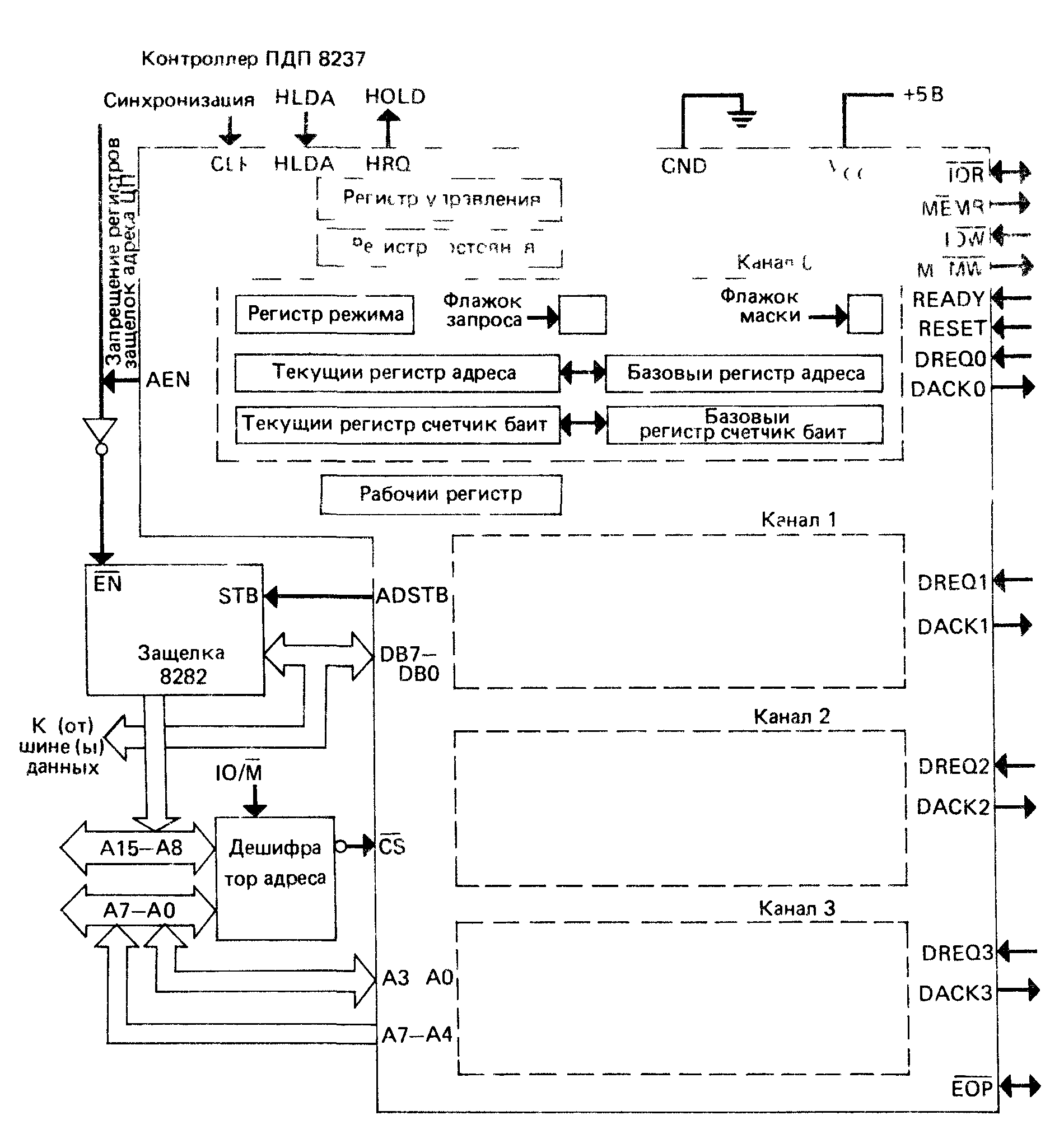

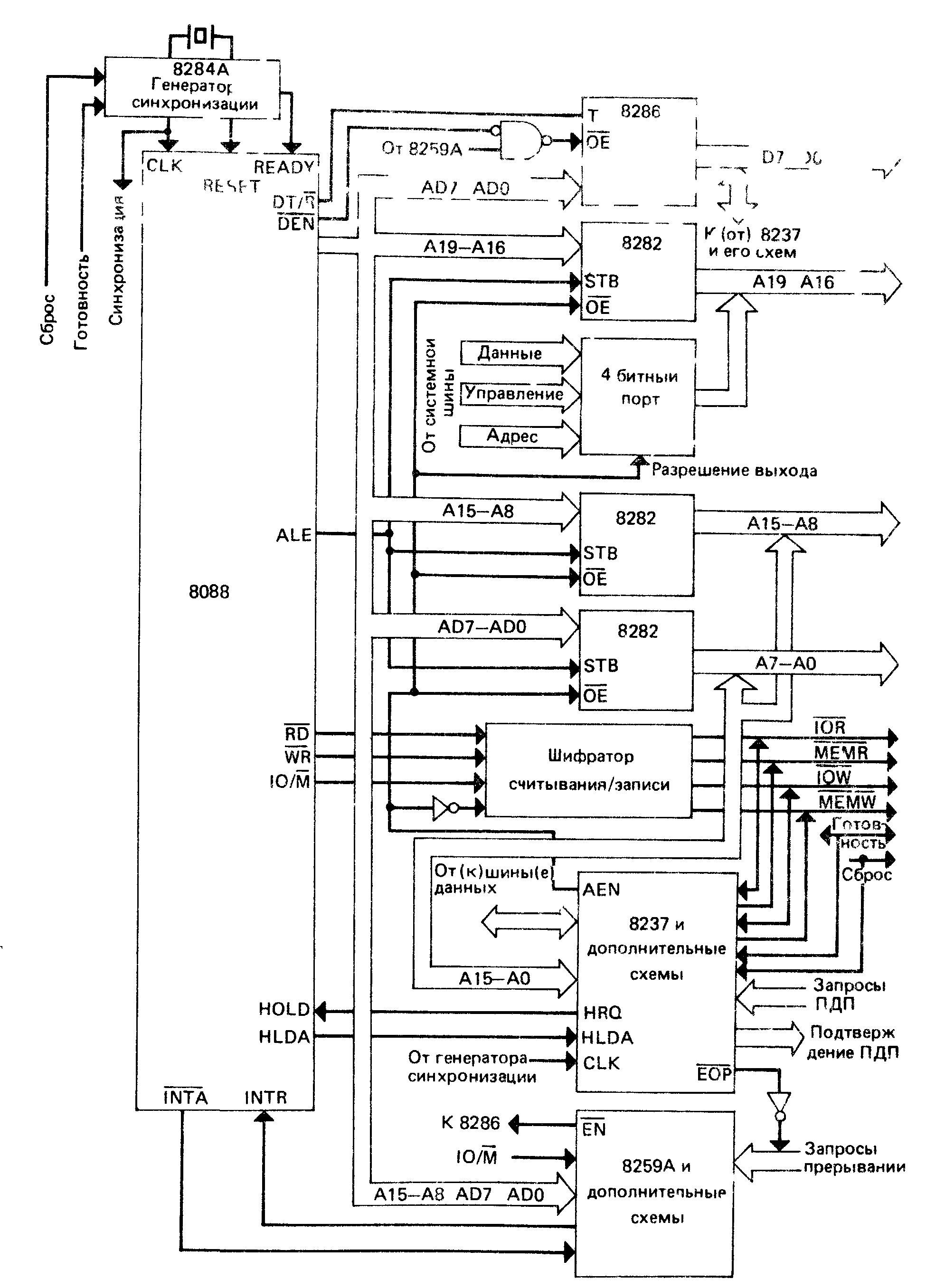

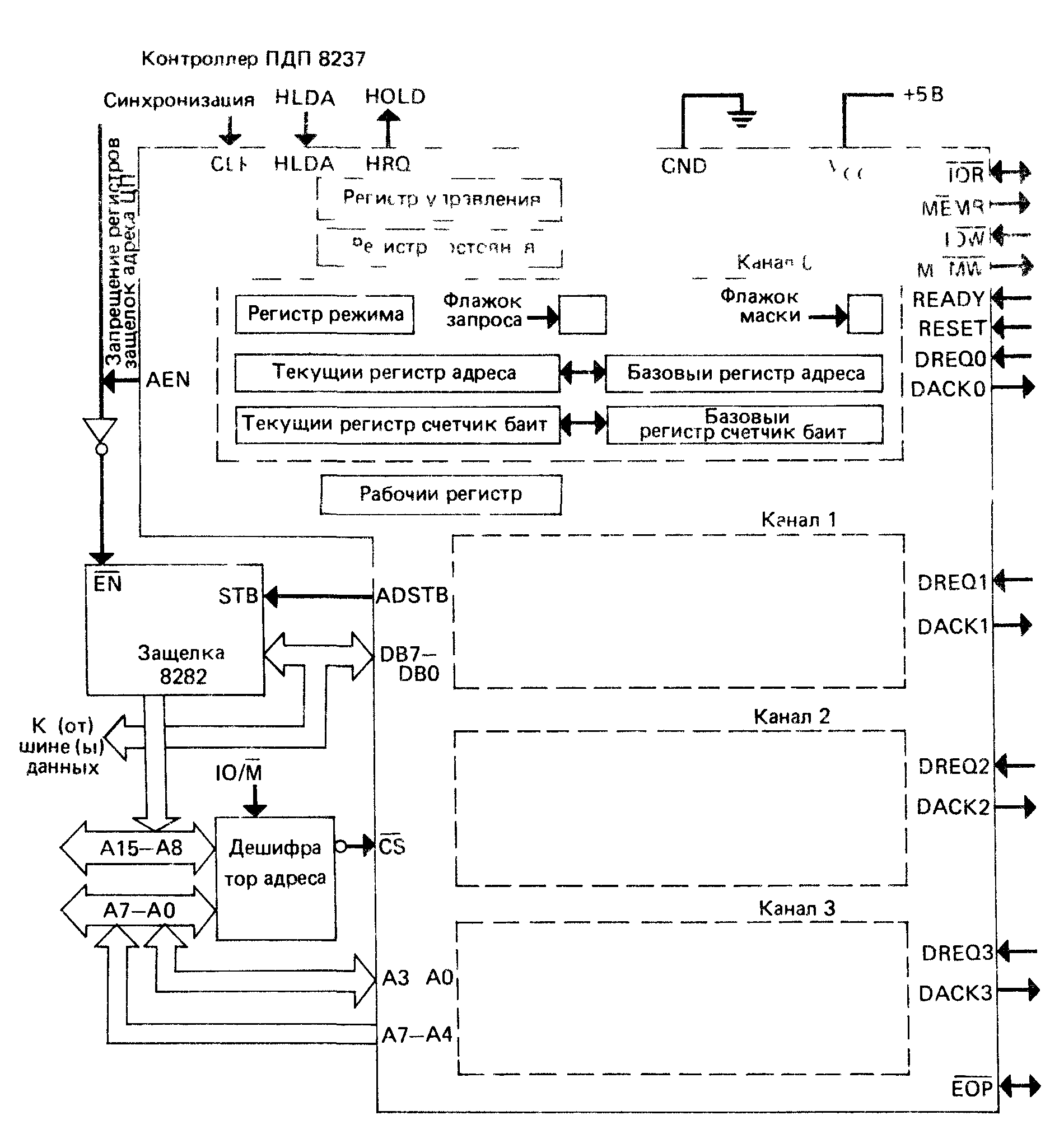

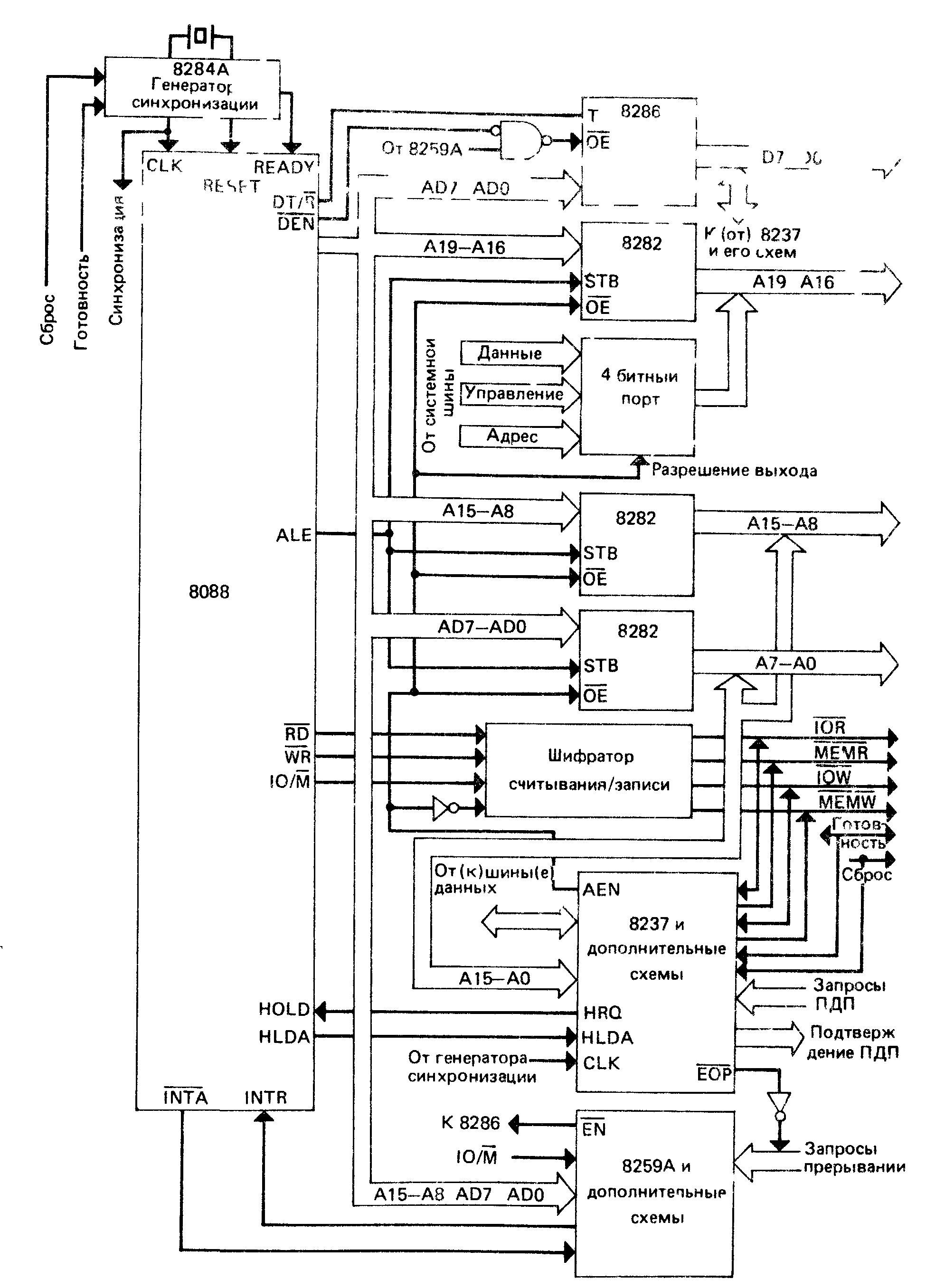

В качестве примера рассмотрим контроллер ПДП 8237 фирмы Intel. Его общая организация вместе с дополнительной логикой, необходимой в системе на базе микропроцессора 8088, приведена на рис 9 37, а конфигурация в минимальном режиме с контроллером ПДП - на рис 938

Когда данные помещаются в регистры контроллера или считываются из них, контроллер ведет себя как любой другой интерфейс ввода-вывода. В качестве ведомого он воспринимает 16-битные адреса, причем 12 их старших бит определяют выбор микросхе мы, а 4 младших применяются для внутренней адресации. Когда сигналы HRO =^ CS — = 0, контроллер превращается в ведомого и линии TOR и IOW являются входными Процессор может обратиться к внутренним регистрам, формируя активный сигнал IOR ИлиТО\У Сигнал AEN, которым ведущий контроллер идентифицирует выдачу адреса, на-Находится в состоянии 0 до тех пор, пока система взаимодействует с внутренними регистрами

Рис 9 37 Организация контроллера ПДП 8237

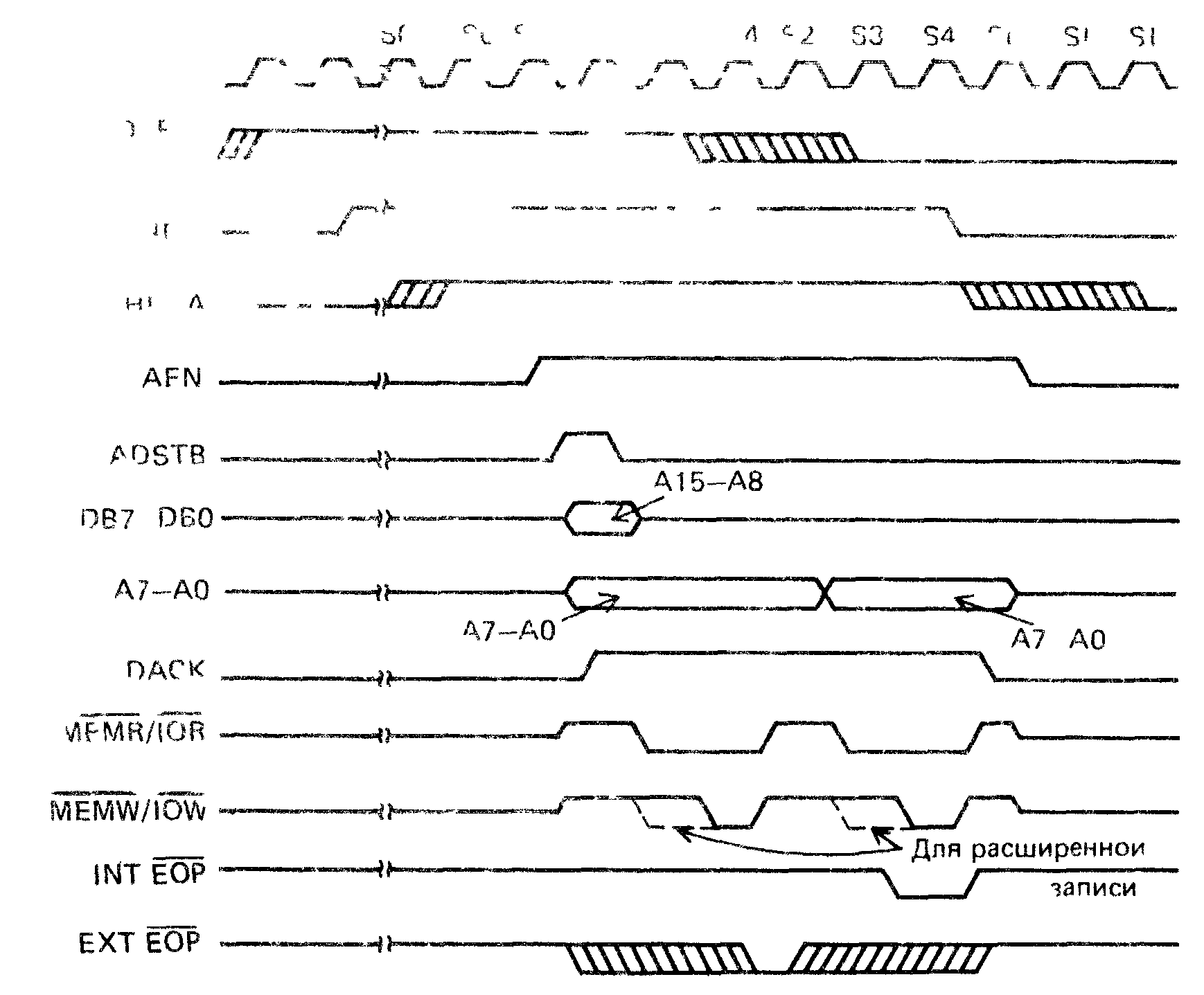

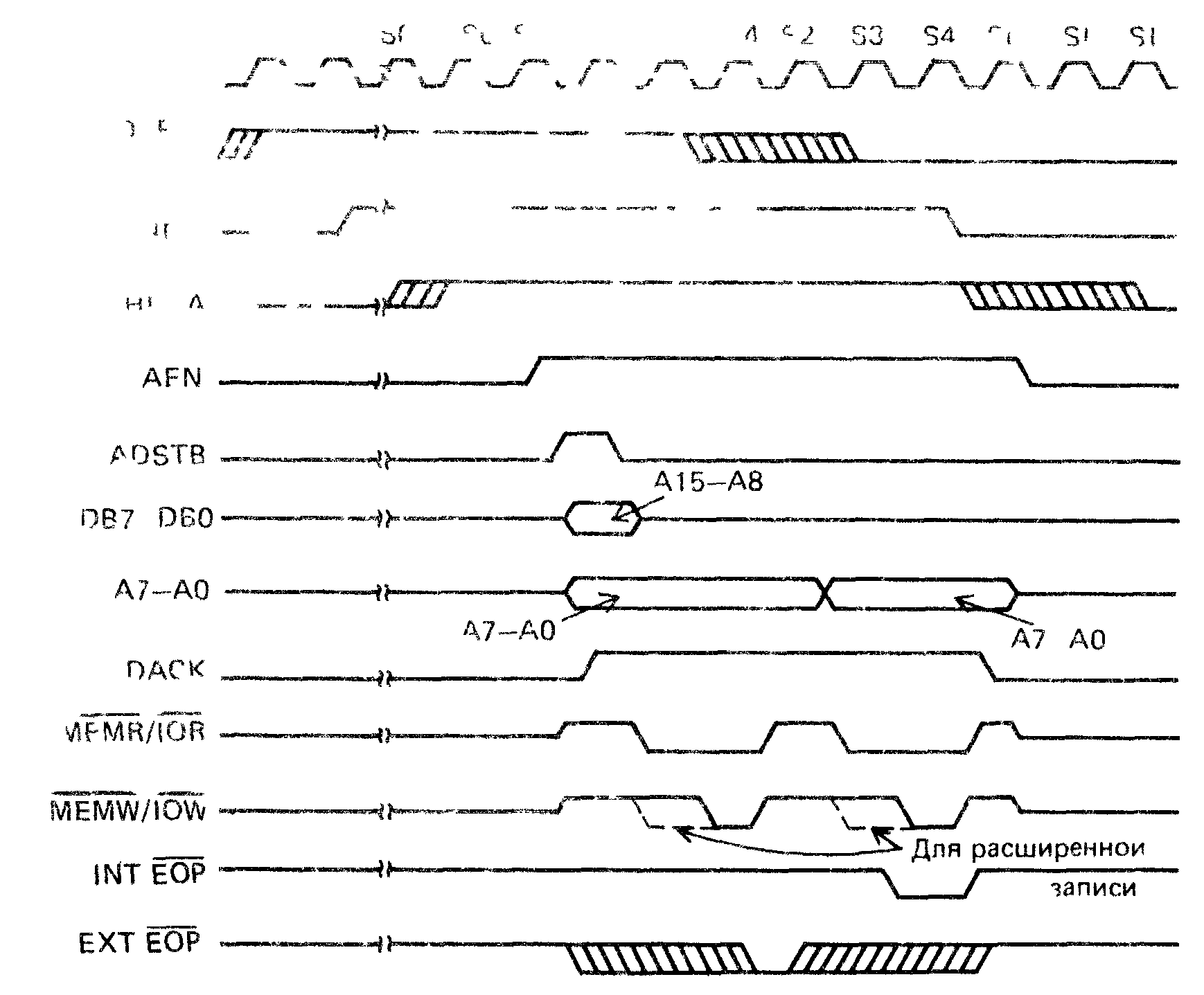

В качестве ведущего контроллер должен выдавать адреса шины Младший байт адре са выводится на линии А7 АО, а старший - на линии DB7 DBO с одновременной установ кой AEN = 1 При таком уровне сигнала AEN разрешается внешний регистр защелка адреса обеспечивая вывод старшего байта адреса на линии А15 А8 Сигнал AFN приме няется также для запрещения регистров защелок адреса 8282, подключенных к линиям А19 А8 и AD7 ADO процессора Через небольшой временной интервал после выдачи сиг нала AEN на выходе строба адреса (ADSTB) формируется импульс Он применяется для загрузки бит 8-15 адреса в регистры защелки 8282, подключенные к линиям А15 А8 Старшие 4 бита адреса А19 А16 контроллер 8237 не выдает,и их необходимо програм мировать отдельно до начала блоковой передачи Для хранения этих бит адреса потребу ется 4-битный порт ввода вывода, в который можно вывести данные, как в любой дру гой порт Во время блоковой передачи содержимое этого порта изменять нельзя, следо вательно, за одну передачу можно передать максимум 216 байт

Рис 938 Система на базе микропроцессора 8088 в минимальном режиме с контролле ром 8237

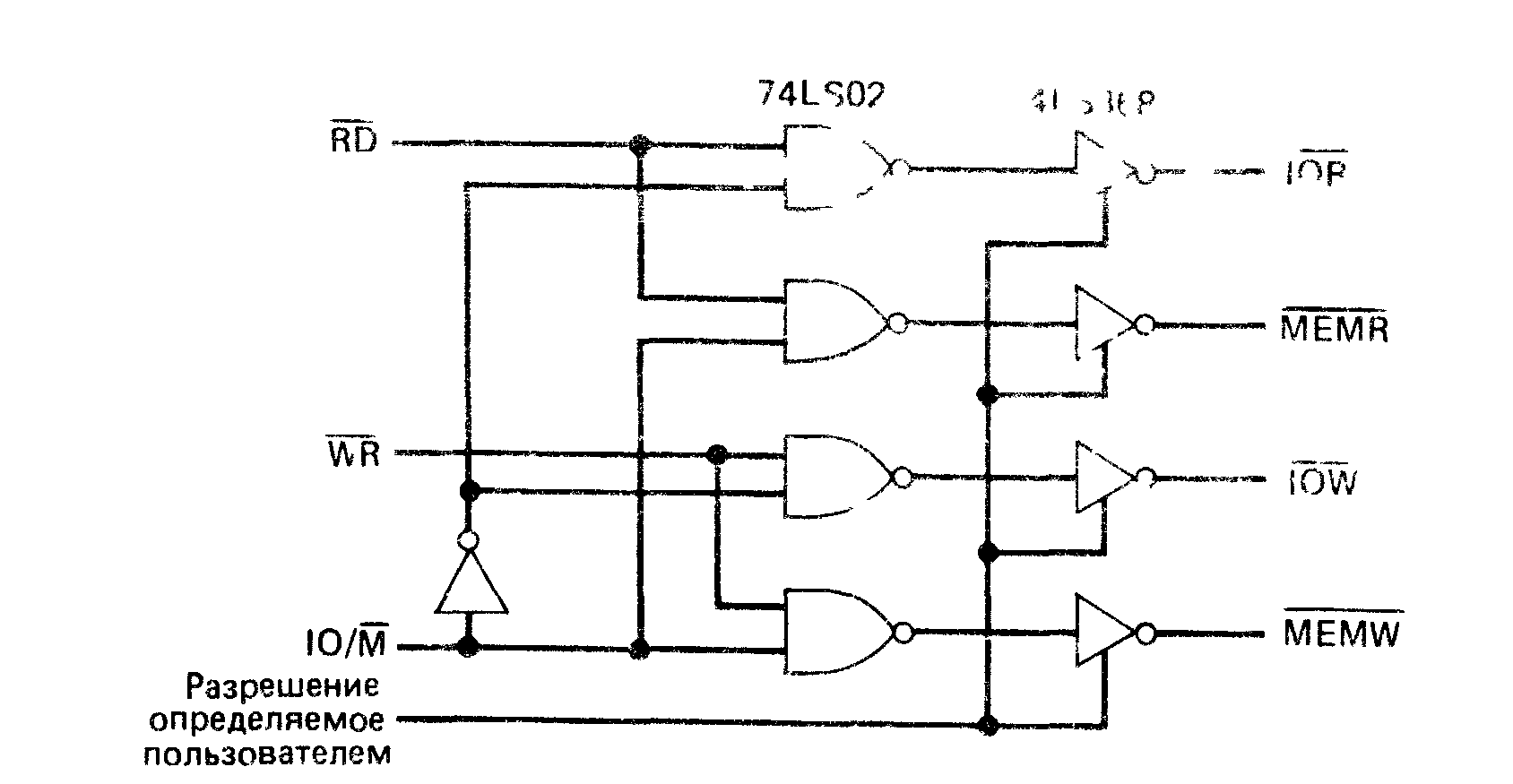

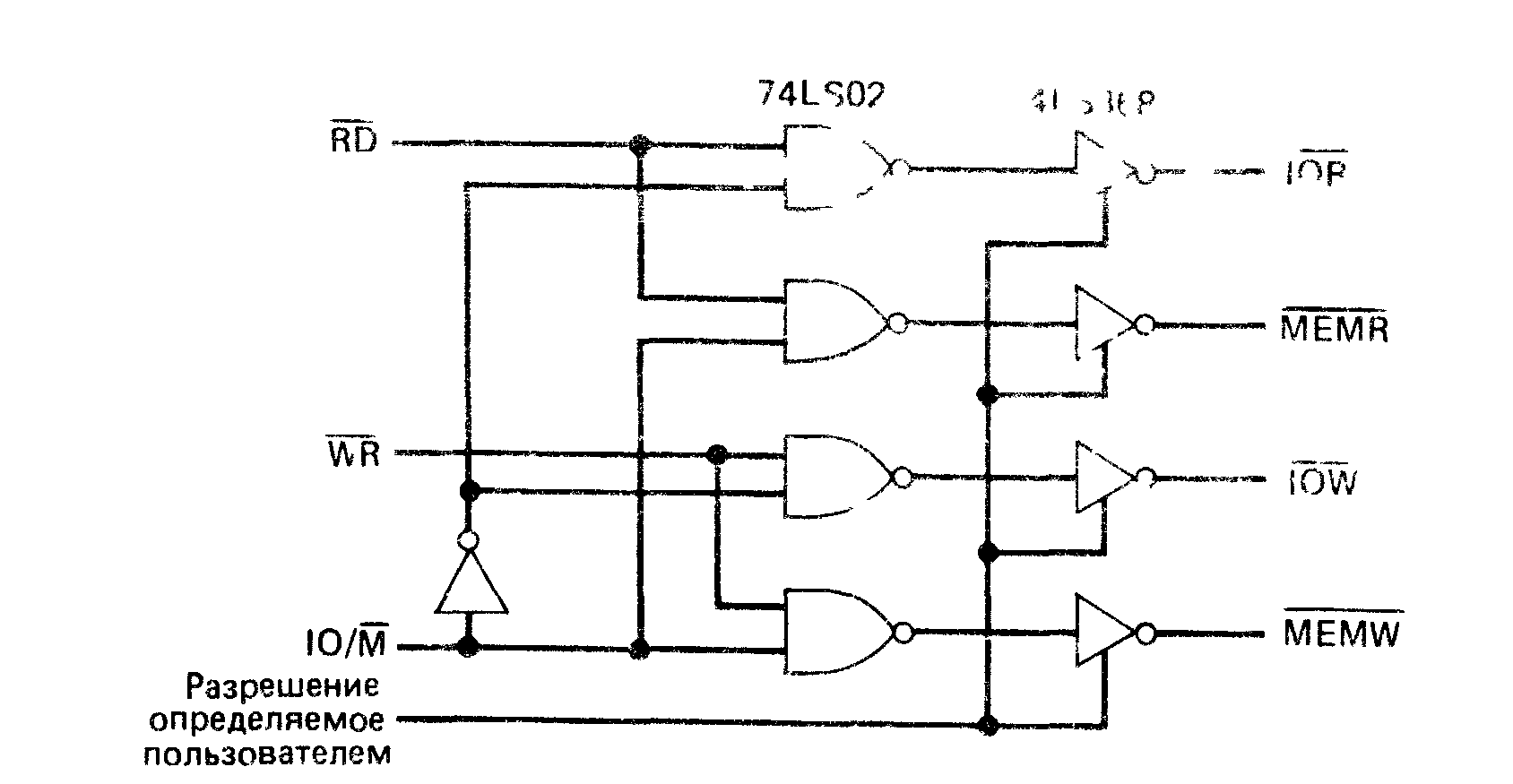

Рис 939 Схема кодирования сигналов RD ^ЫиЮ/М

Примечание Если te требуются трж табильные линии п щкчзов можно исполь зовать дешифрагор (8205 ти ^S^"1) Микросхема 741 S25 / не рекомендуется из за возможних выбросов напряжения, когда она переходит в вьп ок '»имнеданснос состоя ние или выхотит из него

Являясь ведущим, контроллер дочжен выводигь также необходимые сигналы считы вания/залиси Это уже знчкомые нам сигналы

10К' (считывание ввоца-вывода) ,'MEMR (считывание из памяти), lOW (запись ввода-вывода) и1МЕМЛУ (запись в память) Так как эти сигналы не соответствуют выходным сигналам ^D,"WR и Ю/М микропроцессо ра 8088 в минимальном режиме, для преобразования сигналов контроллера потребую ся схема кодирования сигналов считывания/запит (рис 9 ^9) Во время передачи ПДП контроллер запрещает выхсгы схемы кодирования считывания/записи сигналом AFN Конечно, интерфейсы памяти и ввода-Bi гвода в слстсме необходимо спроектировать так чтобы они реагировали на сигналы MFMR, MFUW

T<7R, "КЖ вместо сигналов "RD "WR и Ю/Ч Как и в процессоре, сигнал КГ AD\ применяется s 1я расширения циклов шины при обслуживании медленных угтройсгв посредством введения сосгоянлй ожидадия Сигнал RESET сбрасывает регистры управления, остояния и временною храпения и флажки запросов, л также Уетанавливчет ф гажки масок Гииия FOP - двунаправлен ная При достижении счетчиком нуля на ней формируется отрицательный имчуль кото рый лиС'0 (лу-кит запросом прерывания ибо подается ч интерфейс v тройствч Ро и ин тщфейс может выдать на эту линию сшнал с активным ьизким уровнем В люЭом сту чае ыпкий \ровень на линии ГОР приосгана"г i в°ет бло)- овую гнр^м1^ После приогга HOBK-f се молсо воюбновить в соответствии с режимом ра^оти ьочтрптсра 8^37

В составе коюроллера име ;ея риис^ры управления, состоя ыя и временною хра нения a ^i же четыре канала Каждый каьал имеет свои регипр режима тек пш" рг гкс р адреса базовый регистр адреса, текущий регистр счетчика баЛь базовый регистр счетчика б йт, флажок запроса и флажок маек» Каждый лз kihi ю-ц допускает ?^боту в отцом из четырех режиг^ов, текущий рсжип определясгся битами 7 и 6 канггьного ре гистра режима Кратко охарактеризуем режчмь! работы контроллст

Режим одиночной передачи (01) После калдой перепачи контроллер oci »бождает шину процессору минимум на один цикл шичы, но сразу же начинает щ сверку входэв DREQ и, как только обнаруживает активный игаал инициирует следующую передачу

Р"жим блоковой передачи (10) Активный сигнал DRbQ должен сохрдня^ь^ 1 те ii,»u до формирования активного сигнала DACK после ч г о шияа т»е о^нобожгл? с я то ч в^рпд ьлч пре^ачи вгего 1пока

Режим передачи по требованию (00) Аналогичен предыдущему но послр каждой пе ре ^ачи провсряегся сигнал DRbQ I ели он пассивный передачи приостанавливаются до тех пор 1юка сигнал DRT О не будет активным После этого передача про юлжается с той точки в коюрой она была приостановлена Данный режим позволяет интерфейсу остановить передачу если устройство не может продолжать ее

Каскадный режим (11) Обеспечивает каскадирование конгроллеров 8237 для слу чая когда в подсистеме ПДП требу eir-я более четырех каналов При каскадировании контроллеры второго уровня подключаются к контроллерам первого уровня линиями HRQ к DREQ и HLD4 к DAC К Объем данной книги не позволяег рассмотреть этот ре жим подробнее

В любом режиме при достижении счетчиком нуля формируется сигнал ЕОР = 0 и пе редача прекращается

Бит 5 в регистре режима определяет инкремент (0) или декремент (1) регистра ад реса после каждой передачи т е идентифицирует порядок запоминания данных в памя ти Когда бит 4 содержит 1, разрешается автоинициализация При начальной загрузке те кущих регистров адреса и счетчика байт их содержимое помешается также в базовые регистры адреса и счетчика байт Если автоинициализация разрешена, при достижении счетчиком н\ля содержимое базовых регистров автоматически передается в текущие ре гисгры Биты 2 и 3 определяют тип производимой передачи контроль (00), запись (01) и считывание (10) Контроль предназначен для проверки информации, относящейся к предыдущей операции ввода или вывода и фактически не связан с текущей передачей Мы не будем подробнее останавливаться на контроле Два младших бита при выводе в регистр режима идентифицируют выбираемый канал ПДП

Кроме блоковых передач между памятью и устройствами ввода вывода или внешней памятью, контроллер 8237 может управлять передачами памяти - память При этом бай ты из области-источника помещаются во внутренний 8-битный регистр временного хранения, а затем передаются в область-получатель Следовательно, для каждой передачи па мять — память требуются два цикла шины Для адресации источника применяется теку щий регистр адреса канала 0 Текущие регистры адреса и счетчика байт канала 1 обеспе чивают адресацию получателя и счет Инкремент или декремент адреса получателя необ ходимо производить как обычно, но при } становке соответствующего бита в регистре управления адрес источника можно сохранять кетменным При этом один и ют же байт данных передается во всю область получатель

В регистре управления передача память - память разрешается установкой бита 0 в состояние 1 гри этом единичное состояние бюд 1 показывает что адрес источника необ ходимо сохранять неизменным Бит 2 применяется для разрешения (0) или запрещения (1) контроллера а бит 3 определяет тип синхронизации I ели позволяет быстродействие сисгемы бит 3 можно установить в о юянле 1, определяя сжатую синхронизацию В этом сгуча» для випоч {"ния бог[ьшинс1ва передач требуются всего дьа такта синхро низании (^м imet) Бит ч чре ^e^гeт фиксироч-яны уз и циклические (круговые,» приоритеты Обычно к-и ал 0 имеег высший приоритет, а канал 3 - низший, но если бит 4 содержит 1, приоритеты после каждой передачи циклически изменяются Например, если до передачи бьли приоритеты 2 л 0 1 то после передачи ohf станут 3012 Цикли ческое изменение приоритетов позволяет контр шеру предотвратить монополи $ацию Шины одним каналом При использовании оСычь >й еинхргшэяци-i контроллер допуска ет программное определение продол кителььосш сигналов TOW h'hehw Состояние 1 бита 5 показывает, что эти сигналы расширяются на два тактд синхронизации Програм ма может тч^жс определить vpo^e^ активно и сиги1 ов Р ^> h DACK установкой юи I Гро ом бита (\ (bki '')) и б( ia 7 'и ( ст. 'н е би а 6 показывв1 т что DRI-'Q имеет активный низкий уровень, а бита 7 -- что DACK имеет активный выг кий уровень. Установка состояний этих бит зависит от характеристик тины

В регистре состояния младшие 4 бита показывают состояния счетчиков четырех к-d налов, а старшие 4 бита фиксируют наличие или отсутствие запросов ПДП. Для млал ших 4 бит состояние 1 бита п показывает, что в канале п счетчик достиг 0; для старши? 4 бит состояние 1 бита п + 4 сигнализирует о наличии запроса в канале п.

В каждом канале имеются также флажок запроса и флажок маски. Запрос ПДП мож но запрограммировать так, как будто подается сигнал DREQ. Установка в канале флаж ка запроса имеет те же последствия, что и активный сигнал DREQ; флажок сбрасывает ся активным сигналом ЕОР. При установке в состояние 1 флажок маски запрещает ка нал, поэтому запросы ПДП (аппаратные или программные) не распознаются. Если кана! не запрограммирован на автоинициализацию, флажок маски автоматически устанавли вается активным сигналом ЕОР. Флажки запроса и маски программируются с помощьк приказов, в которых бит 2 определяет состояние флажка, а биты 1 и 0 задают номер ка нала. Остальные биты приказа не используются. Предусмотрен также приказ воздей ствия сразу на все 4 флажка масок. В этом приказе состояние бита п переводит в знало гичное состояние флажок маски канала п.

Кроме приказов, определяющих состояния флажков, имеются приказы главной сброса и сброса триггера первый/последний. Приказ главного сброса имеет те же послед ствия, что и сигнал RESET. Триггер первый/последний предназначен для загрузю 16-битных регистров адреса и счетчиков. Так как контроллер 8237 может одновремен но воспринимать только по одному байту, загрузка каждого регистра производится дву мя операциями вывода. Если первоначально триггер первый/последний находится в со стоянии 0, первый выводимый в эти регистры байт загружается в младший байт, а триг гер устанавливается в состояние 1. При выводе второго байта единичное состояние триг гера направляет его в старший байт. После этого триггер сбрасывается в состояние О Приказ сброса триггера первый/последний предназначен для инициализации триггера дс производства операций вывода. Ни один из двух рассмотренных приказов не связан s передачей данных по шине данных. Они автоматически выполняются контроллером когда осуществляется запись по соответствующему адресу.

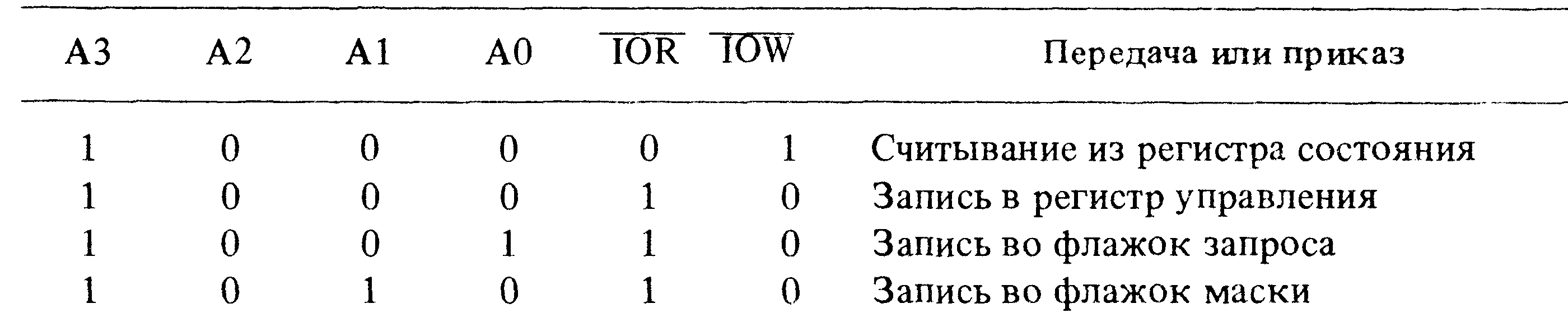

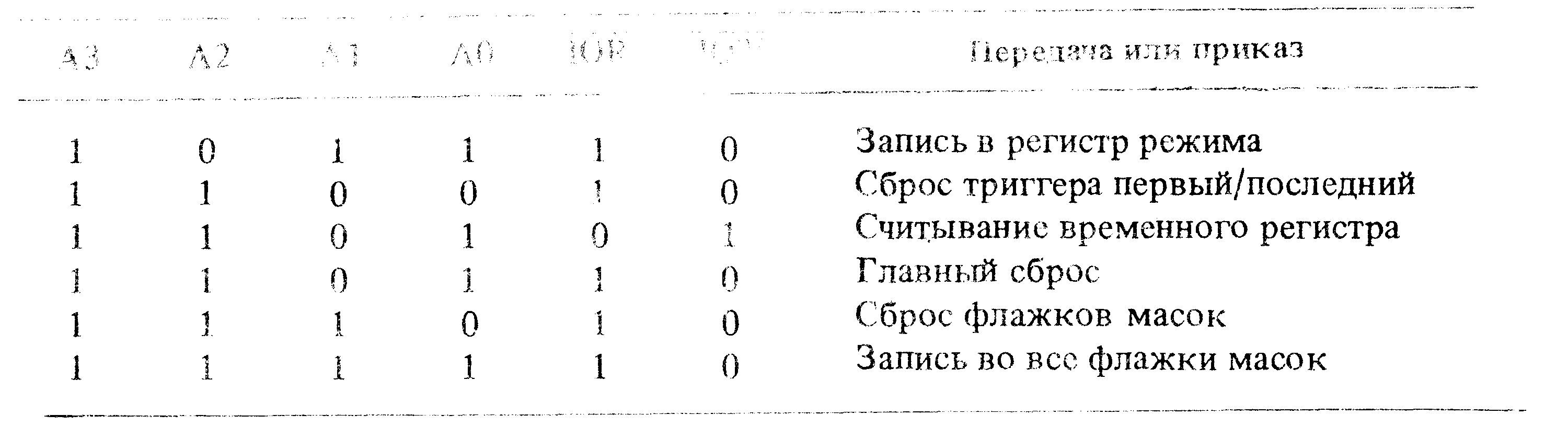

Адресация разнообразных регистров и приказов осуществляется с помощью лини^ CS, IOR, IOW и АЗ-АО. Сигнал

CS == 0 определяет обращение к контроллеру. Сигна;

A3 == 0 при адресации регистров адреса или счетчика и A3 = 1 при обращении к регист рам управления или состояния, а также при выдаче приказа. При адресации регистре! адреса или счетчика линии А2 и А1 определяют номер канала; АО == 0 задает текущий регистр адреса и АО = 1 — текущий счетчик. В операции считывания IOR == 0 и IOW = = 1, а в операции записи 10 R = 1 и tow = 0. Запись в текущий регистр адреса или счет чик одновременно загружает в соответствующий базовый регистр. Суммарные сведеню по адресации сведены в табл. 9.5.

Таблица 9.5

Адресация в контроллере ПДП

Отметим, что наименьший адрес порта, назначаемый контроллеру. 8237, должен быть кратным 16, Регистр временного хранения можно считать только по завершению всей блоковой передачи память — память. Все не показанные в таблице комбинации являются недопустимыми.

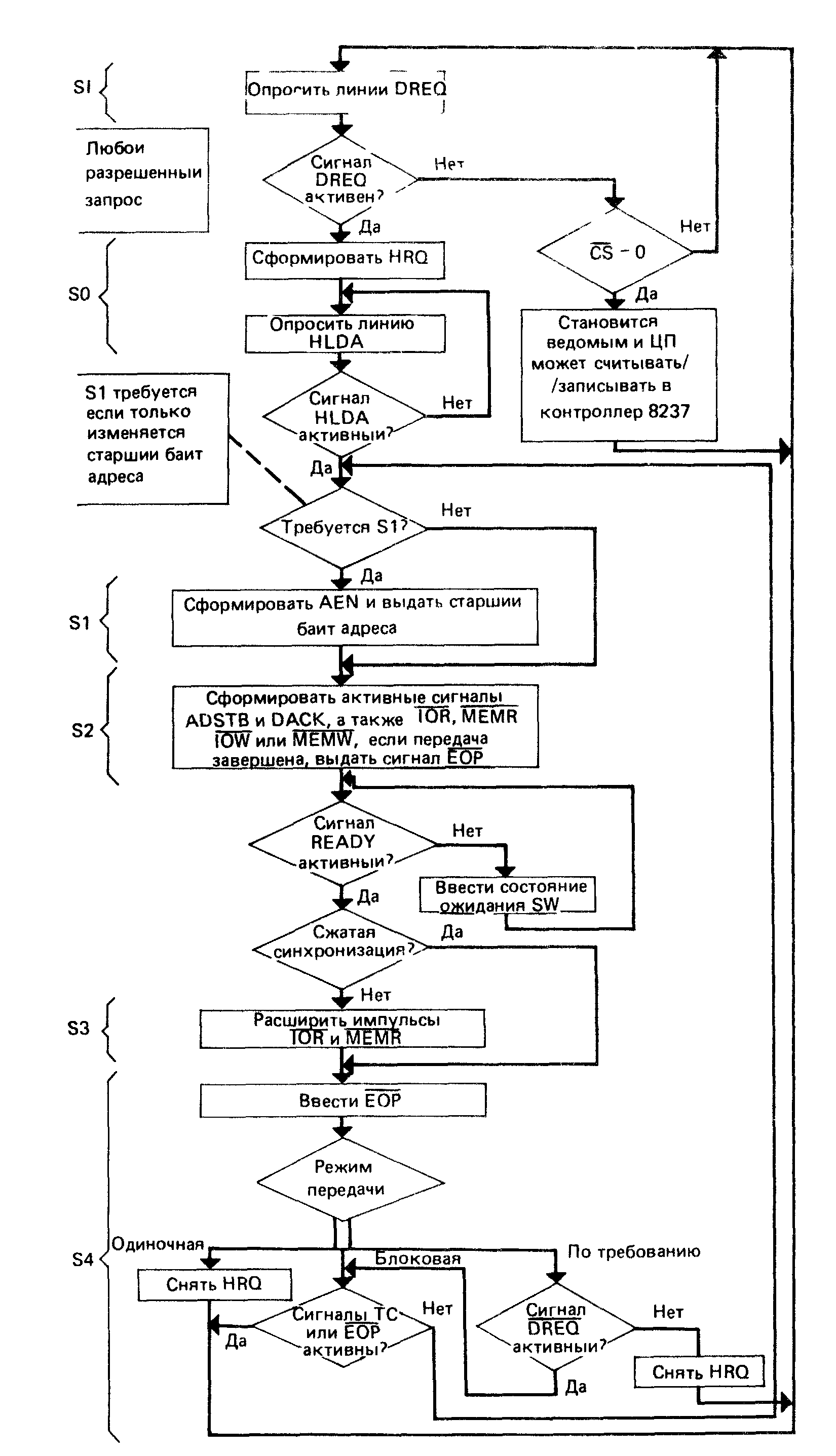

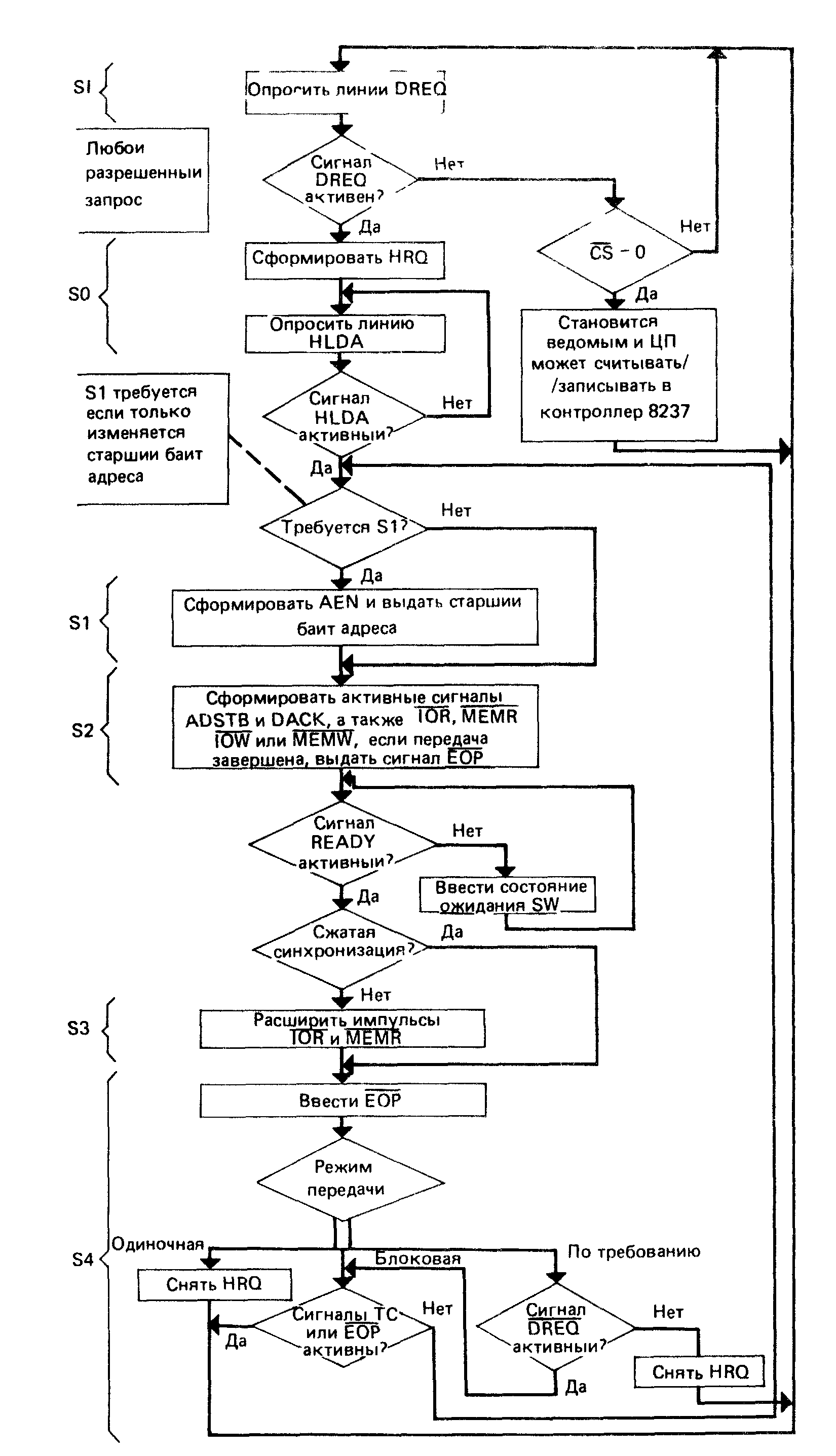

Действия контроллера во времени разделяются на состояния SI, SO, SI, S2, S3, S4 и SW (см. схему на рис. 9.40). Между передачами контроллер реализует последовательность холостых состояний SI. В каждом состоянии SI производится проверка линий DREQ — не запрашивается ли передача ПДП. Если CS

— 0 и все сигналы DREQ пассивны, контроллер превращается в ведомого и с ним может взаимодействовать процессор. При наличии активного сигнала DREQ формируется сигнал HRQ и контроллер переходит в состояние SO. Состояния SO повторяются до получения ответного сигнала HEDA, после чего контроллер повторяет состояния S1-S4. Состояние SI можно пропустить, если старший байт адреса передачи изменять не нужно. Когда в передаче участвует устройство, которое не может реагировать достаточно быстро, вводятся состояния ожидания SW. В обычной синхронизации необходимы состояния S3, но, если шина и интерфейсы допускают сжатую синхронизацию, состояния S3 удаляются. В состоянии S4 проверяется режим передачи и, за исключением незаконченной передачи блока в режиме блоковой передачи и в режиме по требованию, выполняется возврат в состояние SI. Временная диаграмма передачи из интерфейса в память представлена на рис. 9.41.

9.6. КОНТРОЛЛЕРЫ НАКОПИТЕЛЕЙ НА ГИБКИХ ДИСКАХ

Для хранения больших объемов данных в основном применяют дисковые и ленточные накопители, хотя определенное распространение получает и ЦМД-память (память на цилиндрических магнитных доменах). Пока ленты и диски имеют такие преимущества по сравнению с ЦМД-памятью, как транспортабельность и емкость. Ленты имеют меньшую удельную стоимость и более долговечны, но зато диски обеспечивают намного меньшее время обращения. Выпускаются ленты и диски разнообразных размеров и форм, поэтому аппаратура считывания/записи также отличается разнообразием. Подробное рассмотрение магнитных внешних накопителей выходит за рамки настоящей книги; мы остановимся на самых популярных сейчас носителях для микросистем - гибких дисках (дискетах или флоппи-дисках}.

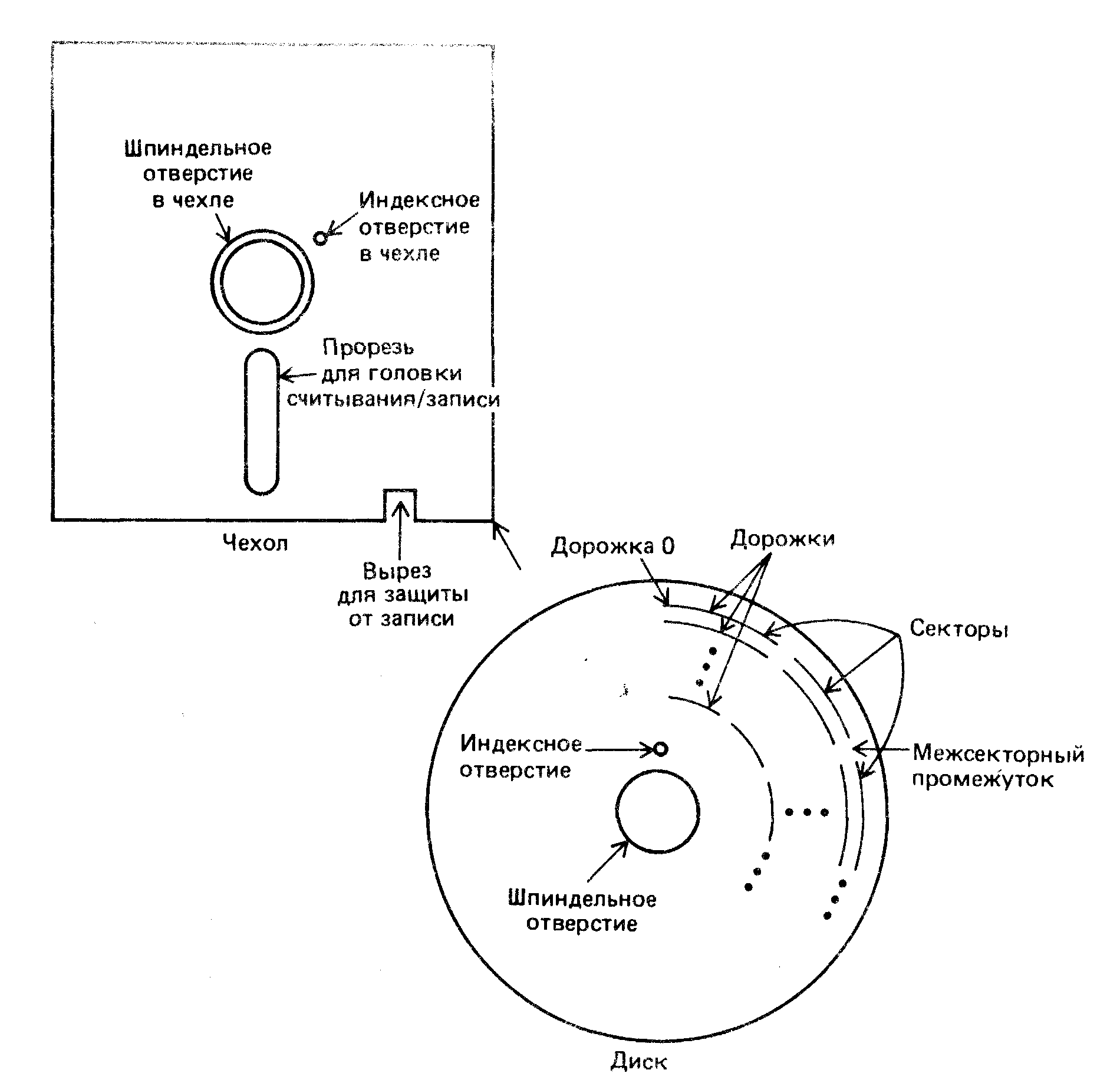

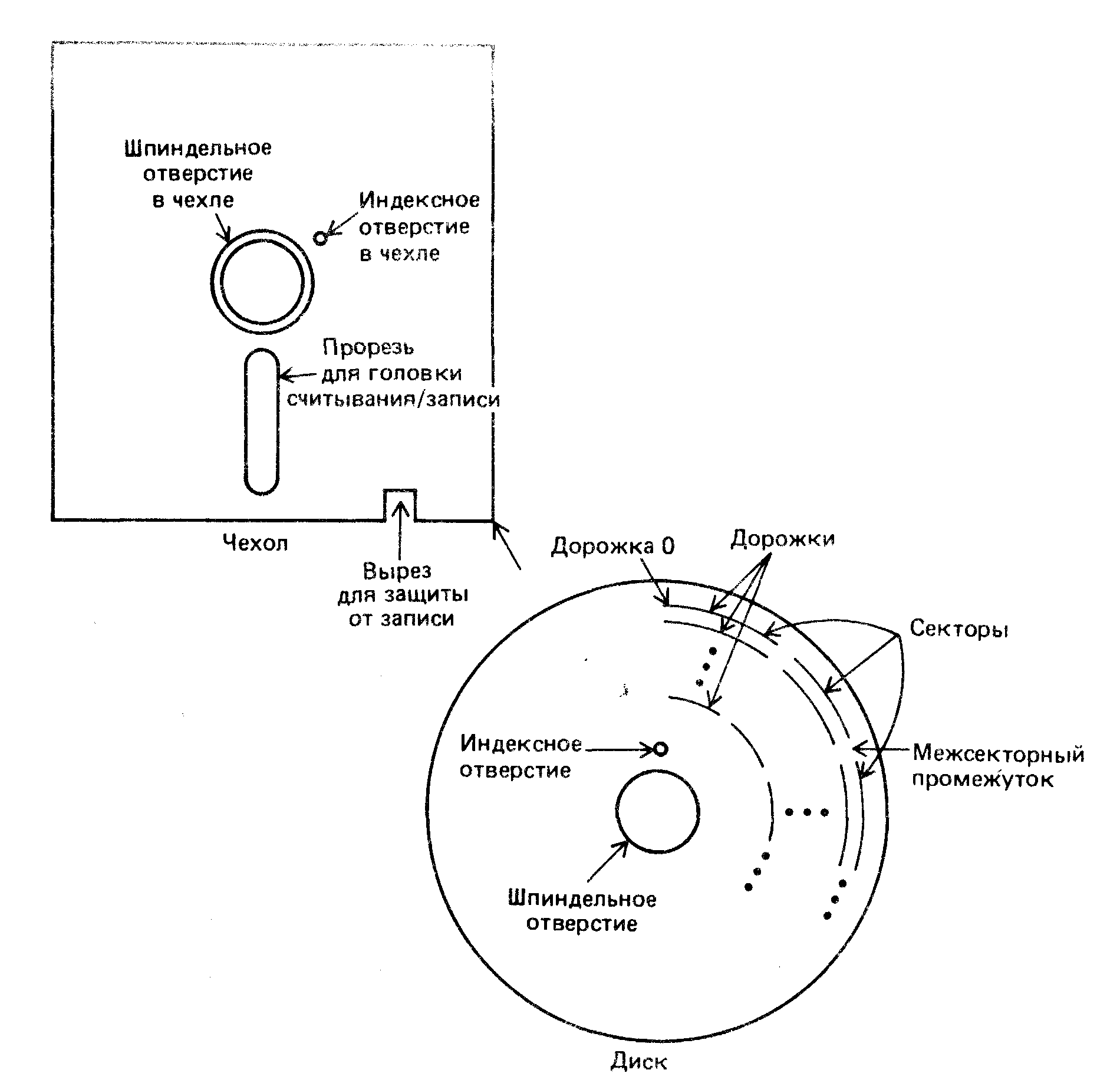

Физическая конструкция гибкого диска и общий формат хранения данных представлены на рис. 9.42. Гибкий диск имеет майларовую основу с нанесенным на нее магнитным покрытием. В центре находится шпиндельное отверстие, а на некотором смещении от центра имеется минимум одно индексное отверстие. Назначение индексного отверстия — обеспечить накопителю отсчетную точку при считывании или записи данных. Гибкий диск помещен в квадратный чехол, в котором также имеются шпиндельное и ин-

Рис 941 Типичная временны диа1рамма работы контроллера 8237

декспос отверстие Кроме того, в чсхчс есть прорезь для контакгирования головки (чи тывания/записи с ювсрхпосгью дис1 а и вырез защиты oi записи

Данные хранятся в последовательной форме на концентрических окружностях, назы васмых дорожками, и группирую гся по дугам, называемым секторами В некоторых накопителя имеется одна головка считывания/записи и данные хранятся только на одной поверхности диска, а в других есть две головки и используются обе поверхности диск! Во втором случае пары дорожек, находящихся ч1 одном и том же расстоянии от ценгра дис1<а, называются цилиндрами

Стандаршые гибкие диски имеют размер стороны чехла 203 и 133 мм (минидиски) Различают диски с программным разделением на секторы, когда диск имеет одно ин декснос отверстие, и с аппаратным <огда 'тело отверстий равно числу секторов Клж дый сектор должен начинаться со служебной информщии, которая отмечает начало сек тора, и только первый ^скгор на порожке отмечается индексным отверстием Во втором случае вес секторы отмечаюгся индексными отверстиями

Дорожки (и цилиндры) пронумерованы, причем внешняя дорожка имеет номер О Секторы 1акже нумеруются, и в диске с пр01раммным разделением на секторы первый .Сектор после индексною отверстия имеет номер 1 Когда диск помещается в накопитель, шпиндель проходи! через отверстие, диск сцепляется со шпинделем и вращается В чехле со скоростью 360 об/мин Подвижную головку считывания/записи можно пози t

—=—

Р чс ^ 4(1 С\ \ ) действий контроллера 8237 «то состоякиям

Рис. 9.42. Конструкция гибкого диска

ционировать на любую дорожку, после чего вращательное движение заставляет все секторы выбранной дорожки проходить под головкой, обеспечивая тем самым доступ к отдельным секторам. Для выполнения записи или считывания головка опускается (загружается) на поверхность диска через прорезь в чехле и позиционируется на нужную дорожку. В диске с программным разделением на секторы накопитель ожидает появления сигнала от индексного отверстия, а затем начинает считывать служебную информацию о формате сектора. После нахождения нужного сектора начинается собственно операция считывания или записи. В случае диска с аппаратным разделением на секторы требуемый сектор находится с помощью сигналов от индексных отверстий.

Необходимое для доступа к сектору время складывается из следующих составляющих:

Время загрузки. Для приведения головки в контакт с поверхностью диска. Время позиционирования. Для позиционирования головки на дорожку. Вращательное запаздывание. Для поворота диска до достижения требуемого сектора. Средние значения этих времен равны 16, 225 и 80 мс соответственно. Когда сектор найден, средняя скорость передачи данных составляет (байт/с) :

Чяспо байт в секторе > число (.ькюров на дорож] ^ а (.короаов пб'с (здс<,ьучшывл ется время прохождения промежутков между данными)

Рассмотрим более подробно конкретный тип гибкие дльк^ 200 мм л,иск с при граммным разделением на секгоры, совместимый с накопителем 3740 фирмы IBM Диск имеет 77 дорожек с 15 (одинарная плотность) или 26 (двойная плотность) секторами, хотя в напшх примерах допустимое число секюров варьируется от 8 до 26 Обычно используются 7 Ч дорожек 1 с допк каются две д< фен тыс гро»ки Р-Ротаиг" дорож ки н", меруются от 0 до 74

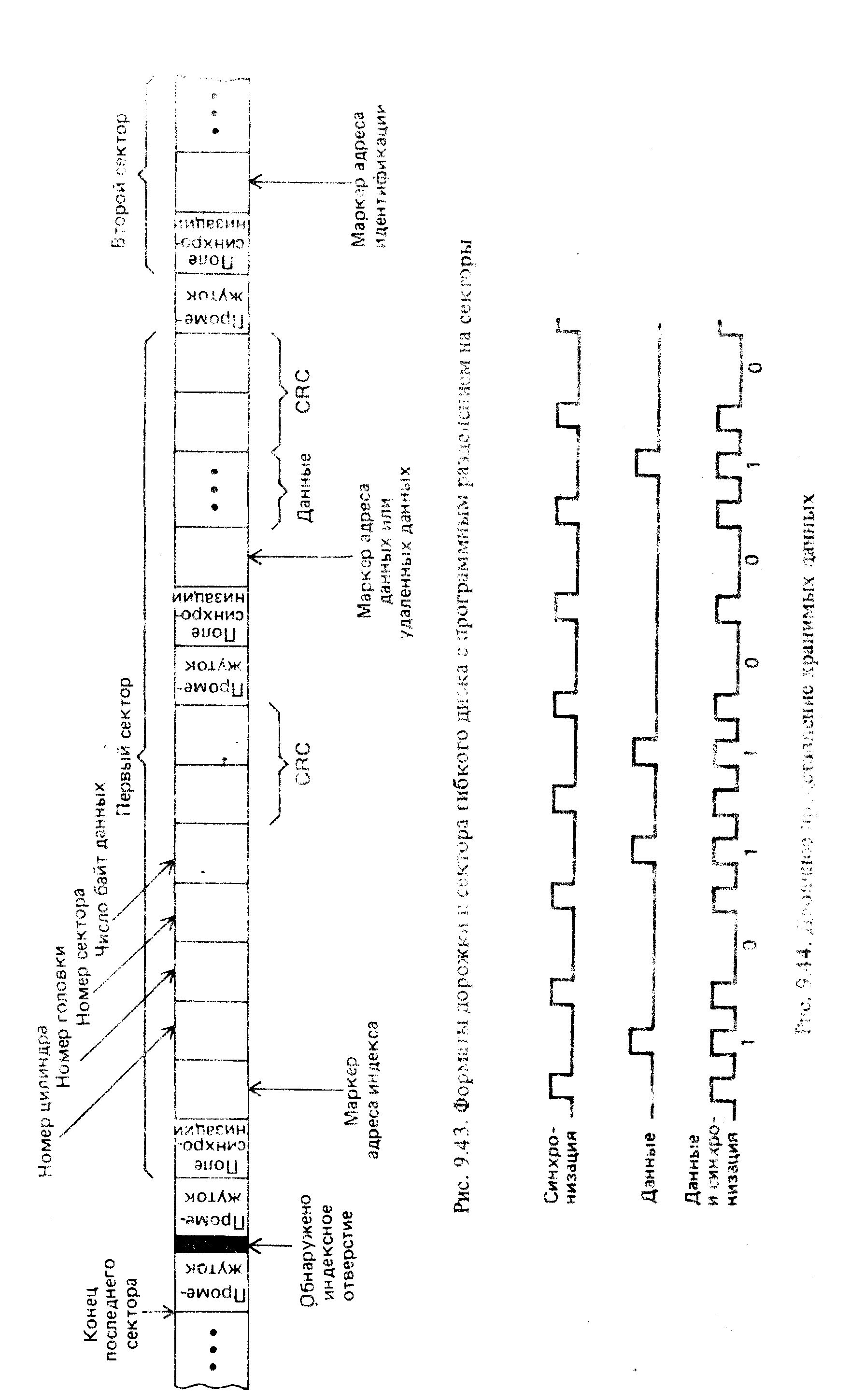

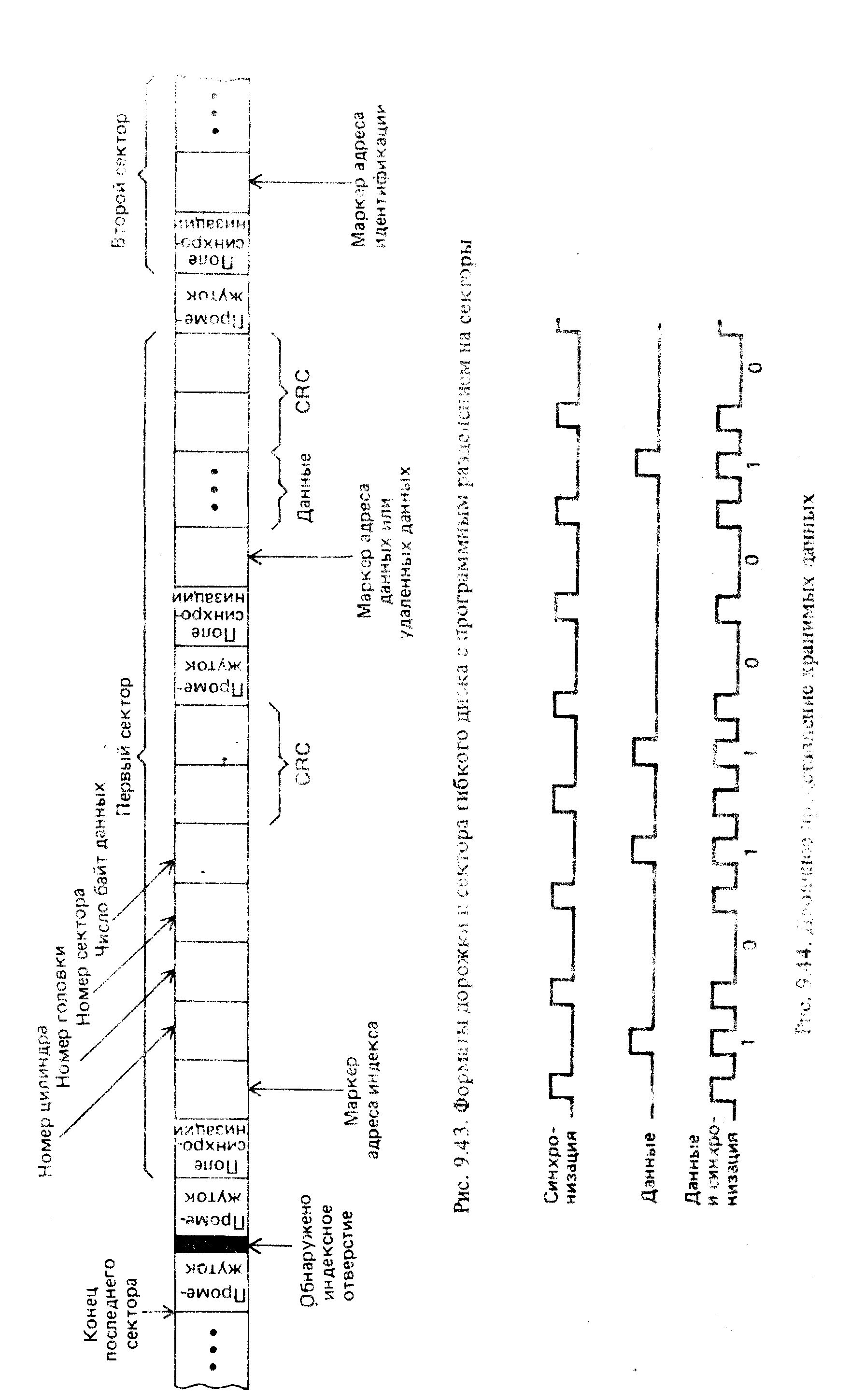

Форматы дорожки и сектора рассматриваемых дисков показаны на рис 9 43 Межд> смежными секторами находятся промежутки, и сигнал от индексного отверстия должен появляться в промежутке между последним и первым сектором дорожки. Каждый сектор содержит поле идентификации и поле данных, оба из которых начинаются с поля синхронизации. Между двумя полями имеется промежуток, необходимый для коммутации головки на выполнение заданной операции. Поле идентификации начинается с маркера адреса, после которого следуют номер цилиндра (или дорожки), номер готовки, номер сектора, число байт данных в секторе и два байта контроля ошибок

Маркер адреса в пo^e идснтифик^чил первого сектора обычно огличается от маркеров в других секторах, а маркеры адреса в полях идентификации отличаются от маркеров в полях данных. Кроме того, маркеры адреса в полях данных различаются в зависимости о г того, содержит поле полезную информацию или занято байтами-заполнителями

Имеются два главных метода генерирования байт контроля ошибок Один из чих заключается в получении контрольной суммы посредством суммирования всех байт в поле, находящемся перед контрольной суммой (с игнорированием переносов). Во втором методе биты поля считаются коэффициентами одного двоичного полинома, а байты контроля ошибок являются остатком от деления эгого полинома на фиксированный поли-

Рж 94S Орг<ш wr \} оп-pfi л ра накопителя на гибком диске

ном степени 1й (меюд наэывлеюя ц^кличе^, им иЛьпочным к^тролем ( К( ) Д.1 к;' предполагается применение метода CR<"

Hd рис 9 44 показано цвоичнос представление последовательно хранимых дднньгх Информация группируется в элементы, каждый ич когорых разделен на четыре интерва ла; в первом интервале находичся импульс синхронизации 1рр1ий интервал предназн^ чен для бита данных и будет содержать импульс есчи биг ушных равен 1 Гипично! зн>. чение временного отрезка элемента ^остаичяет 4 мкс (при скор )ии 360 об/мил)

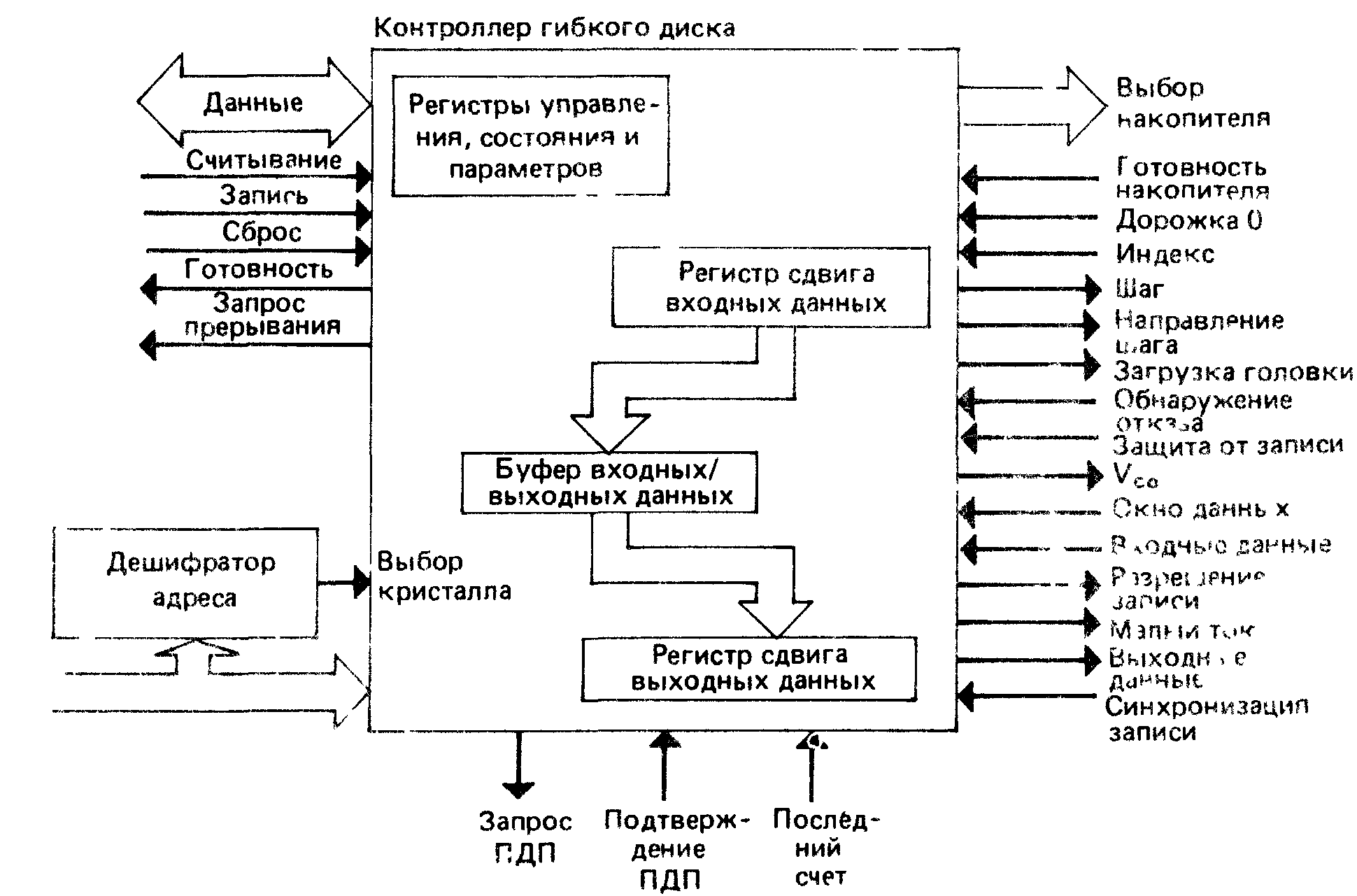

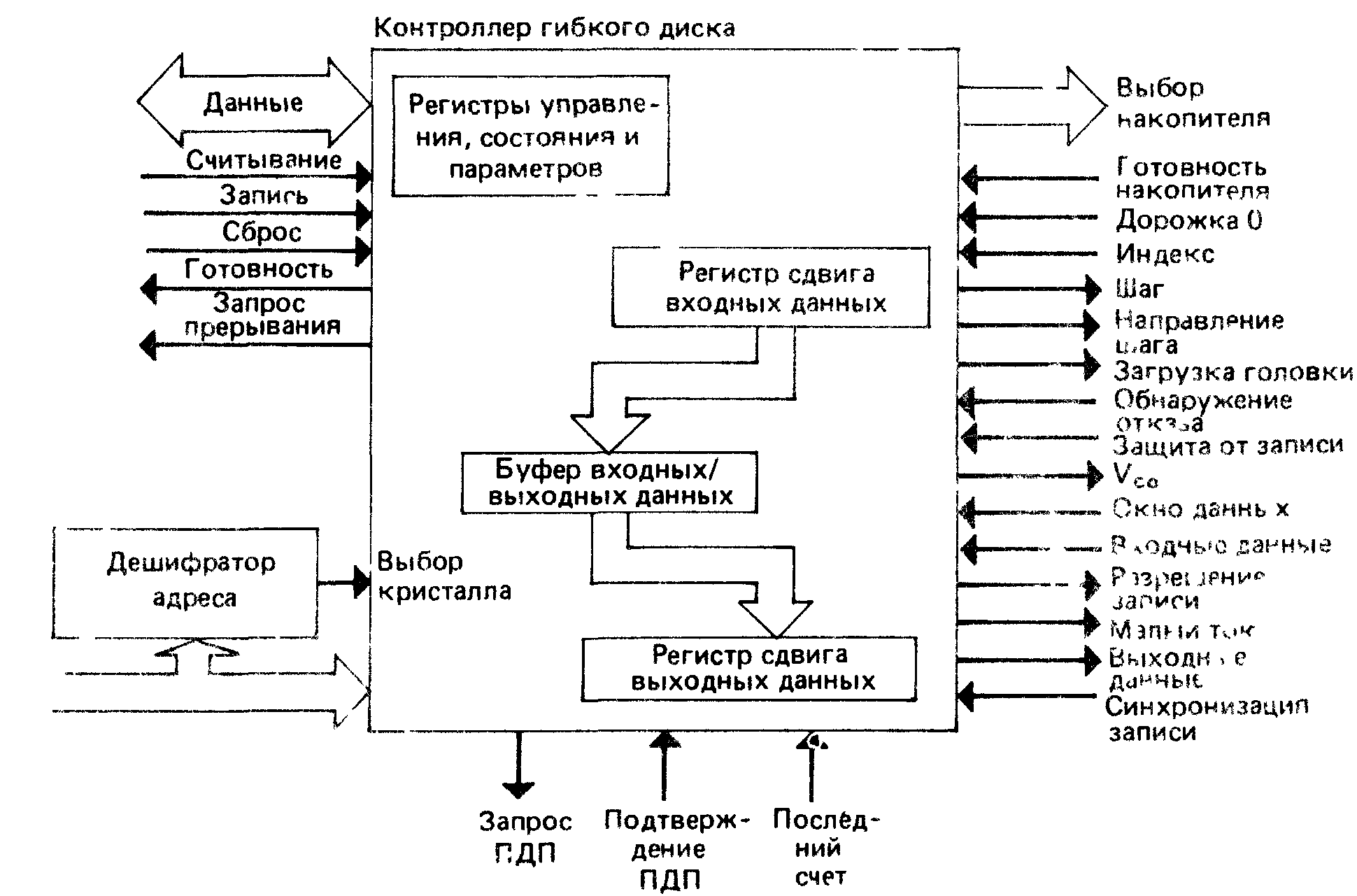

Рис 945 иллюстрируй ор)аниз.ш,ию шпичного кочтголчера чакопшеля на гиб)- ( м диске, а рис 946 показываег моего контроллера в подсистеме внешней память на 1 ,v;

ком диске. Из-за последовательного хранения информации входы и выходы накопи ie-ля представляют собой двоичные потоки. Поэтому входные байты принимаются в регистр сдвига и затем передаются в буферный регистр данных, а выходные данные загружаются в регистр сдвига, из которого они выдвигаются в последовательной форме Выходные схемы должны объединять импульсы со входа синхронизации записи и биты данных так, чтобы получался формат, представленный на рис 9 44

P'ие 946 Подсистема гибкого дискд

Jt^t и t WiiHh bOKOHS?Uilt1 <. h pu » » -l На ^i'jlttB ItfUlK Hi^^KU H ElM»t I t-KOI 1.

f Ji^f^ii h^KOiopbie контакты ь^Нх роллера не-^кодимо зарезьрвироВйТь -^ я !иний вы

6iJi .* iS-^OtlriT^i Kp0*.i^ Т 5Г^ ^0„ ЛАЫ ОЫ^Ь ^а» И./ ВЫ>^ДЫ ь HdKt ^ItClb каг. ЛИ1 АЛ ИМ

1 ч^а i^ar». 1 о i j, »iti^ t о i^-южкам m я м си/иала нлп^ h тичля шага р линия

L^ 1-П^ ^ «•И - 1<- U U\U^,I»\ u* ^аКЛ^ В >.J 4iu t LriIIWIbl ПО ^ а ЙШИ^ НДХОЖ

^ i^ *v a„i t t л д,/ j t-к ^,, Hj^eu^uJu^it о аознишо $^нл1-01 Ka^d 11 i ^1ибки, ф» KOi

^ u »t'i^ И ^ l К Av: ii>/i ri t-ll^ ill,» E iOM, 4TiU ГИЬ1 ЙЙ да^К idlU lih...»! 3 jaiHT^^Io 01 ИМ11^ Jibi. »B lhh ^pU)i

ti8^ ^ о Ut. i 4Я^ ^л (1 мои' cp.uuBut юдстройки ч^пош коюоая фо-рмкр}^ си s гы uksu ii л1у t^iMy контроллер должен в ьщавать сигнал синхронизации V^^, Дтя J«^nrtCH ^аиых к^име чигил выходных данных требуются линии разреш.ния записи и мдлогс гокд ,iWii4i Mo. ли 1ока ip^ir^ a lhjh с тем, что npii записи ha вну^рошис зрожь а <их tщ а бо 1»>ш^ ^3) Лри леняетш м »1ьший ток

Lu^ ' ь.^г ий ди^1 имее -ь ^ктиров, ка кдый ^ктор ссдср^л! 1 28 бай1 ^ скоросп ь^^т д L^^i^ чы ЗьО об/мш! средняя ^кирость передачи данных

2й Х 128 Х 360/60 ^ 1996Ь байт/.

« ^ ^li» и i epi о к^^ ьауся ^авны?.* прям sro 50 Mi с С уч^ом iipOMe куков ^с uib ii^ui л<г^иод it», i^a tfii Си^1дй].яе1 j^ мь„ (1щи4 »ikc на 6Hi) Хотя и р»»ижно хущ<. яв^^ть передач ^ гил^л скоритыо без <<онтроллер1 ПДП, применение контроллера икд^ьшлет^я Go^e•'эф<1'еюивным Поэтому контроллеры дисков обычно имею г г-игнати -»ачр01^ !1ДГ1, ид11^р)кд».н»1я ПДП и окончания счета Коотроллер ПДП оказывается лучшим решением еще и потому, что передачи с диска всегда связаны с передачами бло ков, d и» отдельных байт

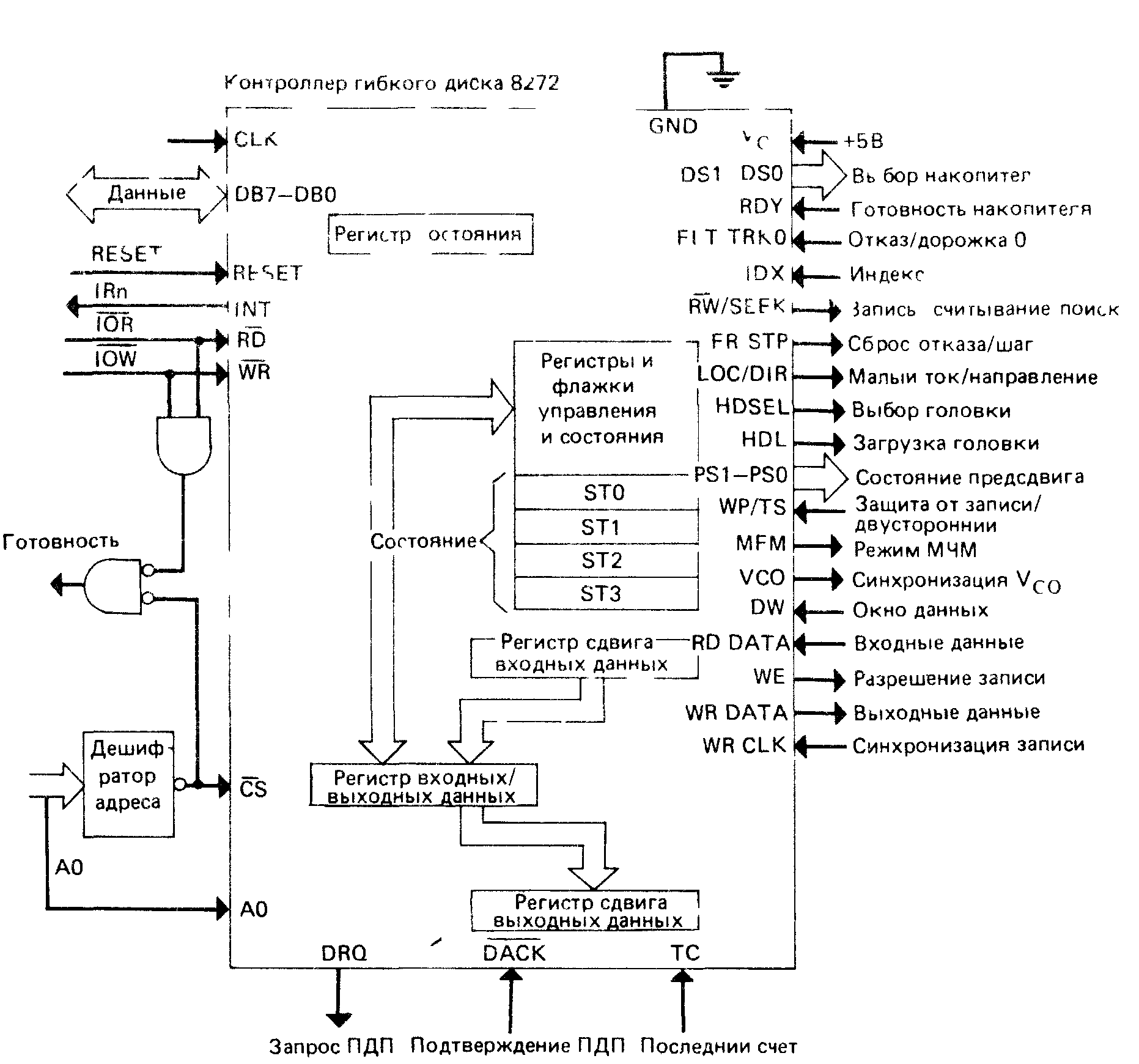

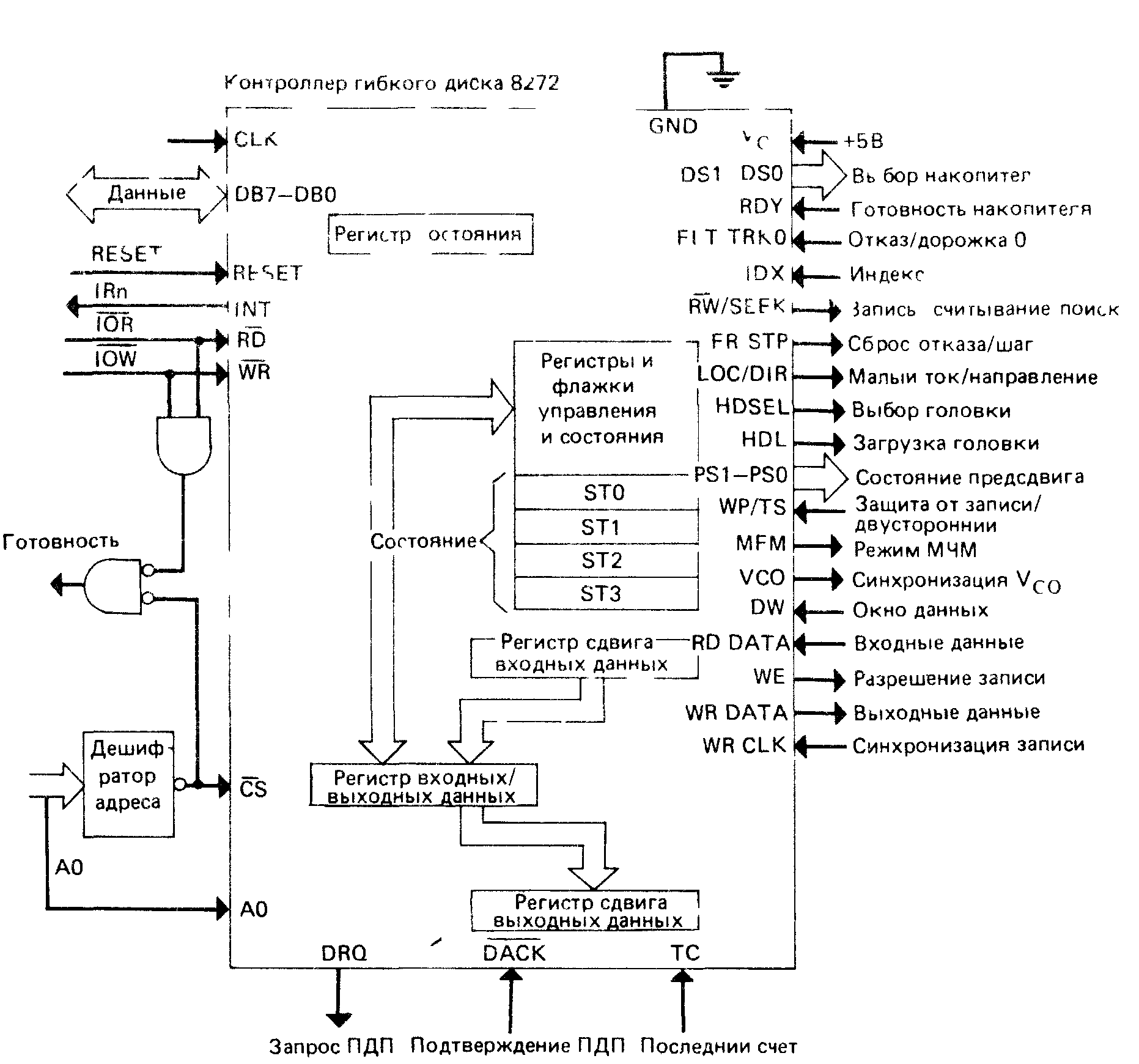

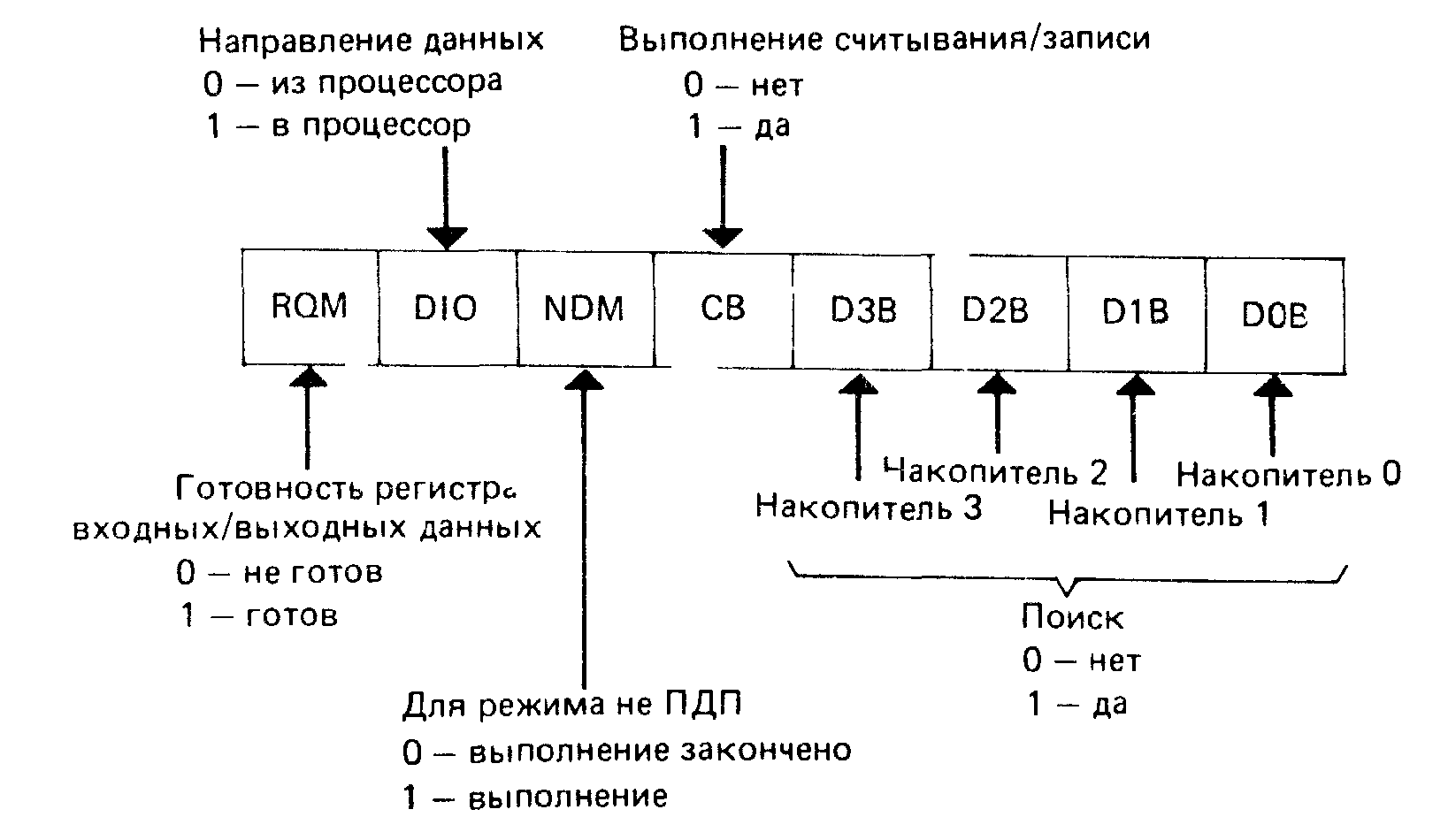

Рди чютрим подробнее типлчьый контроллер диска 8272 фирмы Intel о;» анизлция K^,uf0io noKa-Udd H-t рис 947 В нем имеюгся два регистра которые мо» i адре ^виь

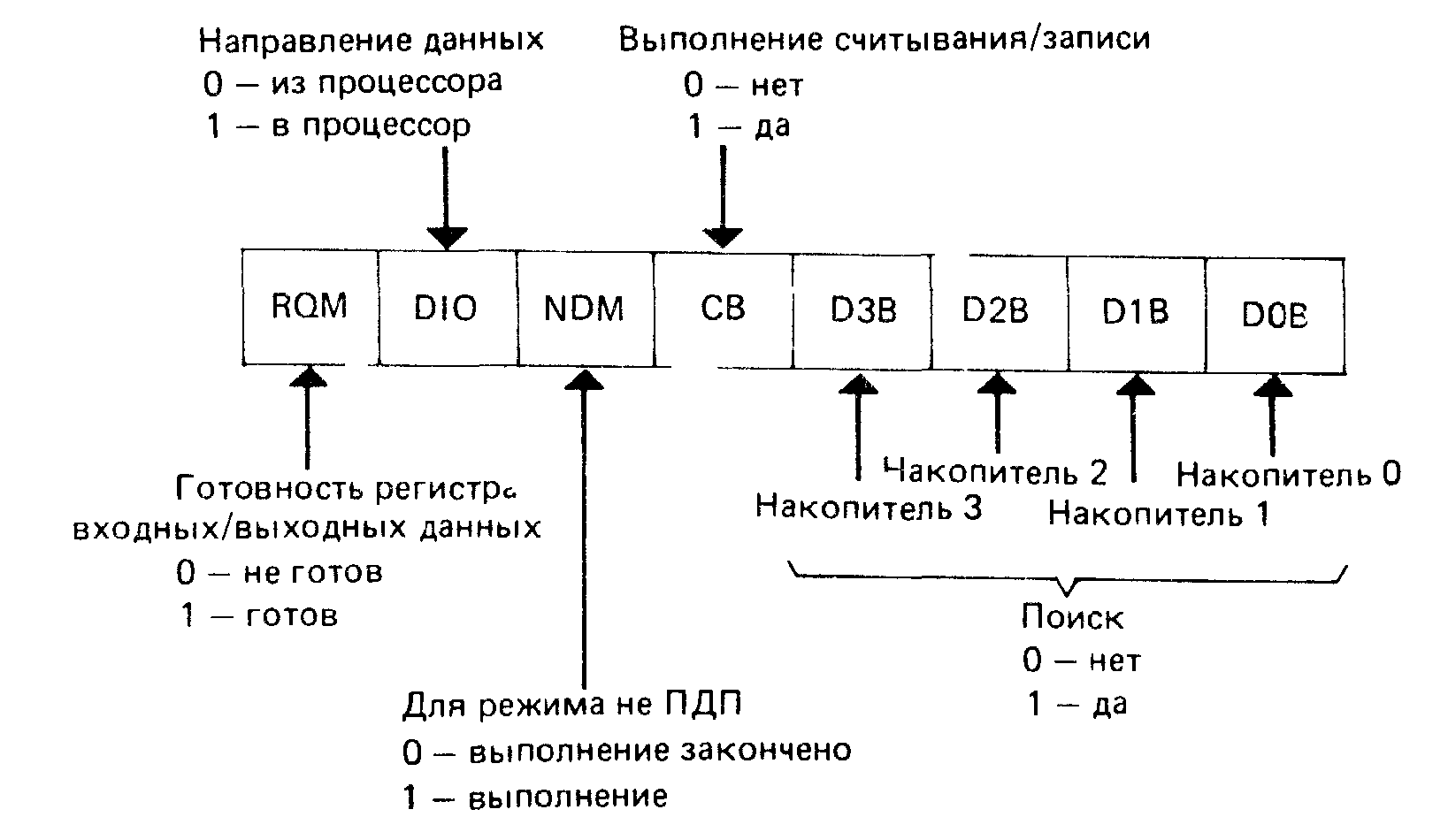

i ^ v^c.wOp р<. И,.^^ СОСТ.О) ЯИЯ, КО-ЮрЫЙ СЧИТЫВа^^Сд При АО = О И ГИГИ^р ВХиД> ^.IX/ri^I

xu ^tbix данных, ибращеии». к коюром' нроизводипя с АО 1 Формат; peiHc'ipd сопол иия прадстлвлен на рис 'у 48 Через регистр входных/выходных данных можно а^рсг-о вагь несколько друшх регистров управления, состояния и параметров, а т«п же hl^koto ко ^пад^рйь Обращение к этим регистрам и флажкам или випо-шениь ввода вывода ^thLii "шредеп&етсм я^^ izi Ооатеяьносгью доступа

Bi-.i ^ шя^-мые контрочлером операции paздe^яютo{ на фазы приказ л выг о^.^ния и р^зулмага Во время фазь! приказа байгы передаюил в ри-истры упра^лен^я и флажки чсре.» регистр входнаЛ/вьц ьдныу данных Зато и i a t j? выпотаения pea шз^^ч^я запро ш нная 011ерация, по завершении коюрои часху.аасг фаза резу плата koi ^а троцесюр ^чкгывает информацию состояния Выв^дь^ в^ вр».мя фазы приказа i< вводы во вр^мя ф»зы резу 1ьтата выпочняются о побайтными п р^дачами лотя любыми пс 1^.дач1ми дан ttb.\ ь^ в^е ля фазы вья олн н л обычно j правпяет контроллер ПДП

Уэ» ^^"^sp 1^бко^ 4h д и »ei.t следую ..дир приказы

Счш^ть ^ш ••i Сч i.^ib ^arfHbit- из иол>1 данных на гибком диске

janA-ait- винные ^ дш п.аег дан ib e в ноле данных на гибком усе

Ottiit.ib удаленные данные. Считывает данные из поля, отмеченного как у ^ал-н {оь

Записать удаленные данные. Записьюает млркер адреса удаленных данные и по\киУ

ет симьо-ш заполнители в поле данных

Считать дорожку. Считывае! поля данных всей дорожки

Считать ID Считывает поле идентификации

Форматировать дорожк} Записывает на д >рожку форма-ihp' юту ю информацию ис

пользуя выданные программой параметры форматирования

Рис 947 Схема контроллера гибкого диска 8272

Рис 948 Формат р1гистра состояния контрочлер1 8272

Сканировать до равно, сканировав до меньше или равно, сканиреааэь ч^ 1ч ь ин 'ч равно. Сканируе! данные на ука данное условие и формирует запрос прерывания ш>г' условие удовлетйоряется.

Инициализировать. Вызывай} перемещение юловки на дорижку U

Считать состояние прерывания. Гчтывае! информацию состоянья ri3 М'' ы .. '<„ 1;

рываний, вызванных изменением линии тоговносш и спер.Щп.й гож sa

Определить., Усканаьли^.л с^ирсс ч шаи51? i4->rioe' |

|

|

Скачать 3.89 Mb.

Скачать 3.89 Mb.