Лекции по ВМСС. Конспект лекций по курсу "Электронные вычислительные машины, системы и сети"

Скачать 3.89 Mb. Скачать 3.89 Mb.

|

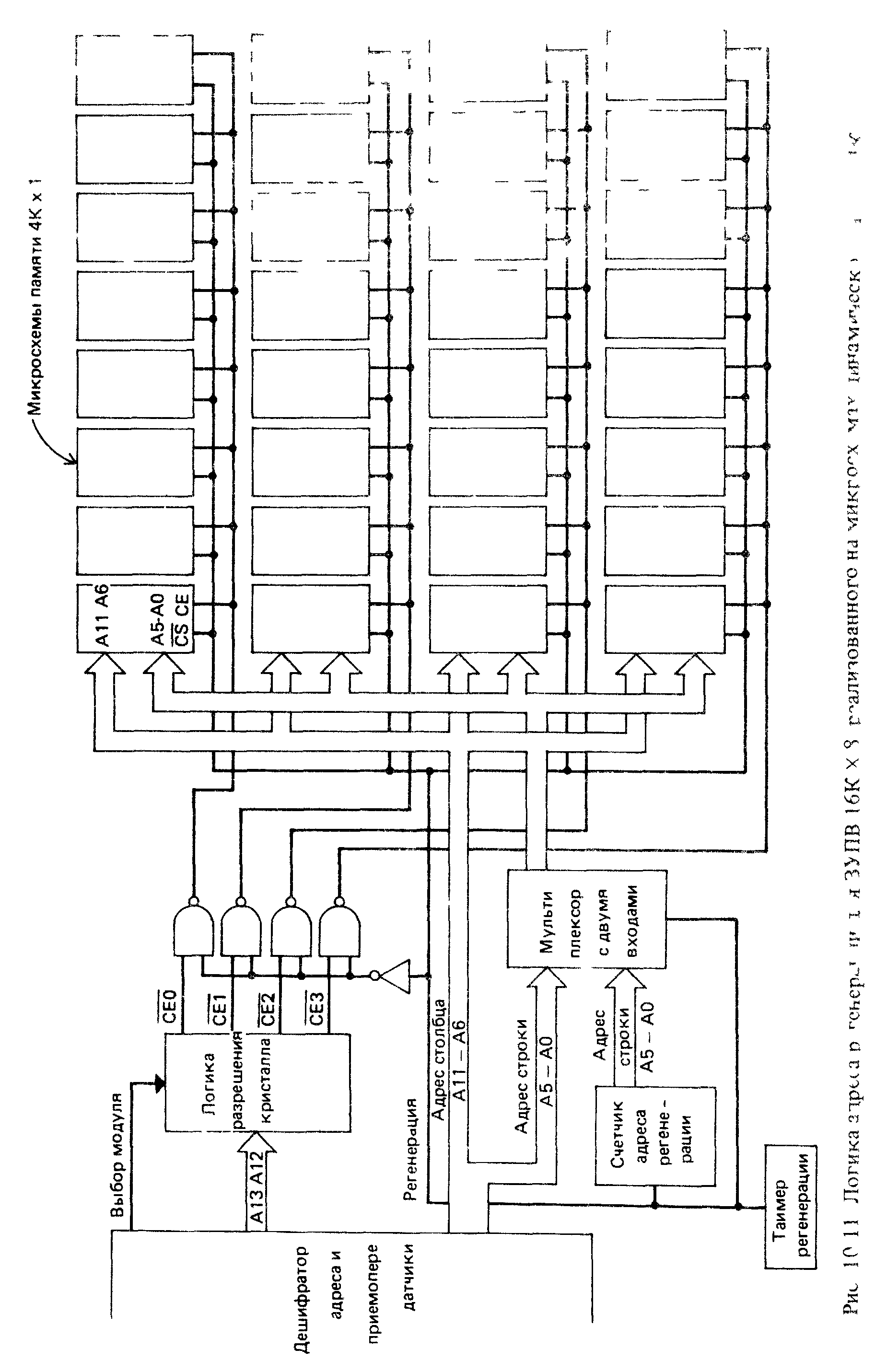

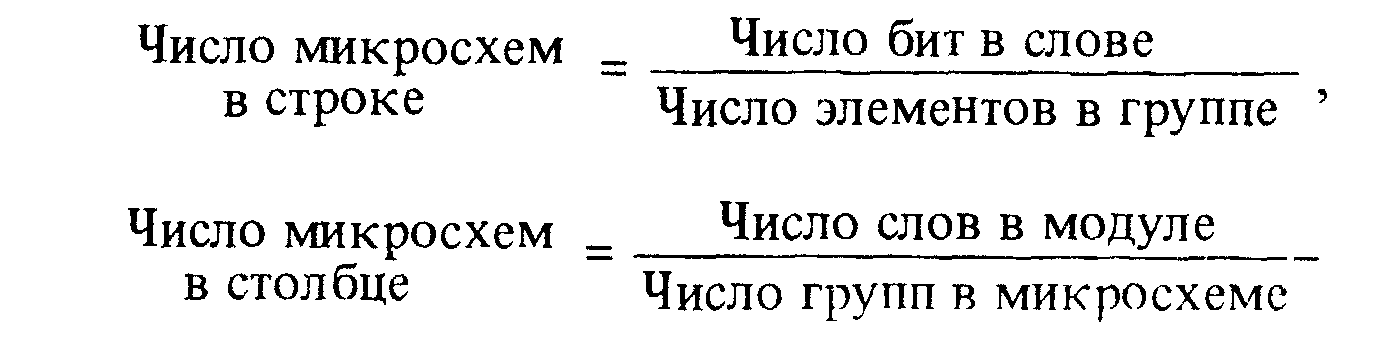

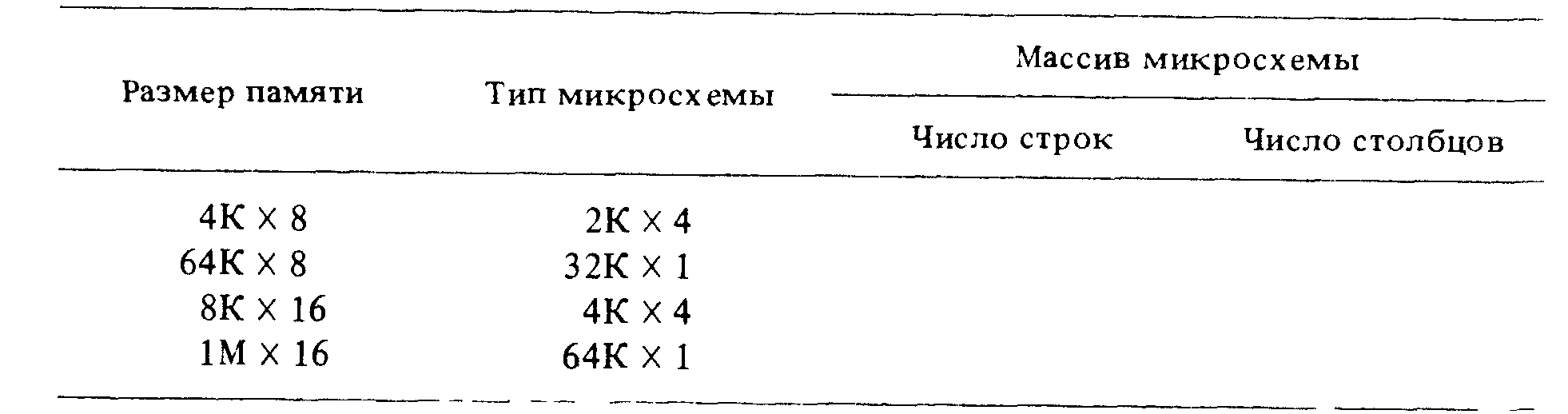

число микросхем в каждой строке, в каждом столбце и во всем t модуле Повторите упражнение для микросхем с - организацией 16К Х 1

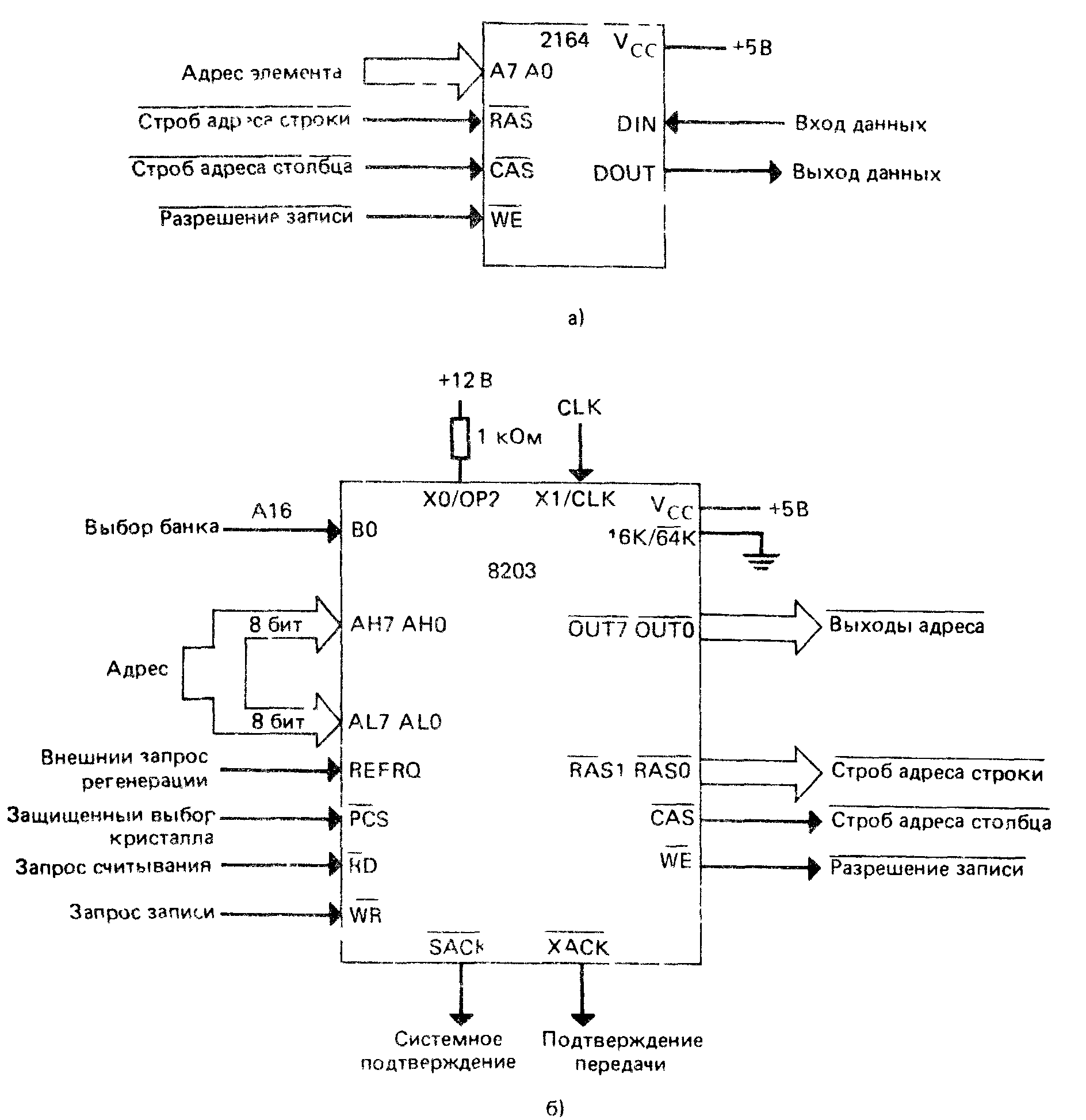

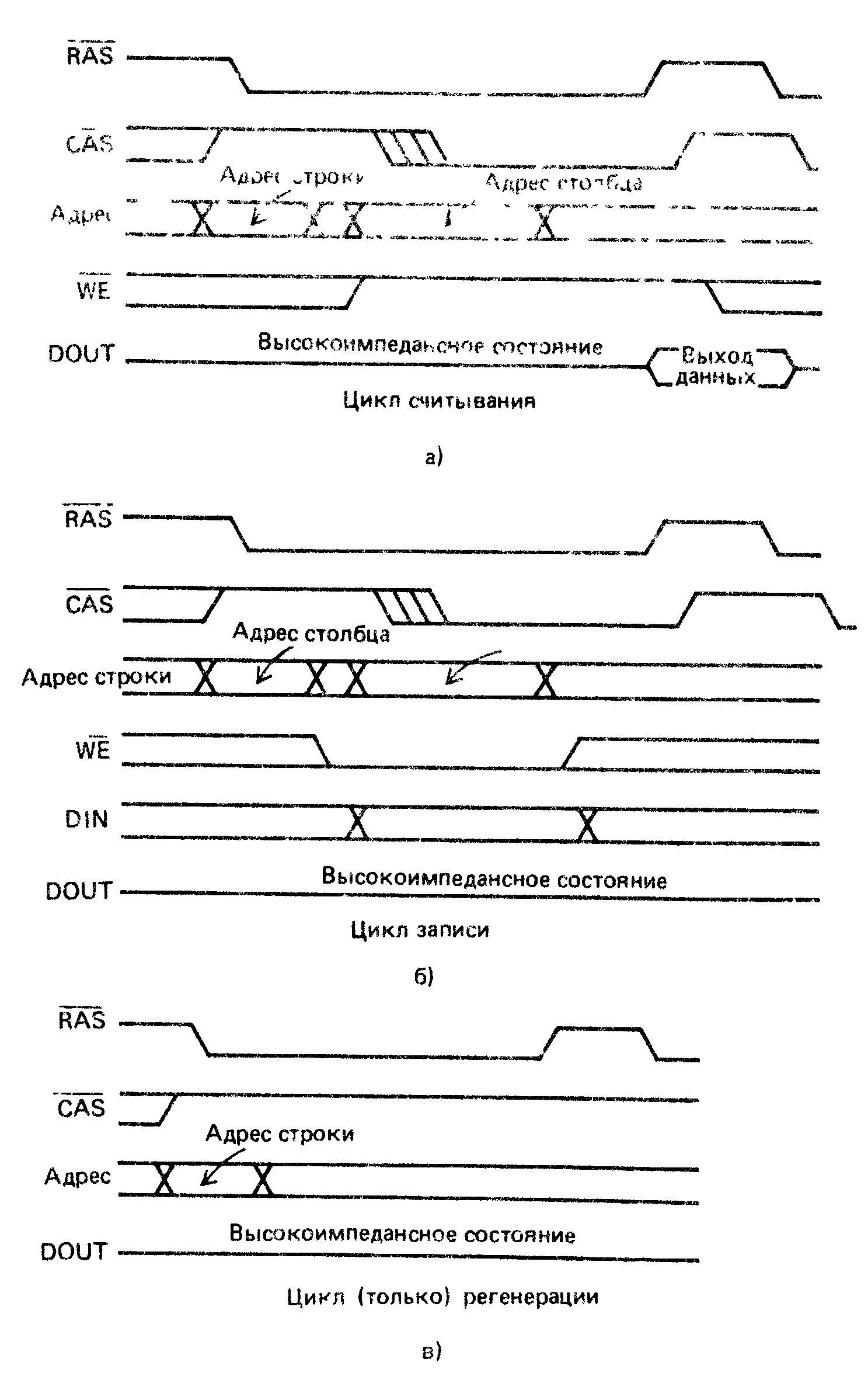

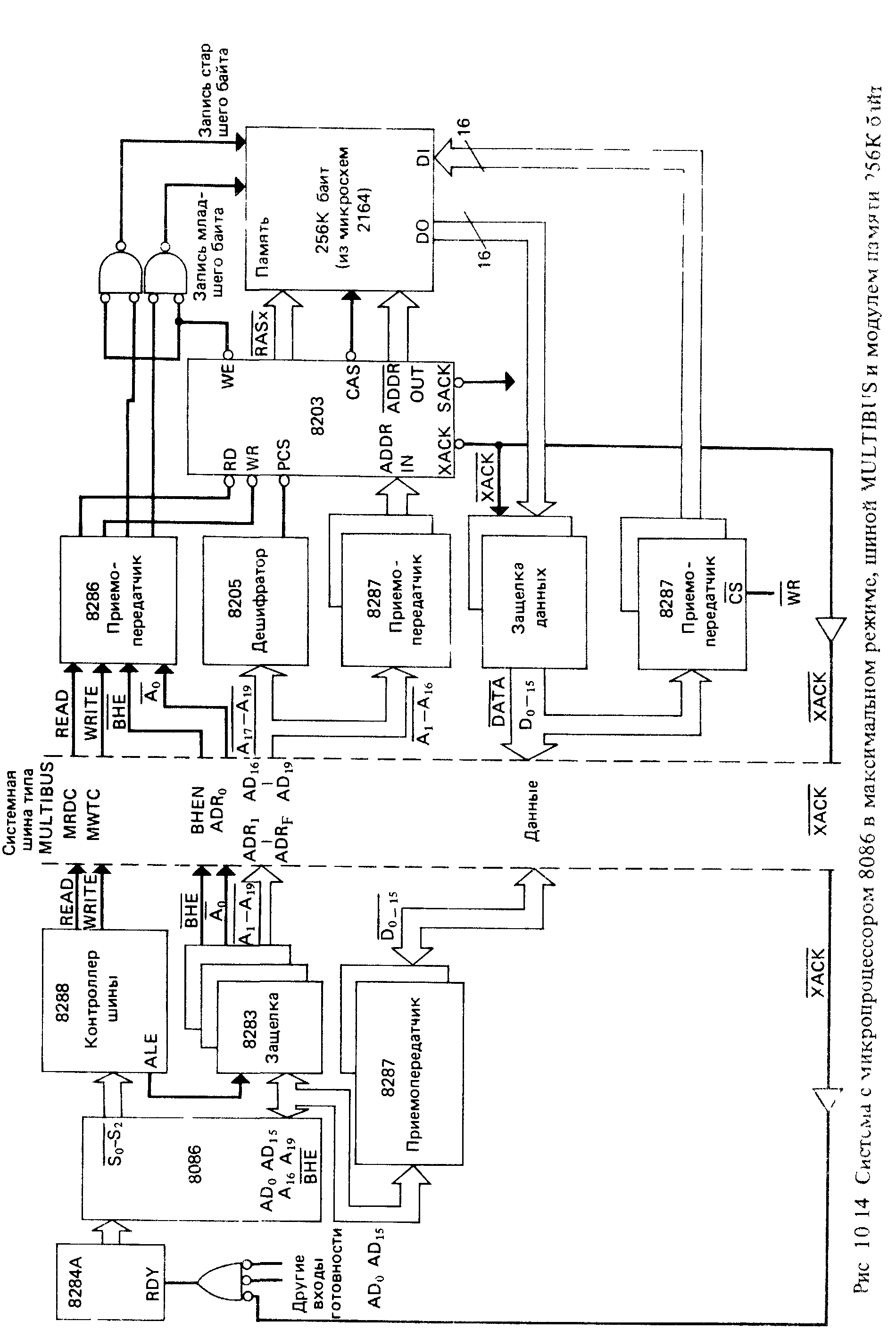

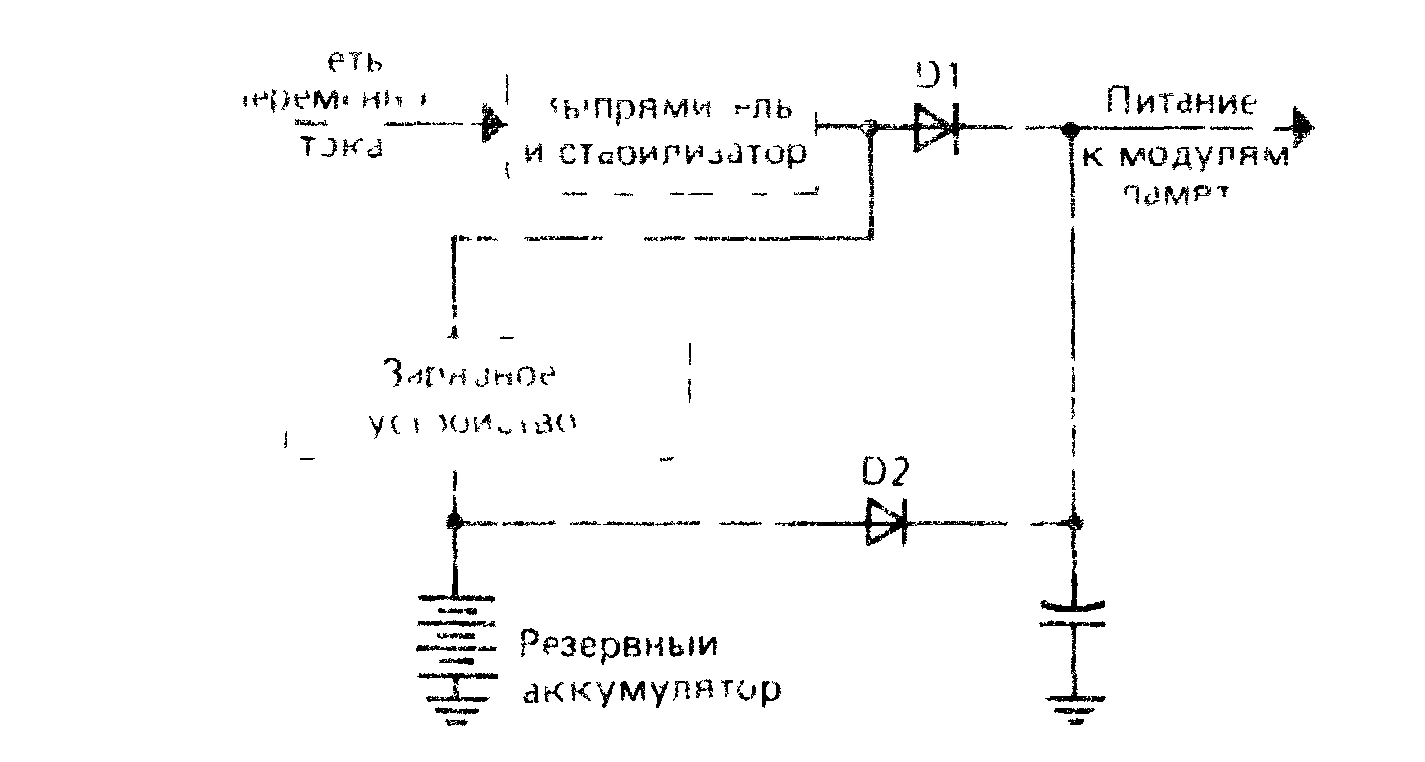

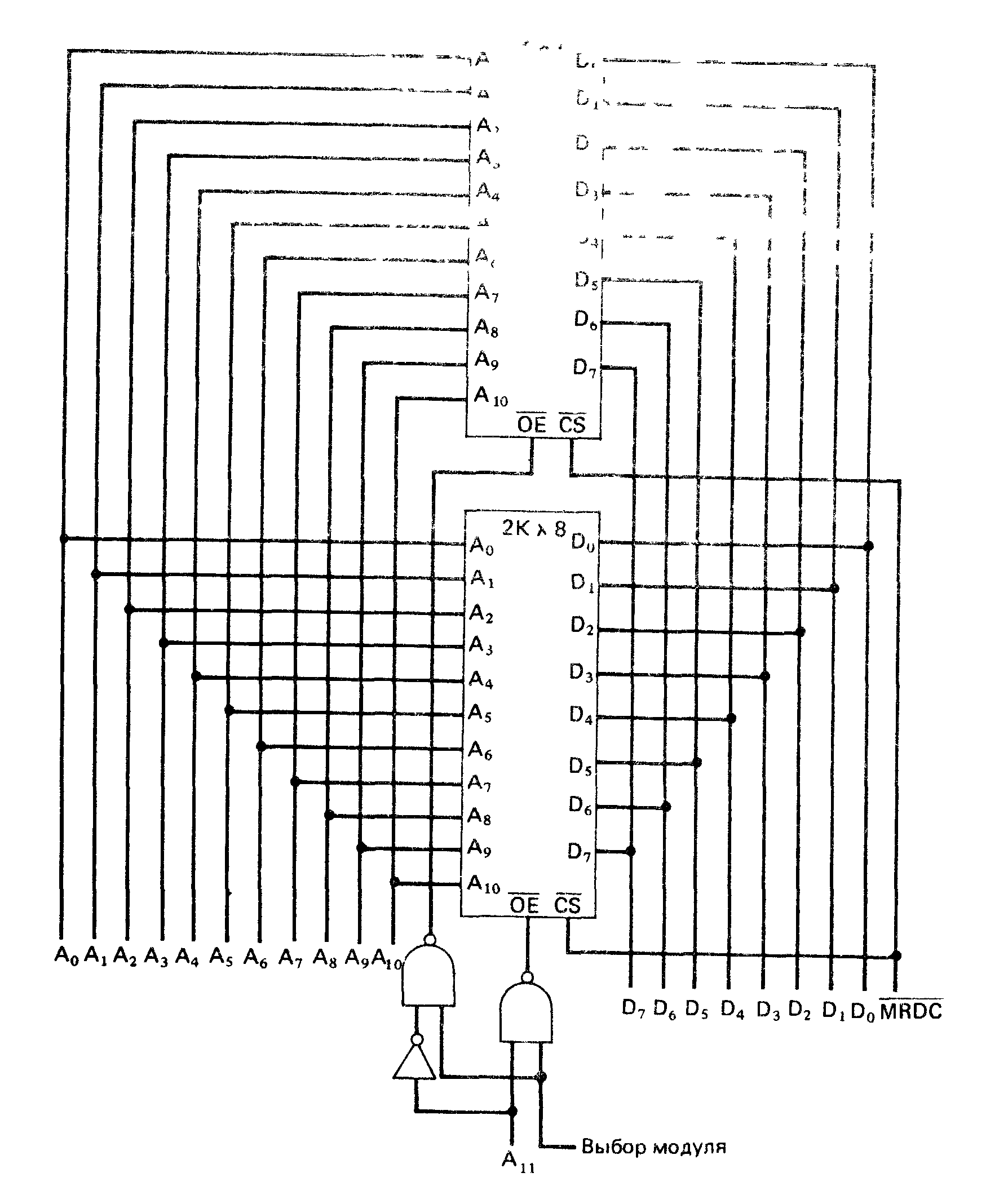

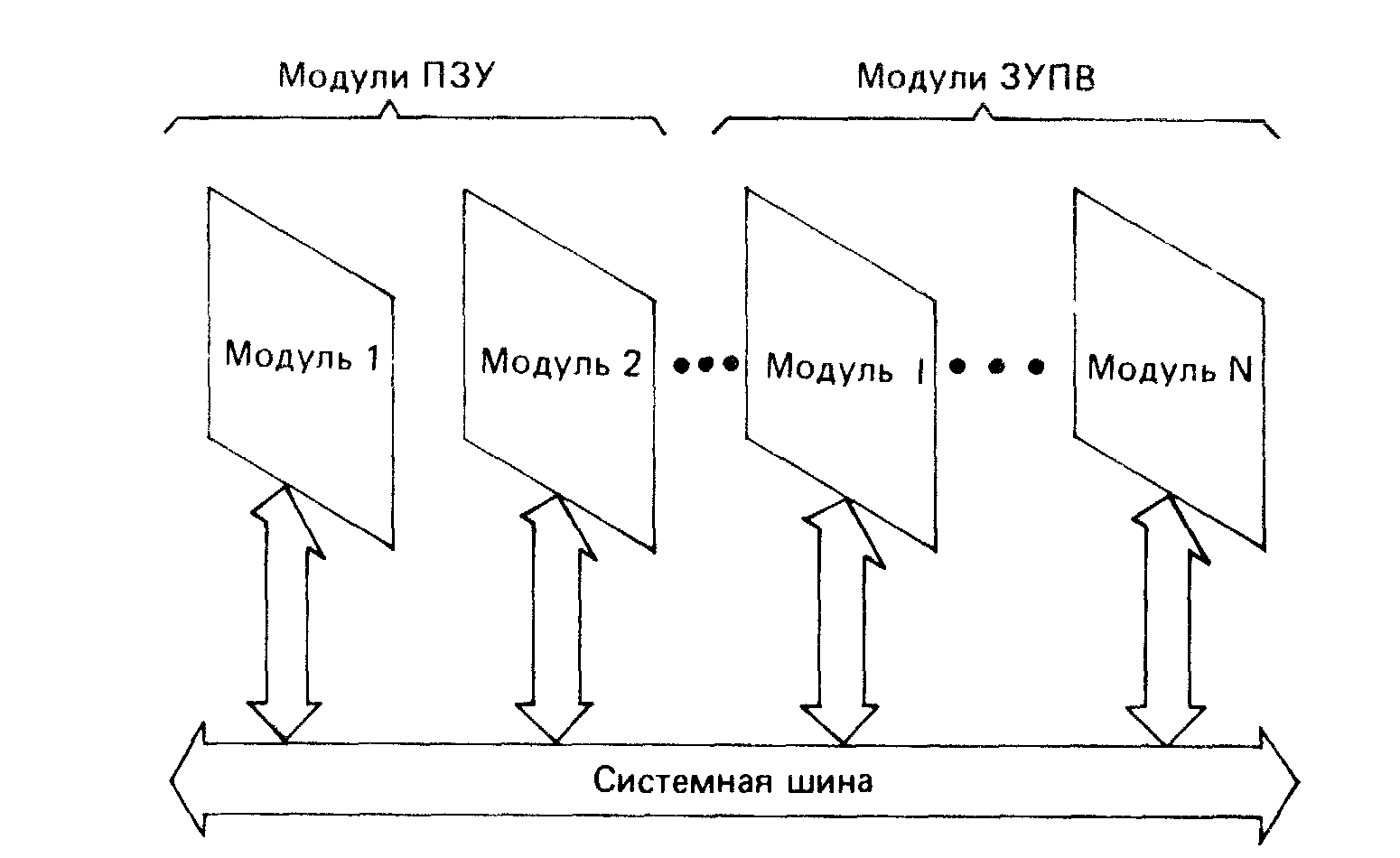

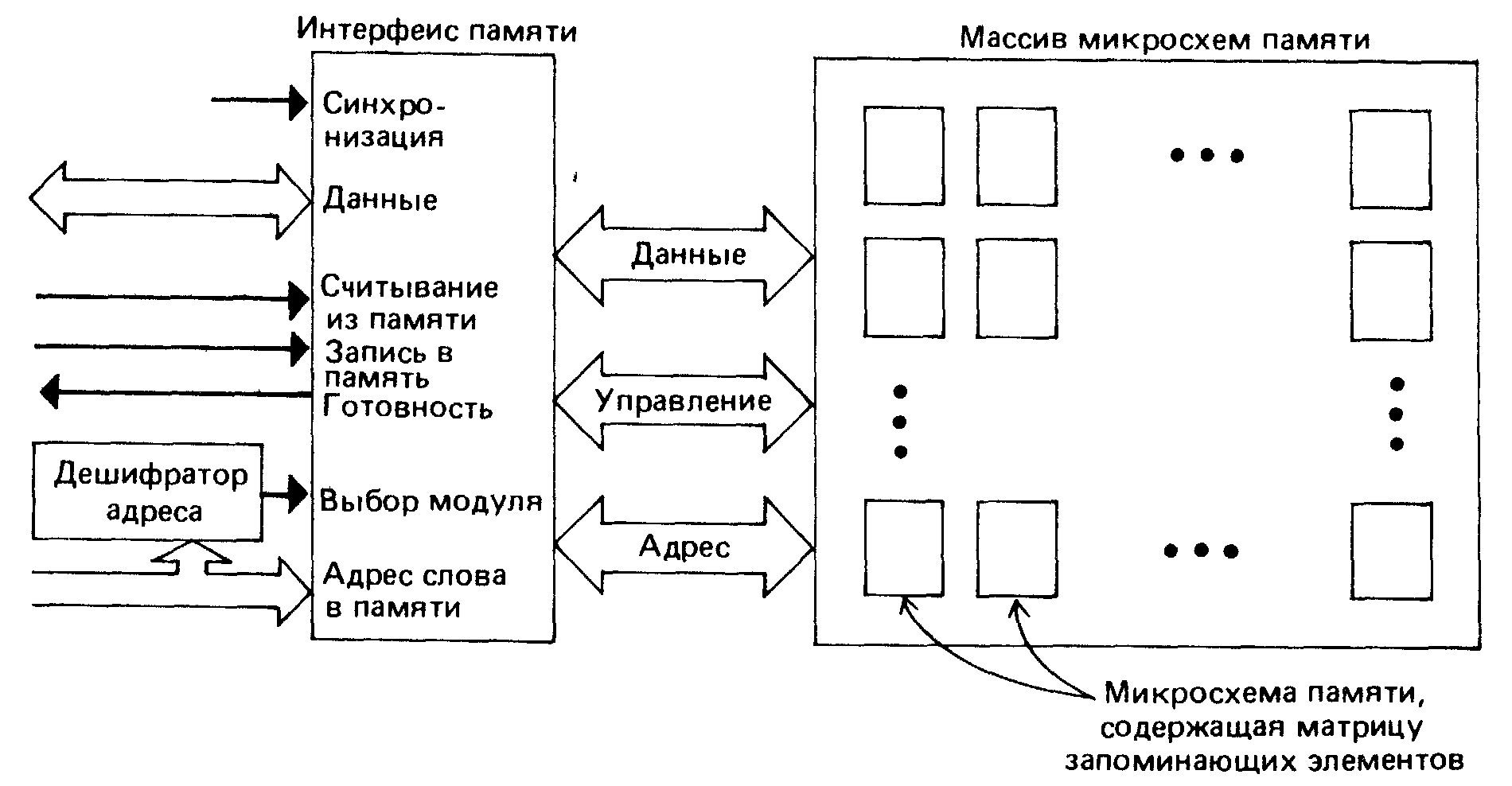

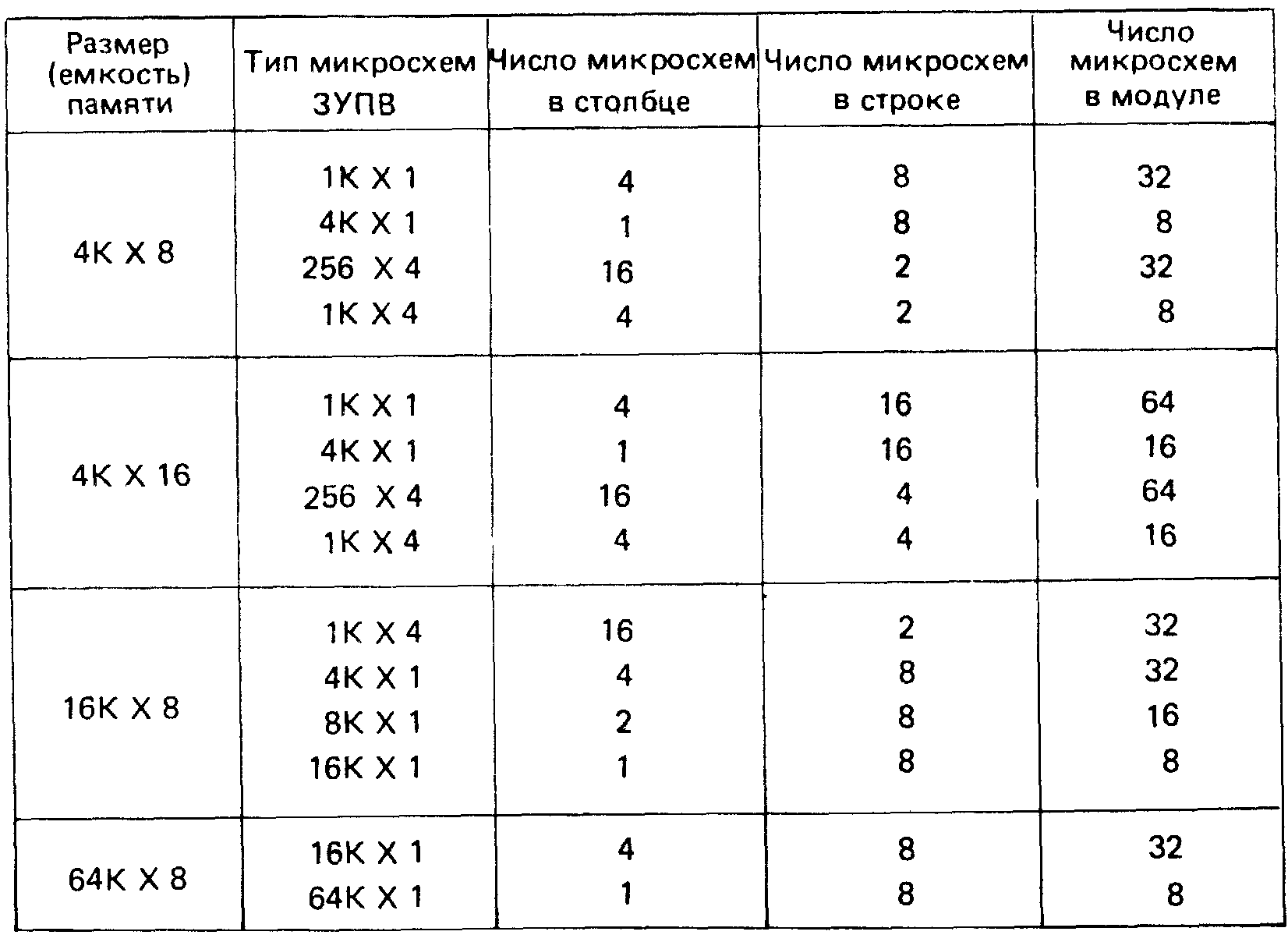

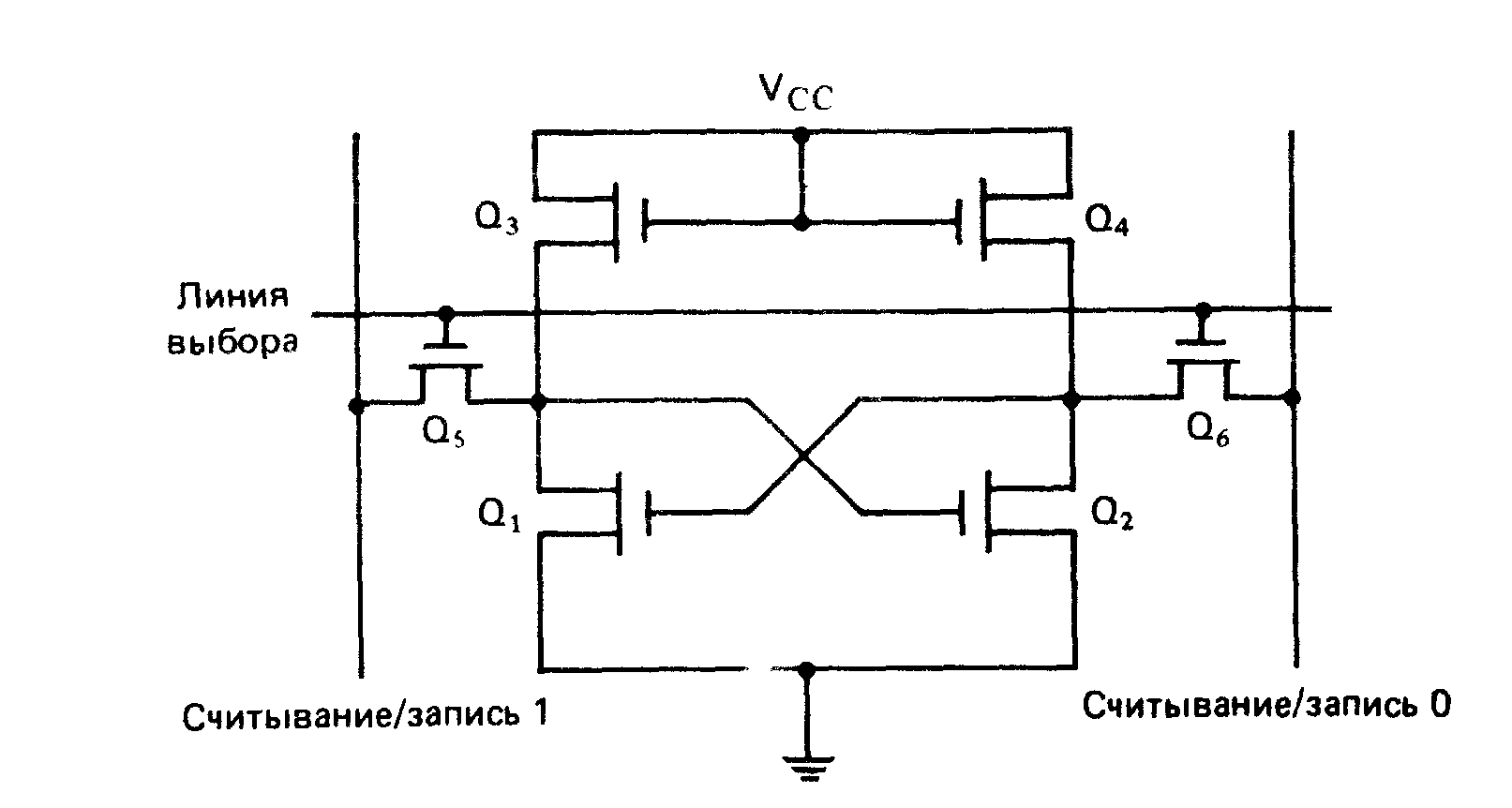

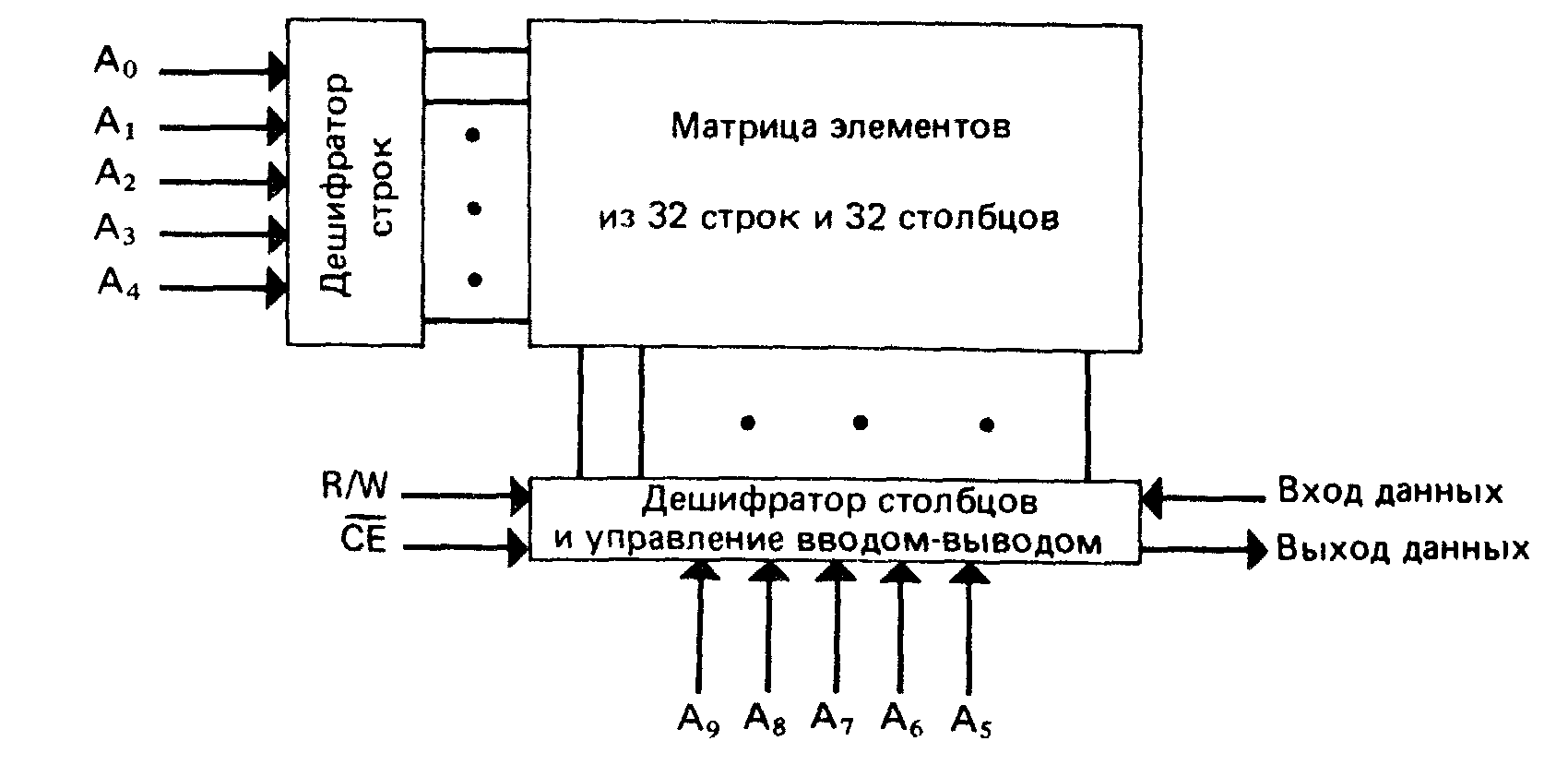

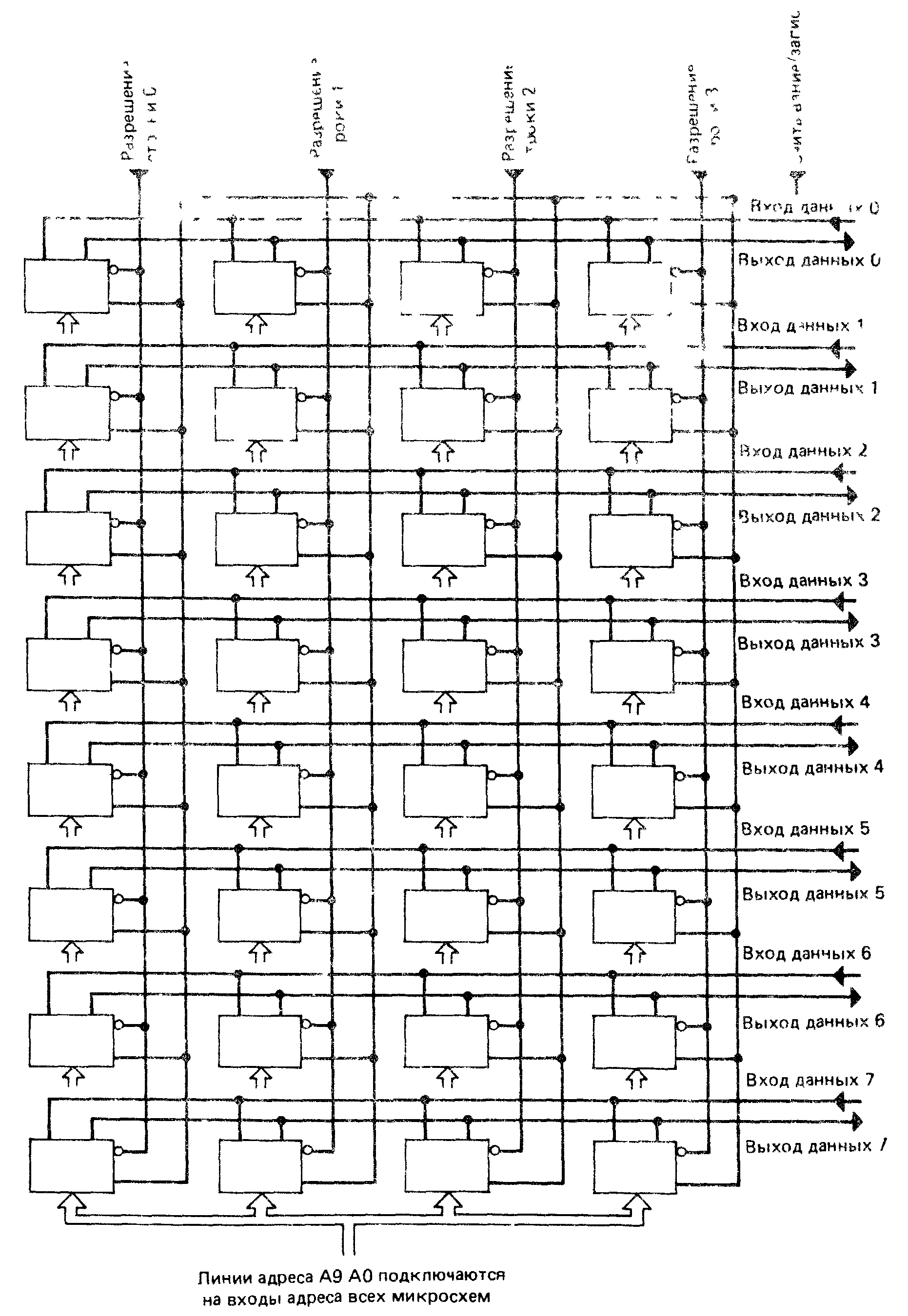

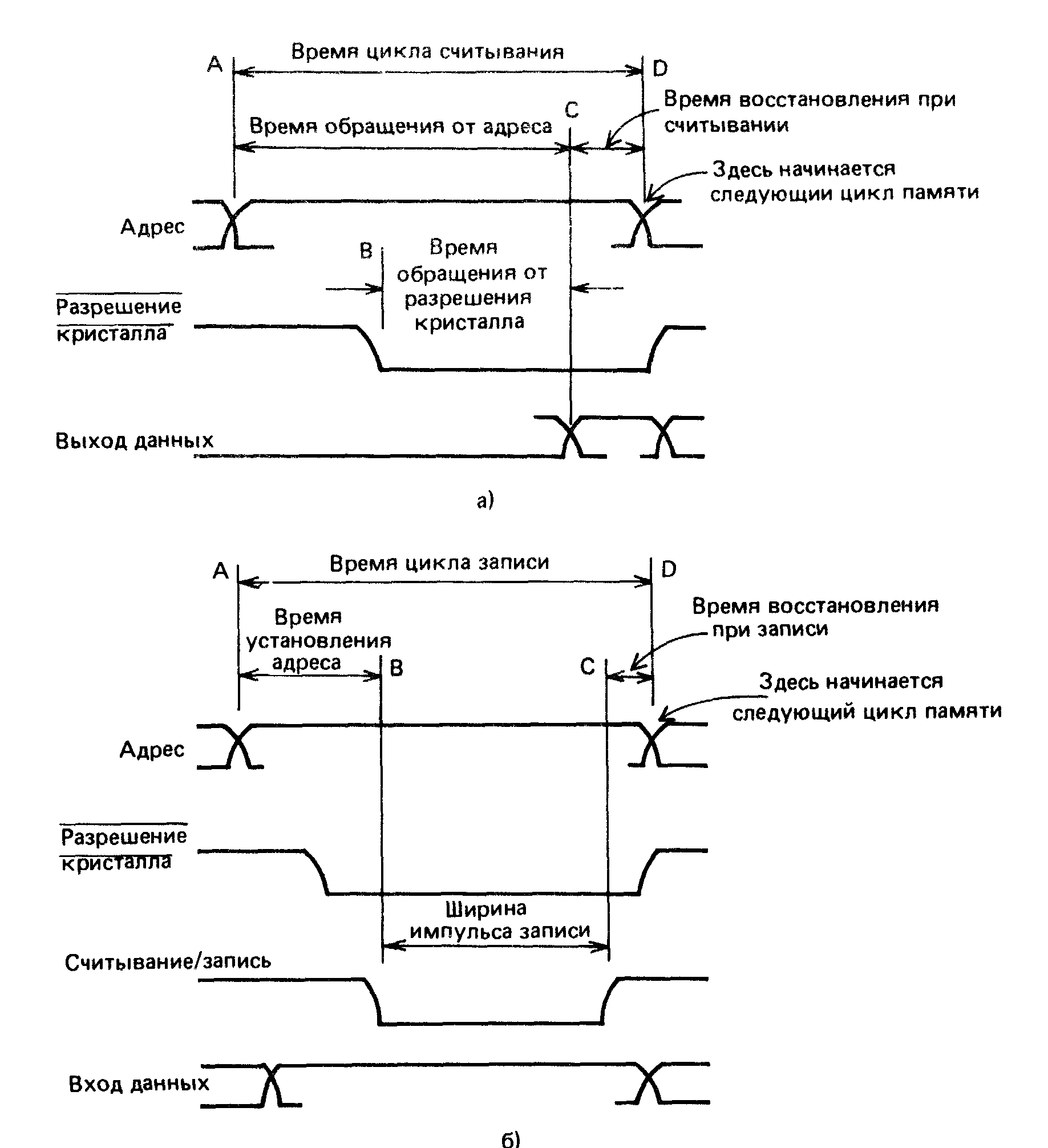

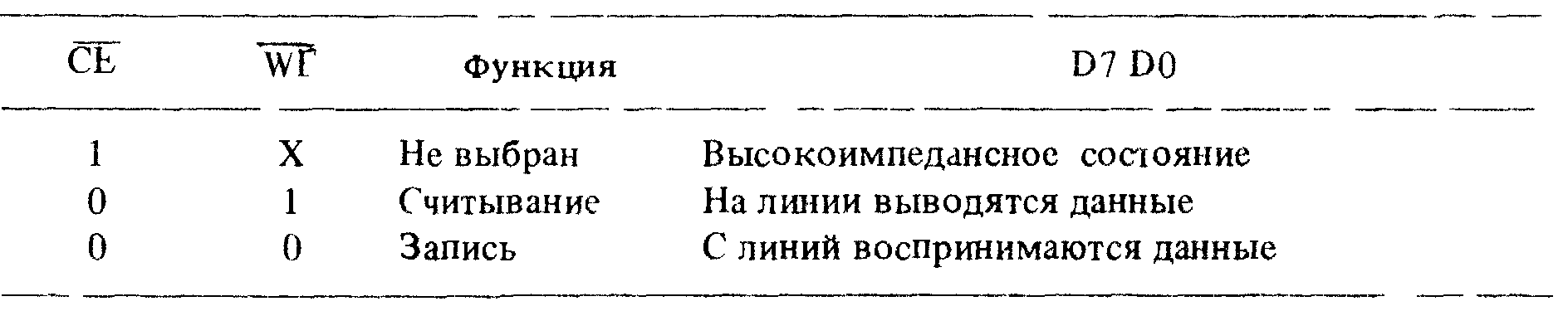

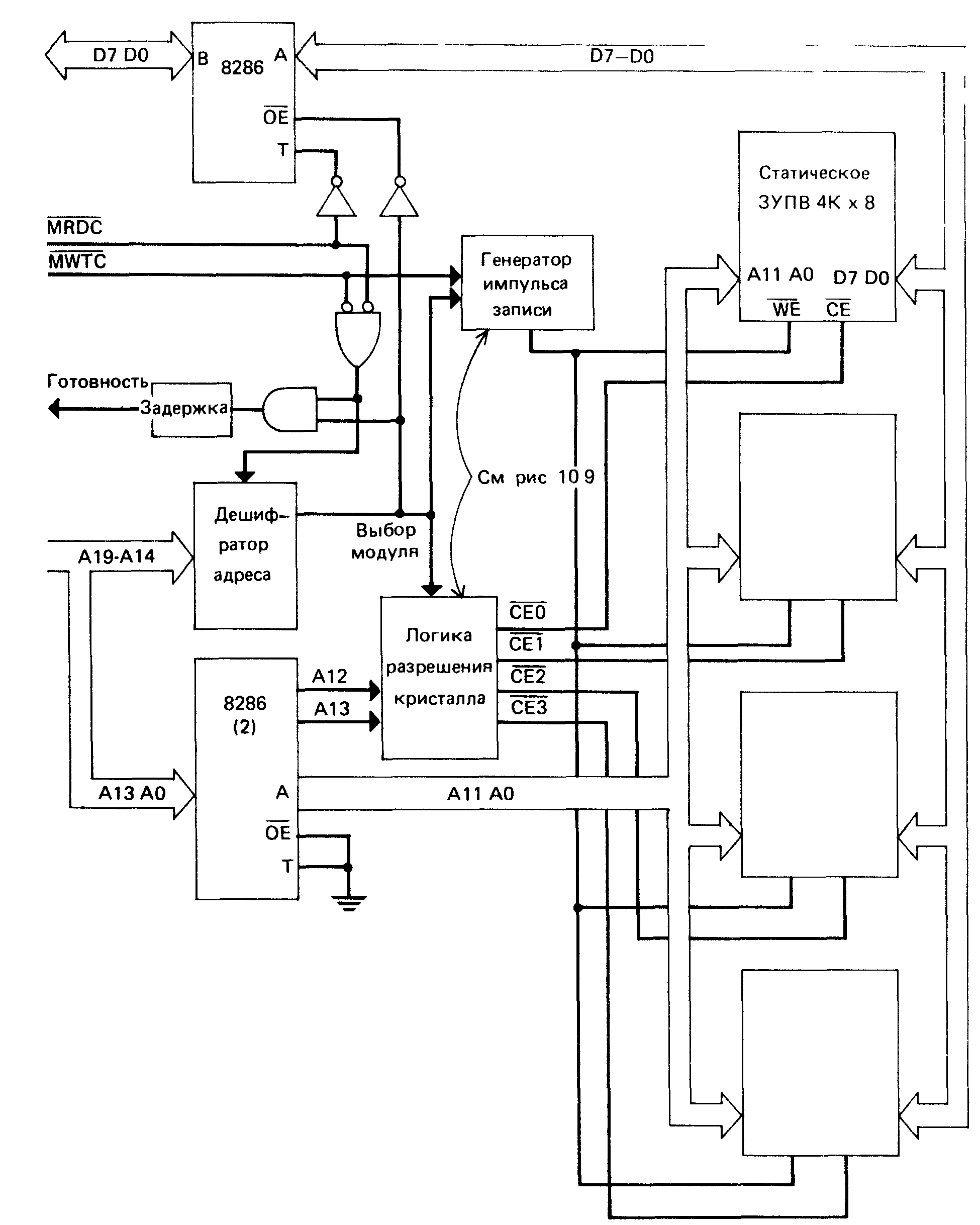

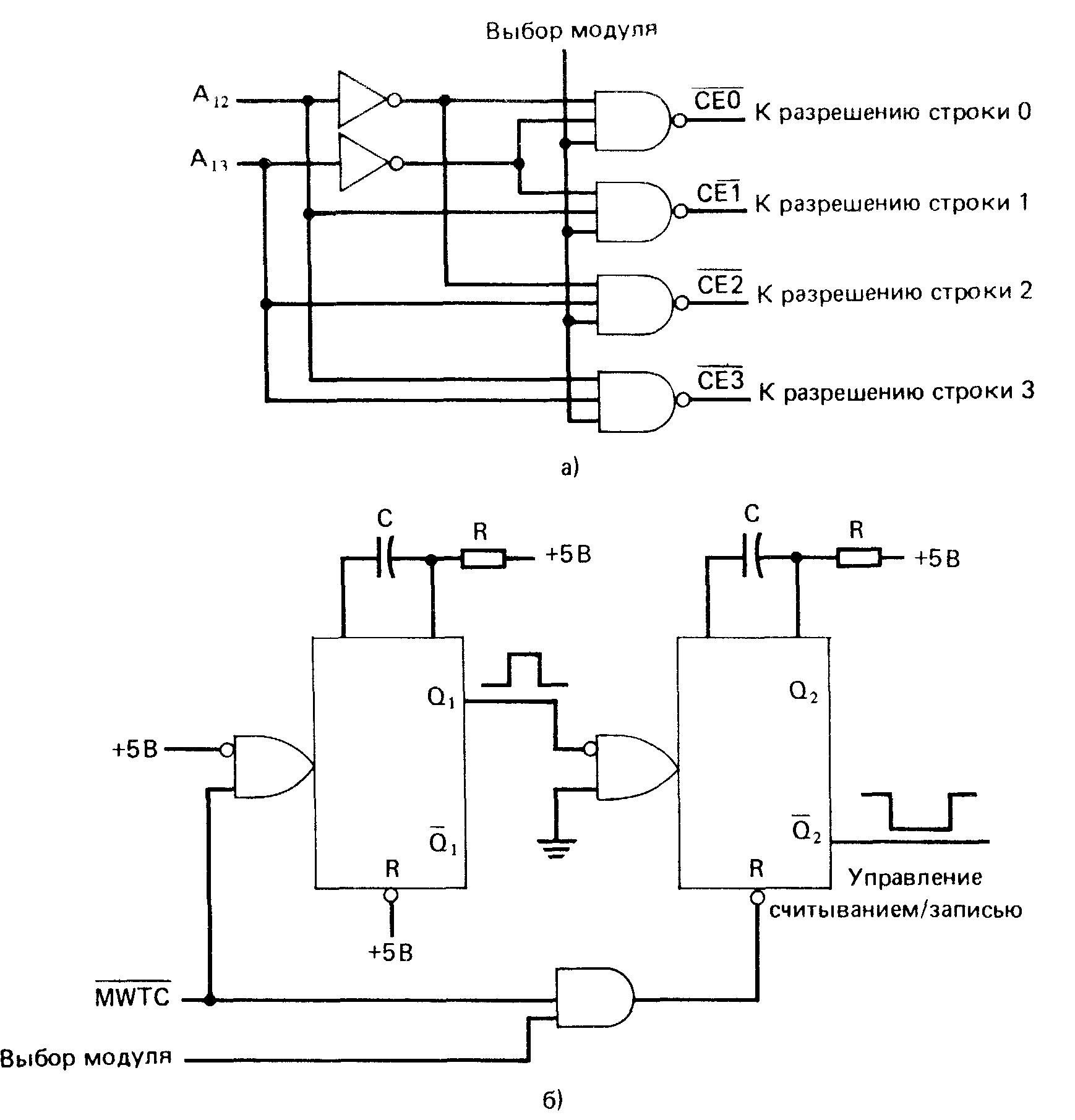

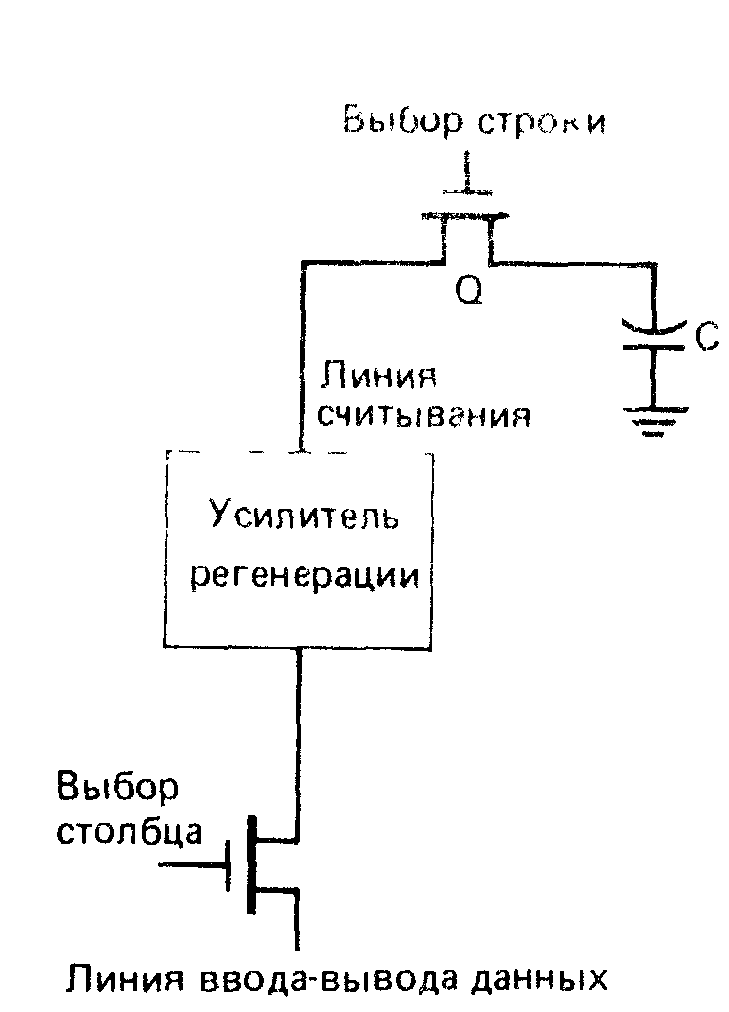

маскируемые.§ 10.5 касается разнообразных видов ПЗУ. 10.1. ОБЩАЯ ОРГАНИЗАЦИЯ ПАМЯТИ Память вычислительной системы обычно состоит из одной или нескольких печатных плат, которые подключены к системной шине. На каждой плате находится модуль, адресуемый старшими битами шины адреса. Как показано на рис. 10. J, в большинстве систем имеются модули ПЗУ и ЗУПВ. Однако следует указать, что в малых системах типа контроллеров могут быть только ПЗУ, а сама память находится на той же печатной плате (и даже в одной и той же микросхеме), что и процессор.  Рис 101 Общая организация памяти  Рис 102 Типичный модуль памяти Общий вид модуля памяти представлен на рис 102 В его состав входят интерфейс и набор микросхем памяти, каждая из которых содержит массив запоминающих элементов; запоминающий элемент может хранить 1 бит К элементам в микросхеме можно обращаться отдельно или группами, но в любом случае соблюдаются следующие отношения  I оворт чго микросхема памяти имеет организацию М х Л", если она содержит М групп из N элементов, а модуль имеет организацию К х L, если он содержит К слов длиной / бит каждое Для иллюстрации введенных определении на рис 10 3 приведены несколько модулей, реализованных на основе типичных микросхем памяти Важнейшими критериями при проектировании памяти являются сгои мость емко^гь быстродействие потребление энергии, надежность, энергояе-зависимость и возможности доступа Стоимость модуля обычно складывается из двух компонент, одна из которых не зависит oi размера модуля и называется накладными расходами, а вторая пропорциональна размеру и называется инкрементнои стоимостью Накладные расходы в основном связаны с электроникой обрамления, а ин-кременгная стоимость соотносится со стоимостью микросхем Обе компоненты зависят от числа контактных соединений и сложности печатной платы Следовательно, микросхемы с большей емкостью требуют меньше служебных приборов и обеспечивают выигрыш в стоимости Так как накладные расходы почти не зависят от емкости модуля, но должны учитываться в каждом модуле, предпочтительнее реализовать память заданной емкости, используя минимум модулей Еще одним фактором, учитываемым в накладных расходах, является стоимость блока питания Чем меньше число напряжений питания, тем менее сложной становится разработка блока питания и платы Быстродействие памяти характеризуется временем обращения (или доступа) , которое определяется как временной интервал от момента поступления  Рис 103 Типичные массивы микросхем памяти стабильных оиналов адреса до получения рыходчык даннь \ Время oupduc ния зависит от mhoihx факторов и даже связано ^ емконют микросхемы Для быстродействующих транзисторов приходиия отводил» большую площадь кристалла, что уменьшает чисто запоминающих элеманюв Кроме тою, быстродействующие микросхемы, коюрьк '•>lпьч ^роизвот.я^я iu бип» лярнои технологии, оказываются боле< дорогими v nq юемкими Потребляемая энергия очень •ражш для уИ^гем когорые ин^Да дол/к ч. работать oi аккумуляторов или ^олрс ти\ элементов (например, и космь ческих объектах). Определяющим фактором для потребляемой каждым Jd" поминающим элементом энергии явпяется применяемая технология. Наиболее часто память с минимальным потреблением энергии производится по КМОП-технологии. Основной ее недостаток связан с увеличением тощади кристалла для каждого запоминающего элемента, что уменьшает емкое! ь микросхемы. К сожалению, потребляемая энергия и быс1ро действие связаны пропорциональной зависимостью, поэтому оптимизировагь оба п-и показателя сложно и дорого. Сейчас наиболее хороший компромисс между быстродействием, потреблением энергии и емкостью обеспечивает высококачественная МОП-технология Поскольку надежность микросхем после их тщательною контроля довольно высока, надежность модуля сильно зависит от числа паяных соединений и сложности платы. Следовательно, при уменьшении общего числа контактов надежность модуля увеличивается, что дополнительно стимулирует минимизацию числа микросхем в модуле. Энергонезависимость и возможности доступа во многом определяются условиями применения. Если применение не требует энергонезависимости, нет никаких причин обеспечивать ее. Когда же требуется энергонезависимое ЗУПВ, приходится использовать ферритовую память, а для полупроводниковой памяти вводить резервное питание По возможности следует как можно шире применять ПЗУ как наименее дорогие, энергонезависимые, надежные и помехоустойчивые устройства, обладающие высокой плотностью упаковки 10.2. СТАТИЧЕСКИЕ ЗУПВ Основной запоминающий элемент на шести МОП-транзисторах, применяемый в статической памяти, показан на рис 104 Хранимая информация определяется состояниями транзисторов Qi и Qs В этой транзисторной паре с перекрестными связями один из транзисторов включен, а другой выключен. Состояние, когда Qa включен, a Q, выключен, представляет собой 1, а противоположное состояние - 0. Транзисторы Оз и Q4 выполняют функции резисторов, а транзисторы Qs и Q ь действуют как разрешающие вентили В операции записи сначала производится выбор элемента посредством установки высокого уровня на линии выбора. При этом ipr чисторы Qs и Qe действуют как короткозамкнутые цепи, поэтому линия считывания/записи 1 подключается к затвору Qs, а линия считывания/записи О—к затвору Qi Для записи в элемент 1 на линии считывания/записи 1 устанавливается 1, а на линии считывания/ записи О—О; это приводит к включению Qs и выключению  Рис. 104 Схема б-транзисторного запоминающего элемента статического ЗУПВ Qi. Если же в элемент необходимо записать 0, на линиях считывания/записи . действуют противоположные сигналы. В любом случае установленные состояния Qi и Оз не изменяются до следующей операции записи. Считывание из элемента производится просто подачей напряжения на линию выбора. При этом состояние Qi передается на линию считывания/записи 0, а состояние 03 — на линию считывания/записи 1. Число запоминающих элементов и их организация в статической памяти варьируются в широких пределах. Диапазон размеров составляет от 256 х 4 до 16К х 1. ЗУПВ 254 х 4 состоит из 256 ячеек, каждая из которых имеет 4 бита, а ЗУПВ 16К х 1 обеспечивает 16К ячеек, каждая из которых содержит всего 1 бит Общая организация статического ЗУПВ 1К х 1 представлена на рис. 10.5. Запоминающие элементы организованы в матрицу из 32 строк и 32 столбцов. Биты адреса А9-АО разделены на адреса строк и столбцов, определяя одну из 1024 ячеек. Входы адреса строки А4-АО дешифрируются и выбирают одну из 32 строк запоминающих элементов. Входы адреса столб-  Рис 10 5 Структура микросхемы памяти с организацией 1К X 1 ца V' ^V че 7 )^-v i ti^iipar'i кдин »u ( ^ Cin г н' t'he и »-). ^ччц^яя vii ввода-вывода, сисгочщио из драйверов и усилю елей считывания Эти схемы позволяют вывеет хранимый 5ит в операции етишвщия и и^мслш ш l операции записи Вхо,п R/W (счить^вани^/зашчь) опре,-ц-^яеэ пт операции (высокий уровень при считывании и низкий гри записи) R\o„i p'np^ULHu/-криситша г? предназначен i ^ rt.i^opi с ур»г^твуюиг"м с ^ чг ми; р< <хем ч мо/ук намят На pHt 106 показан модуль памяти 4К >- построенный рз микросхем 1К х 1 Если кристалч разрешен, выполняется операция считывания или записи в соответствии с уровнем сигнала R/W В противном случае сигнал R/W не распознается и выход переводится в высокоимпедансное состояние Это позволяет непосредственно соединять выходы нескольких микросхем, поэтому. применяя в столбцах микросхемы 1К х 1, можно реализовать модули 2К х 8 4К х 8 и т д., причем каждый столбец "вносит" один бит в байт данных Выводимый бш зависит не юлько от сигналов на линиях адреса, но и от то го, на какие микросхемы подается сигнал разрешения кристалла. Каждая строка в массиве подключена к линии разрешения строки, а всеми линиями разрешения кристалла управляют старшие биты адреса (в данном примере — линии All и А10). Когда строка выбрана, каждая микросхема в строке будет вводить или выводить бит в соответствии с сигналами на линиях А9-АО. Если адрес содержит 16 бит, линии А15-А12 выбирают модуль, All и А10 - строку, а А9-АО - биты в микросхемах, образующие адресованный байт Из-за сложности запоминающего элемента плотность упаковки статической памяти меньше, чем динамической памяти Кроме того, статическая память потребляет больше энергии, так как в запоминающем элементе один из транзисторов всегда включен Основное достоинство статической памяти заключается в том, чю ее недужно регенерировать Микросхемы полупроводниковой памяти легко объединять друг с другом, так как они имеют встроенную электронику обрамления Однако временные ограничения входных сигналов довольно критичны, а временные характеристики микросхем варьируются. Для обеспечения правильной работы логика управления на плате памяти должна формировать входы адреса и управляющие сигналы, соответствующие спецификациям применяемых микросхем. Временная диаграмма входов в операции считывания отличается от диаграммы в операции записи Наиболее важным временным параметром при выборе микросхем является время обращения Максимальная временная задержка от вх ща адреса до выхода данных больше задержки между разрешением кристалла и выходом данных, поэтому временем обращения обычно считается первый параметр Время обращения наиболее распространенных МОП-ЗУПВ изменяется от 50 до 500 не В операции считывания после стабилизации выходных данных вход адреса нельзя сразу же снимать, чтобы запустить следующую операцию считывания Это объясняется тем, что перед следующей операцией прибору требуется некоторое время (называемое временем восстановления при с^итыелнии}. что-  Рис 10 6 Модуль 4К Х 8 на микросхемах памяти с организацией 1К Х 1  Рис 107 Временные диаграммы циклов обращения к памяти а — цикл считывания, б — цикл записи бы закончить внутренние действия Сумма времени обращения и времени восстановления при считывании образует время цикла считывания Именно это время необходимо между запуском операции считывания и запуском следующего цикла памяти Время цикла записи можно определить аналогично и оно может отличаться от времени цикла считывания На рис 107, а приве дена временная диаграмма цикла считывания из памяти Адрес подается в точке А, которая является началом цикла считывания, и должен сохраняться стабильным весь цикл Чтобы уменьшить время обращения, вход разрешения кристалла следует подавать до точки В Выходные данные становятся действительными после точки С и сохраняются такими, пока действуют входы адреса v разрешеч} я Kprici.uia На временной iiidi раммс с ютывания вход R^W не показан гю он должен иметь высокий вровень в течение всею ^икла В типичном цикле записи показанном на рис 10 "7, о, кромь входов адрз-са и разрешения кристалла необходимо еще подать отрицате 1ьный имп/льс на линию R^W и запомиыемче инные В кчение всею лого iwio'a lamibie просто сохраняется стабильными О щако подача импульса записи имре^ JBd г<ригиччых временны> параметр! время уианотения alpcca и ширит и^* пульса записи Времч установления адреса jto время, необходимое шя ста билизации адреса, т е временной интервал, который должен пройти до подачи импульса записи На рис 107, б время установления адреса равно времен ном> интервалу между точками А и В Ширина импульса записи определяет продолжительность активною низкого уровня на входе записи Время цикла записи равно временному интервалу между точками 4 и D, оно представляет собой сумму времени установления адреса ширины импульса записи и в ре мени восстановления при записи В некоторых микросхемах допускаются нулевые времена восстановления в обеих операциях Важно отметить, что время обращения и время цикла являются минималь ными временными требованиями для самих микросхем Время обращения и время цикла во всей системе памяти значительно больше из-за задержек, вносимых логикой управления вводом выводом, логикой системной шины и логикой интерфейса памяти На рис 108 представлен модуль статической памяти 16К х 8 для микро процессора 8088 в максимальном режиме Предполагается что входы CL и WE и линии D7-DO статическою ЗУПВ 4К х 8 имеют взаимосвязи, указанные в табл 10 1 Таблица 101 Сигналы в статическом ЗУПВ  Ьсли микросхема не выбрана (т е СЬ =1) она переходит в пассивное состояние, позволяющее работать с пониженным потреблением энергии Шина адреса разделяется на две Ч1сти линии А1Ч-А14 применяются для выбора модуля, а линии А 13 А 12 подаются в логику разрешения кристалла, которая более подробно изображена на рис 10 9, а Она имеет че{ыре выхода СЕО СЕЗ, из которых в любой момент времени может быть активным только один Выход СЕО подключен на вход микросхемы, имеющей младшие 4К ад ресов, и активен, когда А 13 = А12 = 0 Аналогично сигнал СЕ1 активен, когда А13 = 0 и А12 = 1, СЕ2 активен при А13 = 1 и А12 = 0 и СЕЗ активен, когда А13 = А12 = 1 Во всех случаях на линии выбора модуля должен действовать сигнал 1, прежде чем формируется активным сигнал СЕ Сшнал на линии  Рис 10 8 Модуль памяти 16К X 8 для микропроцессора 8088 в максимальном режиме выбора модуля активен только тогда, когда модуль выбран и распознается операция считывания или записи. Линии адреса А11-АО подаются на входы А11-АО всех микросхем памяти В генератор импульса записи, построенный на двух одновибраторах, подаются сигнал MWTC и линия выбора модуля (см рис 109,  Рис 109 Вспомогательная логика для модуля памяти, показанною на рис 108 ,. а — логика разрешения кристалла, б — генератор импульса записи тора подключен на входы разрешения записи WF всех микросхем памяти и вызывает загрузку данных с линий D7-DO в адресованный байт Отметим, что в микросхемах на рис 10 6 имеются отдельные линии входных и выходных данных, а в микросхемах на рис 10 8 линии данных являются двунаправленными Внутри микросхемы необходимы отдельные линии для считывания и записи в запоминающие элементы, но можно разделить двунаправленные сигналы на сигналы считывания и записи в самом устройстве 10.3. ДИНАМИЧЕСКИЕ ЗУПВ Как и в статических ЗУПВ, память в кристаллах динамической памяти организована в матрицу запоминающих элементов Простейший элемент динамического ЗУПВ состоит всего из одного транзистора и одного конденсатора (см рис 1010) Хранение в элементе 1 или 0 определяется наличием или отсутствием заряда на конденсаторе В операции считывания на одной из ли-  Рис. 10.10. Типичный однотранзисторный запоминающий элемент динамического ЗУПВ или выбора строки уоапав^иваекя вис кий уровень посредством дешифрирован} адреса с1роки (младшие биты адреса). Си, над на этой линии включает ключевы транзисторы Q во всех элементах выбра' ной строки. При этом подключенный , каждому столицу усилитель регенерашь воспринимает уровень напряжения на сот ветствующем конденсаторе и интерпретирует его как 0 или 1. Адрес столбца (старшие биты адреса) разрешает один элемент в выбранной строке на выход. Во время этих действий конденсаторы во всей строке разряжаются. Чтобы сохранить информацию, усилители регенерации производят повторную запись в элементы этой же строки Операция записи осуществляется аналотич-но, но в выбранном элементе запоминаются входные данные, а остальные элементы в выбранной строке просто регенерируются. Из-за разряда конденсатора током утечки р-/2-перехода элементы динамической памяти необходимо периодически считывать и восстанавливать -этот процесс называется регенерацией памяти. Скорость разряда увеличивается с повышением температуры и период регенерации составляет 1 . . ... 100 мс. При рабочей температуре +70°С типичное значение его 2 мс. Хотя строка элементов регенерируется в операции считывания или записи, случайность обращений к памяти не может гарантировать, что каждое слово в модуле памяти регенерируется с требуемым периодом 2 мс. Необходима периодическая регенерация памяти с помощью специальных циклов. В цикле регенерации в микросхемы подается адрес строки и выполняется операция считывания, чтобы восстановить выбранную строку запоминающих элементов. Однако этот цикл отличается от обычного цикла считывания следующими моментами: 1. Входной адрес подается в микросхемы не с шины адреса, а от специального двоичного счетчика, называемого счетчиком адреса регенерации. В каждом цикле регенерации производится инкремент этого счетчика и он проходит по всем адресам строк. Адрес столбца в регенерации не участвует, так как все элементы строки восстанавливаются одновременно. 2. В цикле регенерации разрешаются все микросхемы, поэтому она производится одновременно во всех микросхемах модуля памяти. Такой прием сокращает число циклов регенерации. В обычном же цикле считывания разрешена максимум одна строка микросхем. 3. Кроме входа разрешения кристалла динамическое ЗУПВ обычно имее! входной сигнал разрешения выхода данных. Эти два сигнала управления объединяются внутри микросхемы так, что выход данных переводится в высоко-импедансное состояние, если оба эти входа не активны. В цикле регенерации сигнал разрешения выхода данных имеег пассивный уровень. Это необходимо потому, что все микросхемы в одном и том же столбце оказываются выбранными, а их выходы данных соединены друг с другом. Во время обычного цикла считьюания выбрана только одна строка микросхем и сигналы разрешения выхода данных всех строк имеют активный уровень. Рассмотрим модуль памяти емкостью 16К байт, реализованный на динамических ЗУПВ 4К х 1. Массив микросхем имеет 4 строки и 8 столбцов. Каждая микросхема содержит 64 строки и 64 столбца запоминающих элементов и имеет отдельные входы адреса строки (6 бит) и адреса столбца (6 бит). Предполагается, что входы разрешения кристалла и разрешения выхода обо-значеныТЕ h |

ППЗУ программируются бит за битом посредством задания адреса содержащей бит ячейки на входах адреса и подачи тока в выходную линию данных; при этом подаются импульсы по линии питающего напряжения и соог-ветствующих управляющих входов. Значение тока, амплитуда и продолжительность импульсов, а также способ подачи их зависят от типа микросхемы. Обычно циклы программирования чередуются с циклами контроля и продолжительность чередования в два раза больше времени, необходимого для программирования бита.

В отличие от ППЗУ, в которых содержимое программируется раз и навсегда путем "пережигания" диодных связей, содержимое СППЗУ определяется распределением заряда. СППЗУ программируются путем инжекции заряда и после программирования распределение заряда сохраняется до тех пор, пока не будет нарушено каким-либо внешним источником энергии, например ультрафиолетовым светом. Вместо заключения кристалла в светонепроницаемый корпус, как это делается в ос1альных микросхемах, СППЗУ имеют над кристаллом кварцевое окно, через которое проходит внешняя энергия. При экспозиции памяти от внешнего источника энергии в течение нескольких минут (10 ... 50 мин в зависимости от гипа микросхемы) заряды перераспределяются в их естественное состояние, стирая старое содержимое памяти ; После этого СППЗУ можно программировать вновь.

: Как и ППЗУ, СППЗУ обычно применяют на этапе разработки изделия, а в | серийной продукции заменяют маскированными ПЗУ. Благодаря возможности стирания ими можно пользоваться несколько раз Однако в отличие от ; ППЗУ их содержимое может исчезать, поэтому СППЗУ не рекомендуется " встраивать в изделия, рассчитанные на длительную эксплуатацию. Продолжительность сохранения содержимого зависит от условий окружающей среды и варьируется от нескольких месяцев до нескольких лет.

Программируется СППЗУ посредством подачи адреса на адресные входы, ; а также высоких или низких уровней напряжения на все выходы данных;

«после этого на входы питания и управления подаются необходимые импуль-

(сы. Например, при программировании СППЗУ 2764 с организацией 8К х 8 (фирмы Intel) на вход Vpp подается напряжение 21 В, а на вход СЕ низкий Уровень напряжения. Одновременно адрес программируемого байта подает-|ся -на входы А12-АО, а баЙ1 данных на контакты 07-00. Затем байт данных ' записывается в адресуемый &ат подачей импульса напряжения +5 В на вход

PGM. После записи необходимо содержимое каждого oauia проконтролировать.

Микросхемы ППЗУ и СППЗУ, выпускаемые даже одной фирмой, имекл различные спецификации программирования Эти спецификации, особенно для ППЗУ, оказываются довольно сложными и их требуется неукоснитель но соблюдать. Поэтому многие фирмы предлагают специальные приборы, на зываемые программаторами ППЗУ и предназначенные для программирова ния ППЗУ и СППЗУ Чтобы удовлетворить спецификации нескольких типов микросхем, в некоторых программаторах предусмотрены схемные модули, называемые платами персонификации, которые формируют все электрические сигналы для программирования микросхем определенного типа. Кроме плат персонификации, в управляющий модуль программатора обычно встраивается микропроцессор. Управляющий модуль позволяет одним приказом записать блок данных из системы проектирования в ППЗУ или СППЗУ В программаторе имеется также индикатор для контроля содержимого ППЗУ. Для универсального программатора ППЗУ фирмы Intel в операционной системе ISIS-II имеются приказы для выполнения следующих операций

1. Загрузка программируемых данных из выбранного устройства ввода (дисковый файл, перфолента или системная консоль) в память системы проектирования.

2. Индикация или изменение данных в памяти системы проектирования

3. Запись в сегмент ППЗУ данных, которые хранятся в памяти системы проектирования по заданному начальному адресу (т е. собственно программирование) .

4 Передача блока данных из ППЗУ в память, что позволяет просмотреть содержимое ППЗУ с системной консоли или использовать для программирования дублирующей микросхемы.

5. Передача блока данных из ППЗУ в дисковый файл.

6. Сравнение блока данных из ППЗУ с содержимым области памяти (т е контроль программирования).

Электрически изменяемые ППЗУ также допускают репрограммирование и обладают удобным преимуществом возможностью отдельно стирать и ре-программировать каждый байт. К недостатку таких микросхем относится сравнительно высокая стоимость.

Упражнения 1 Заполните следующую таблицу

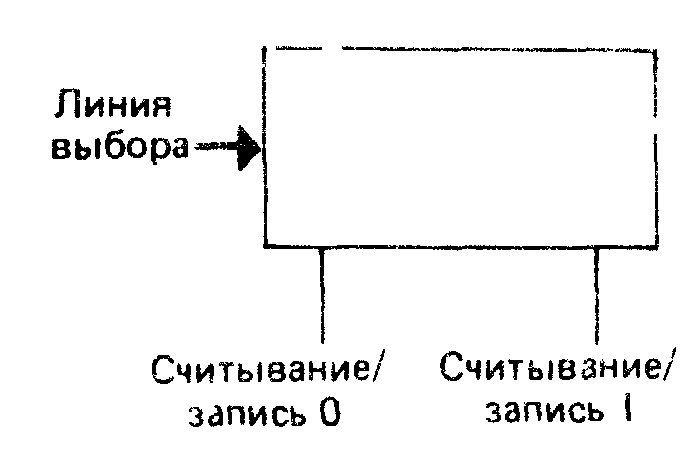

Рис. 10 17 Условное изображение запоминающего элемента

^ 2 Имеется модуль памяти емкостью 32К байт с в контрольными битами парите га, выполненный на

(