Лекции по ВМСС. Конспект лекций по курсу "Электронные вычислительные машины, системы и сети"

Скачать 3.89 Mb. Скачать 3.89 Mb.

|

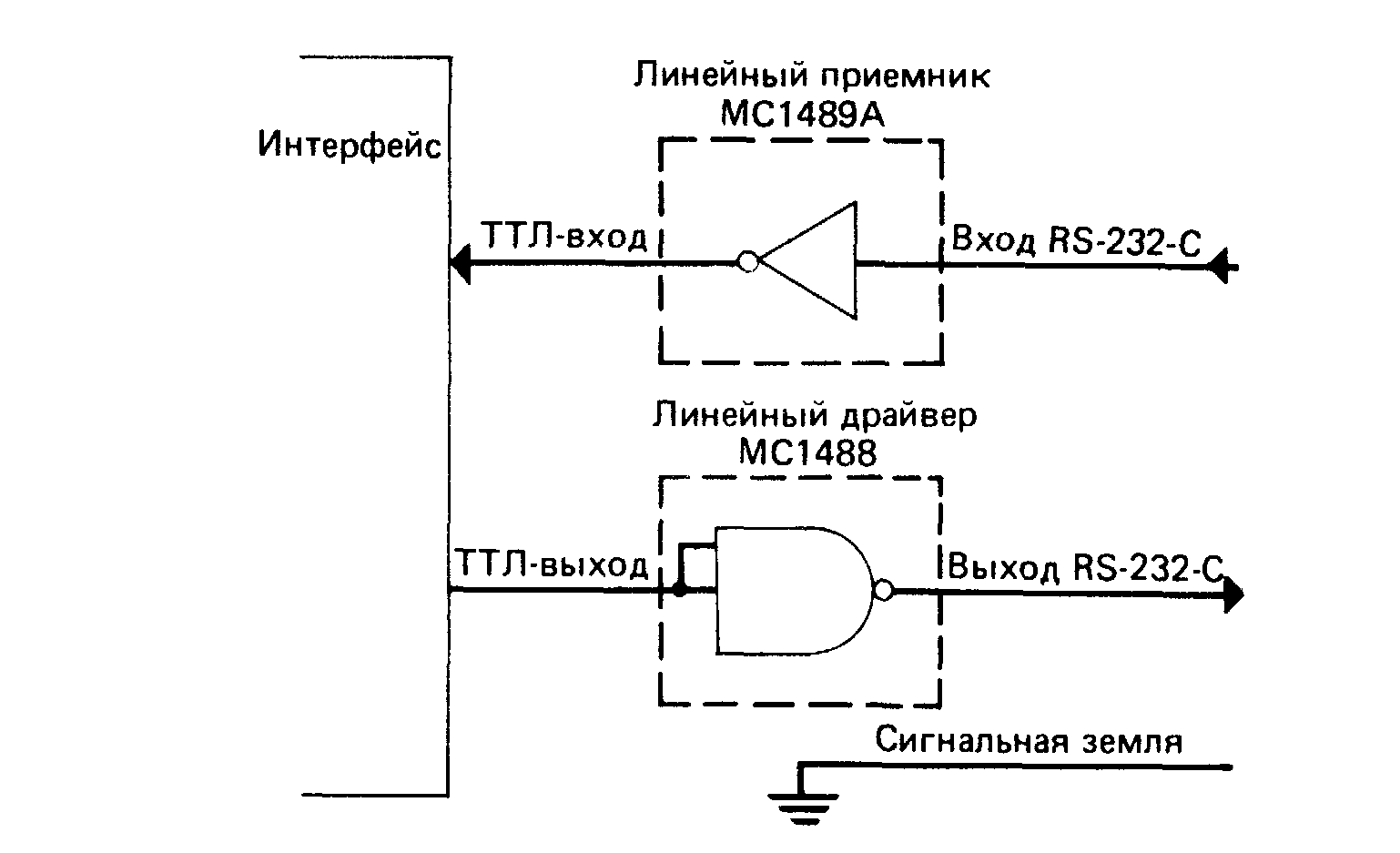

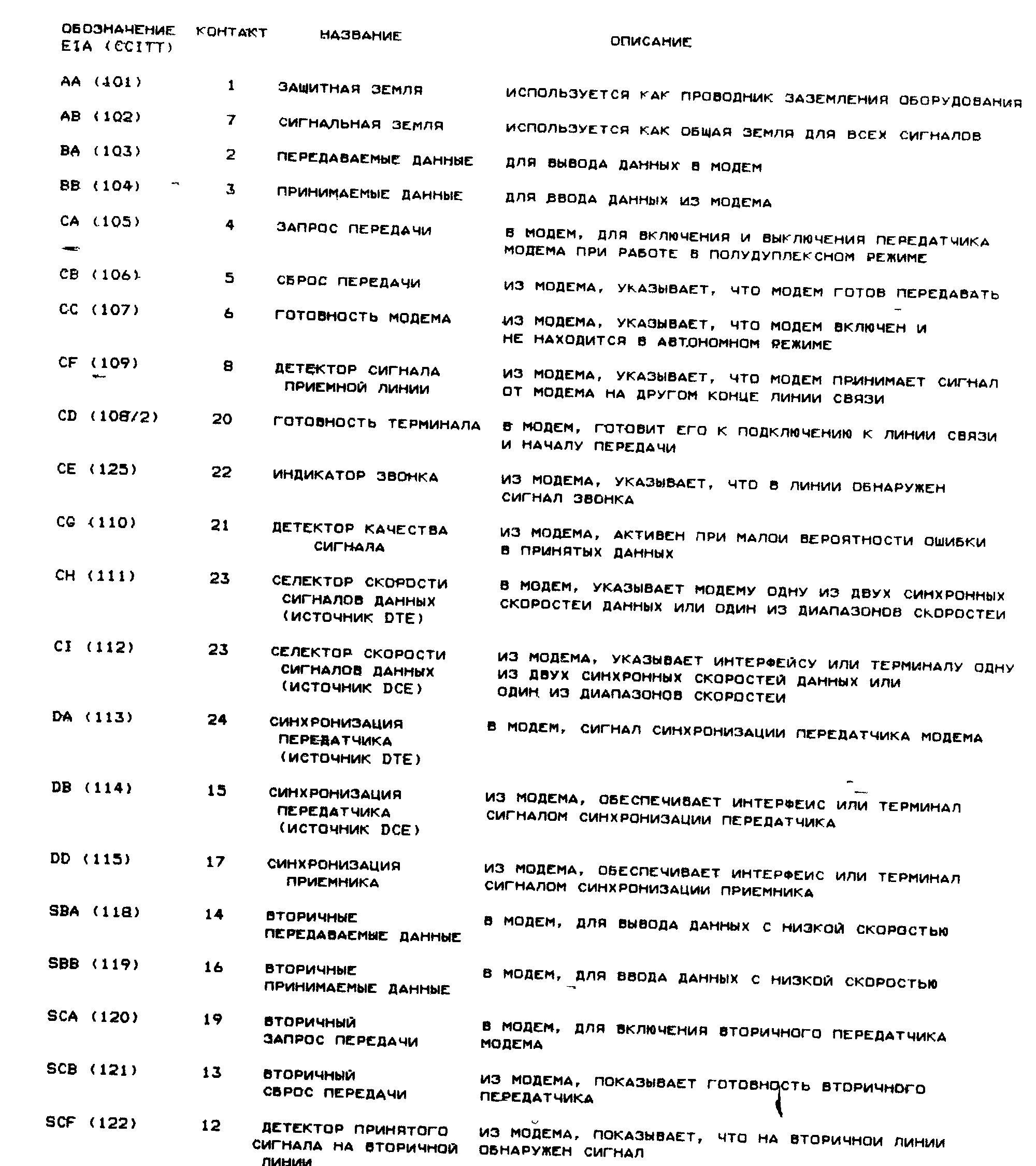

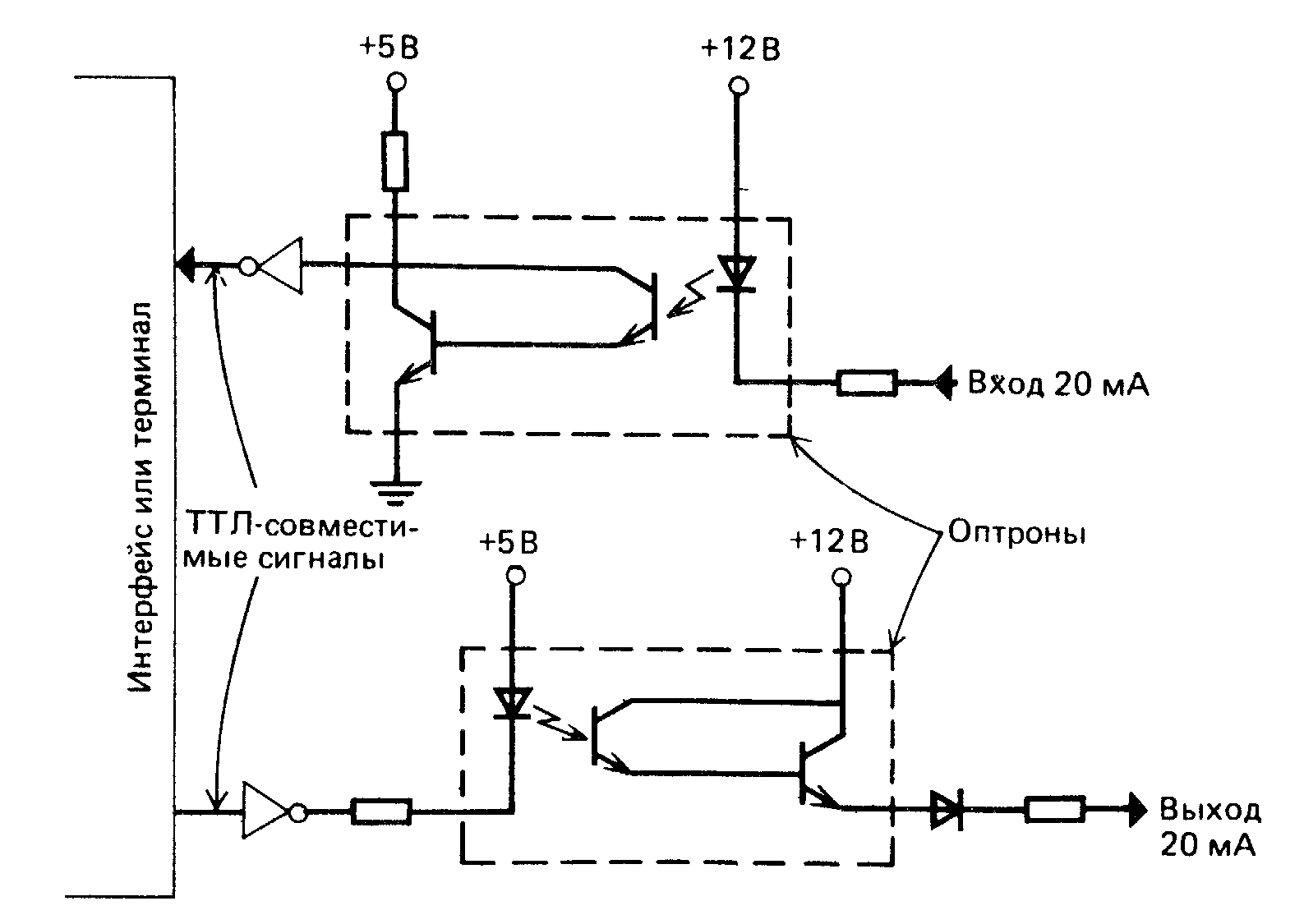

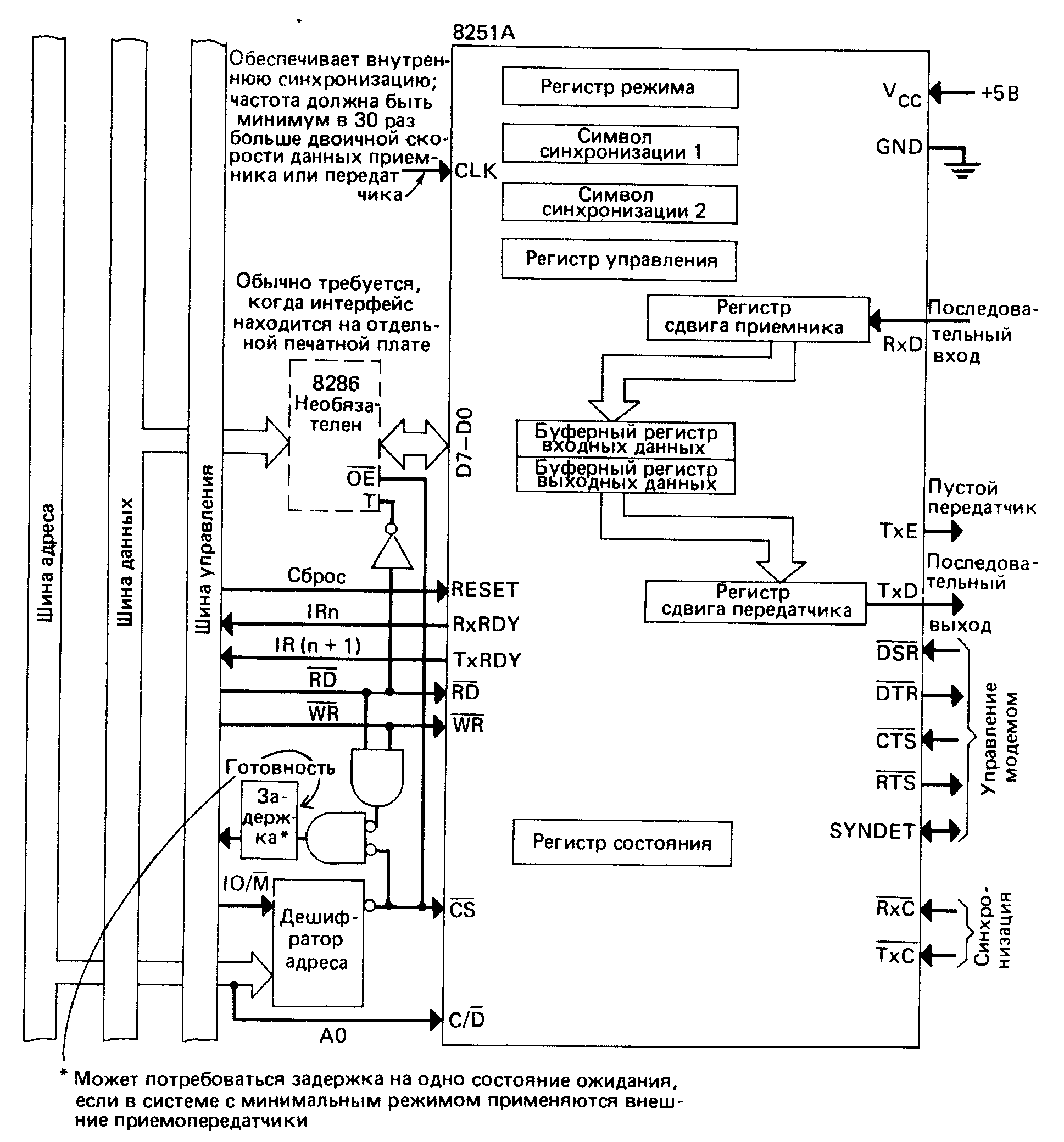

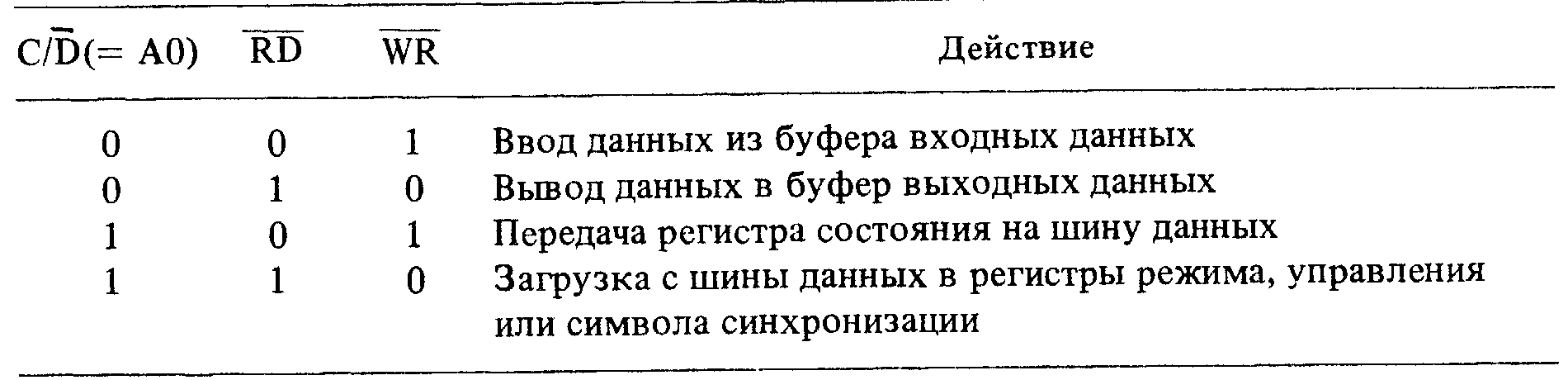

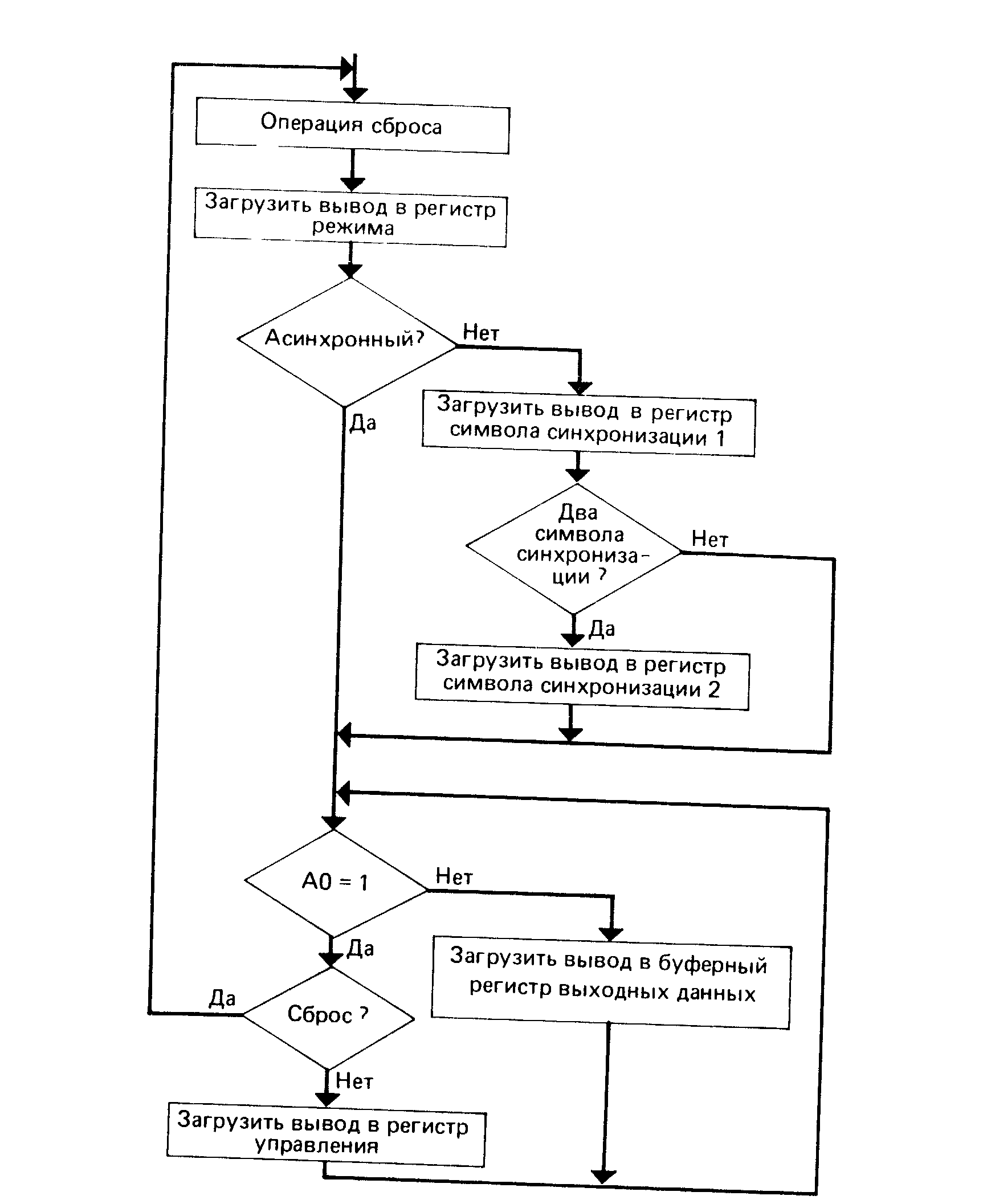

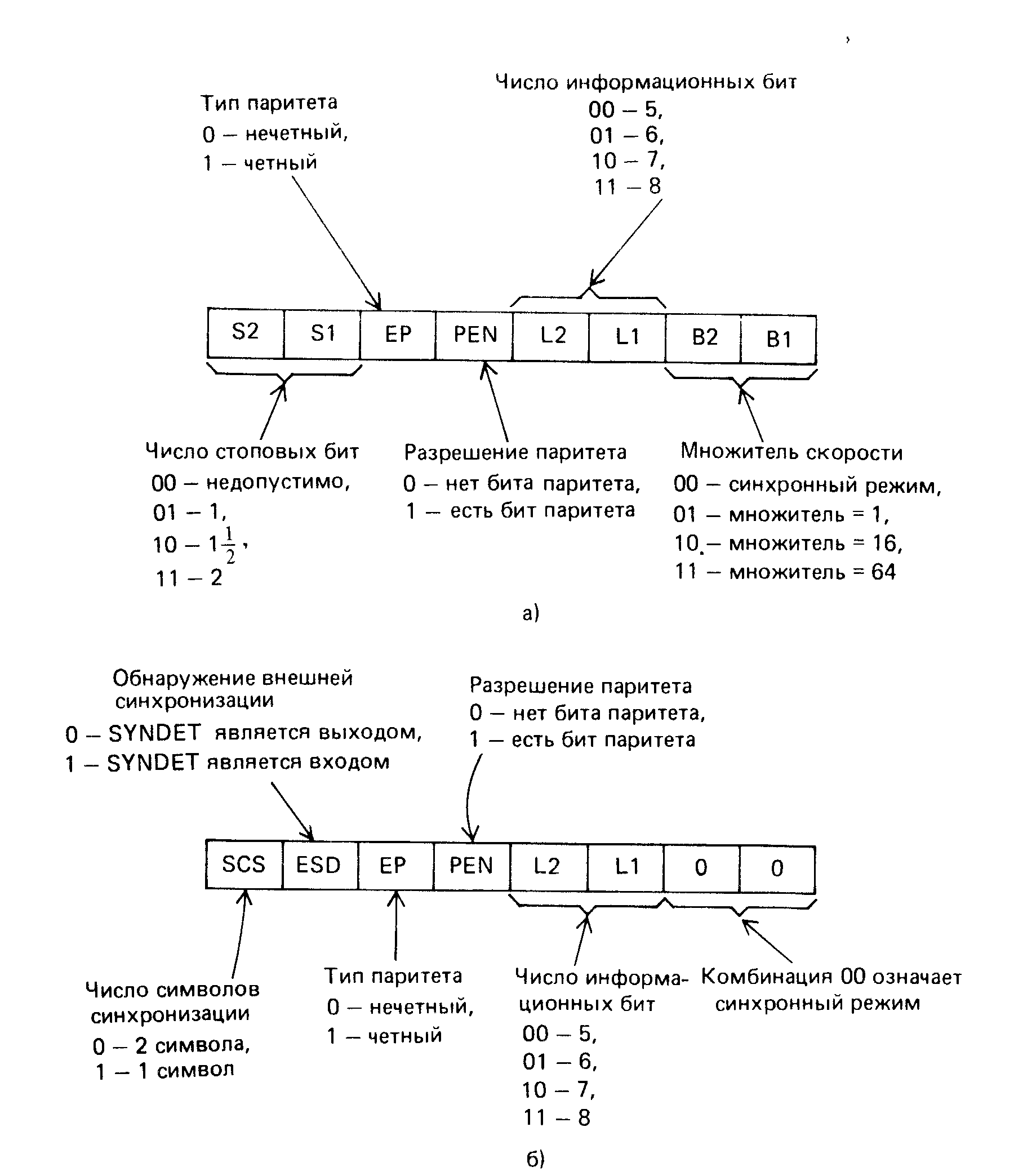

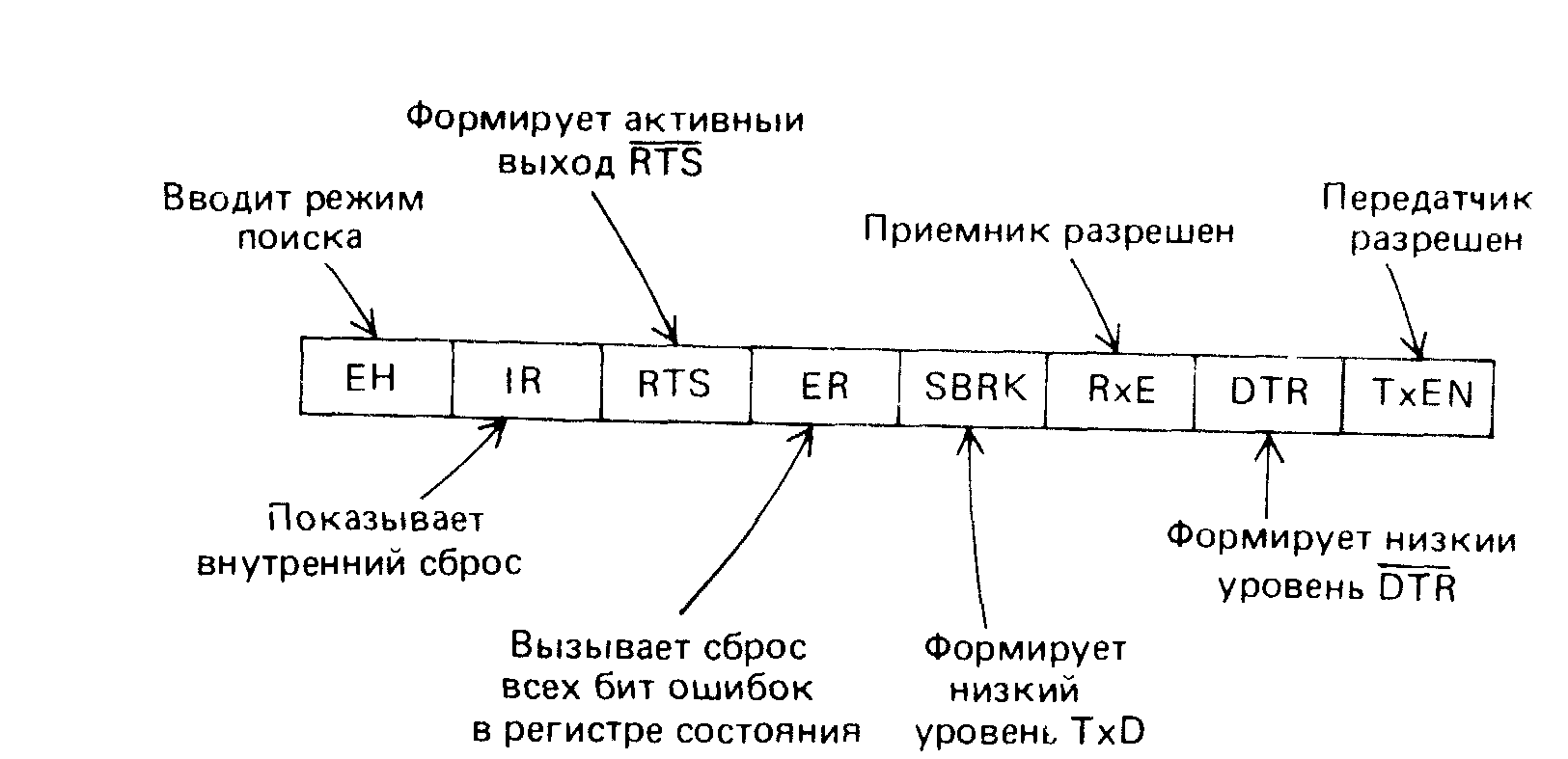

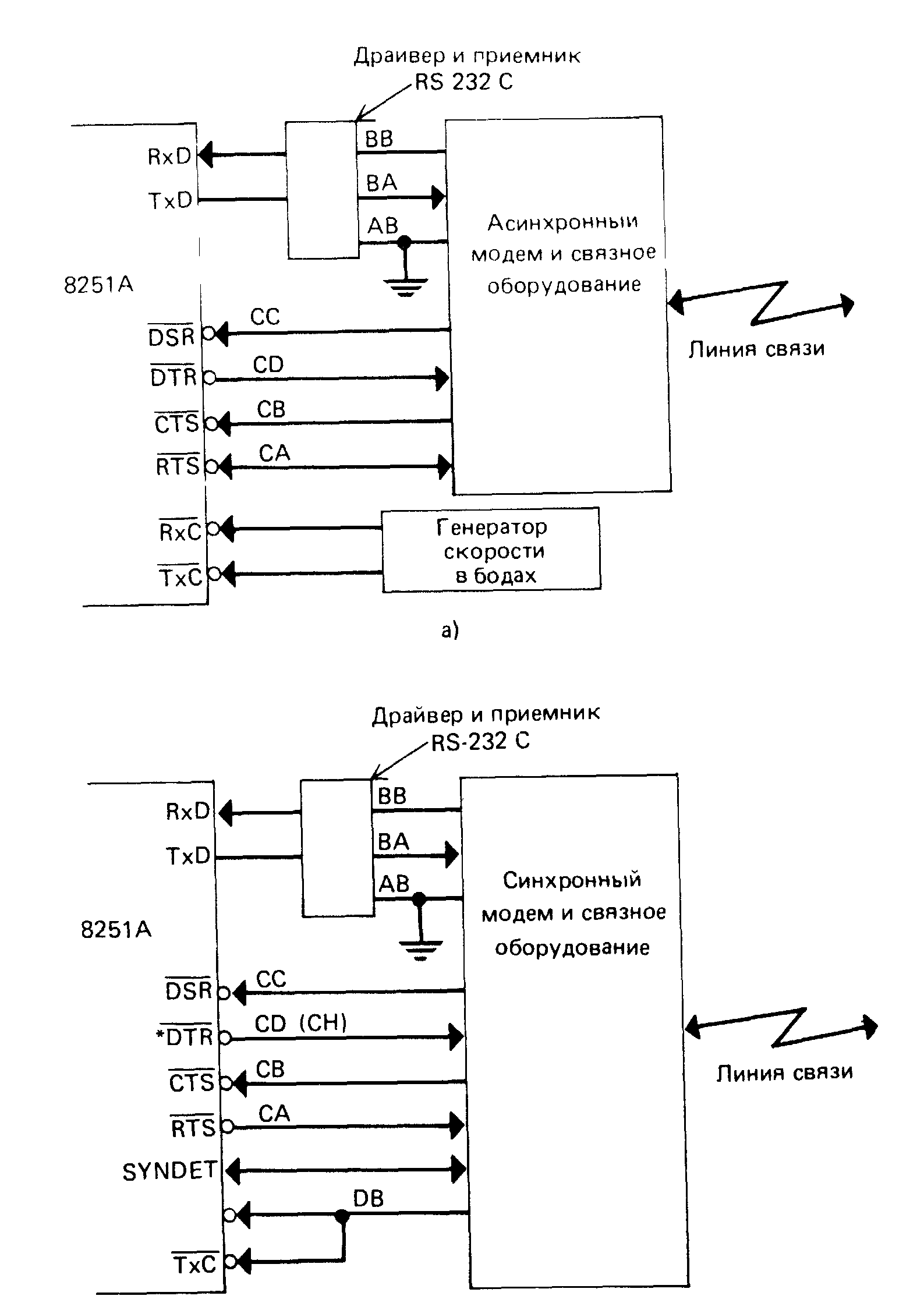

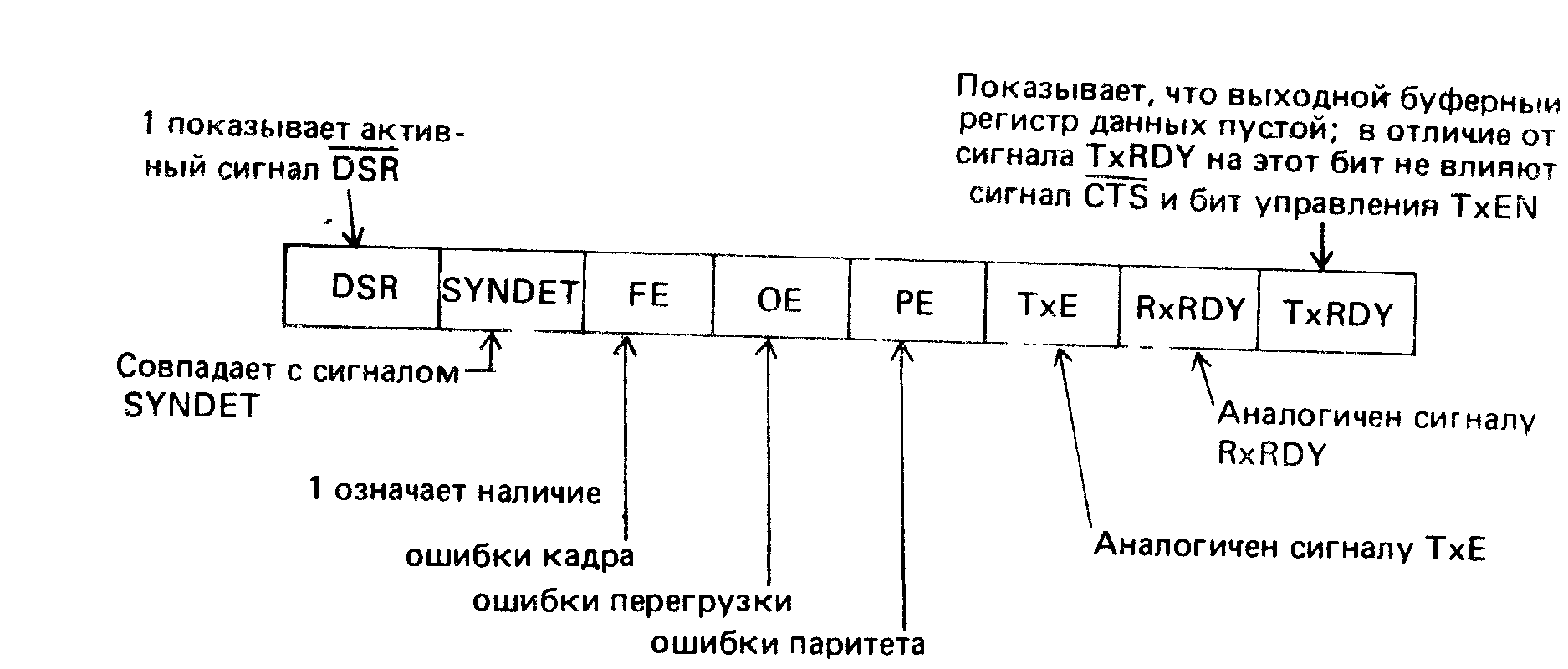

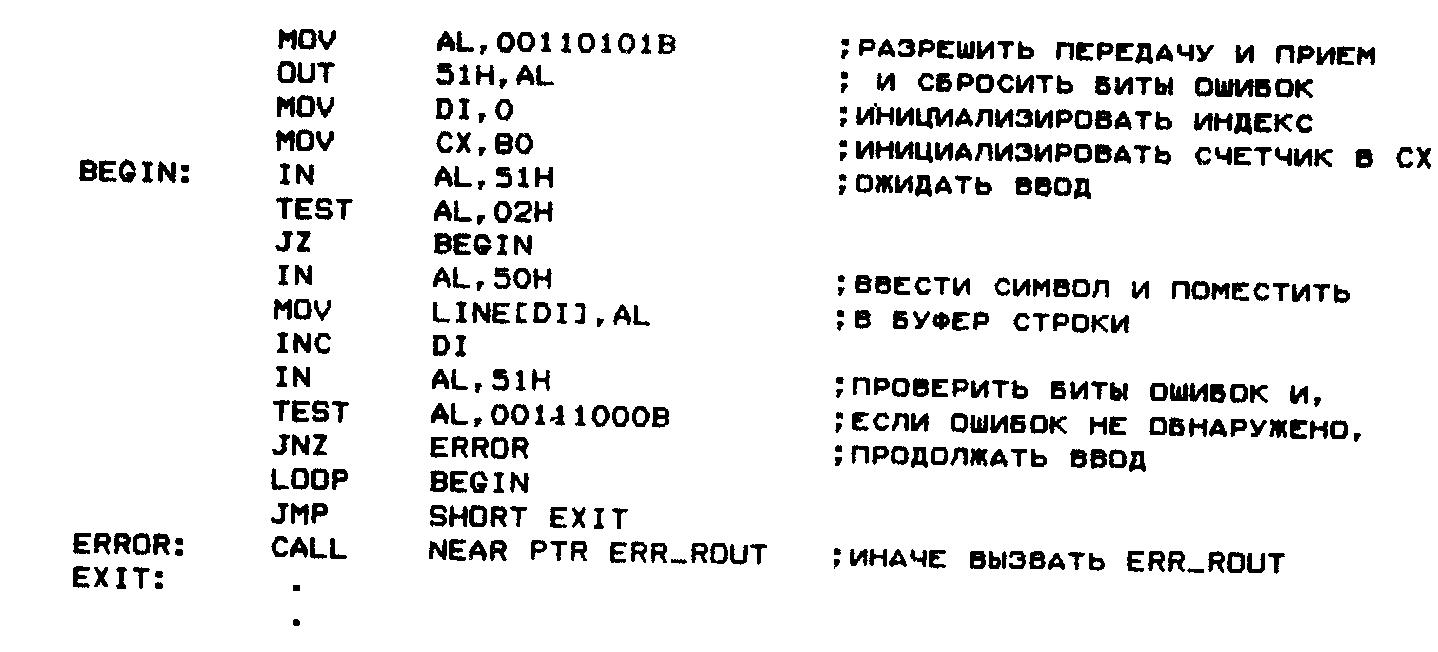

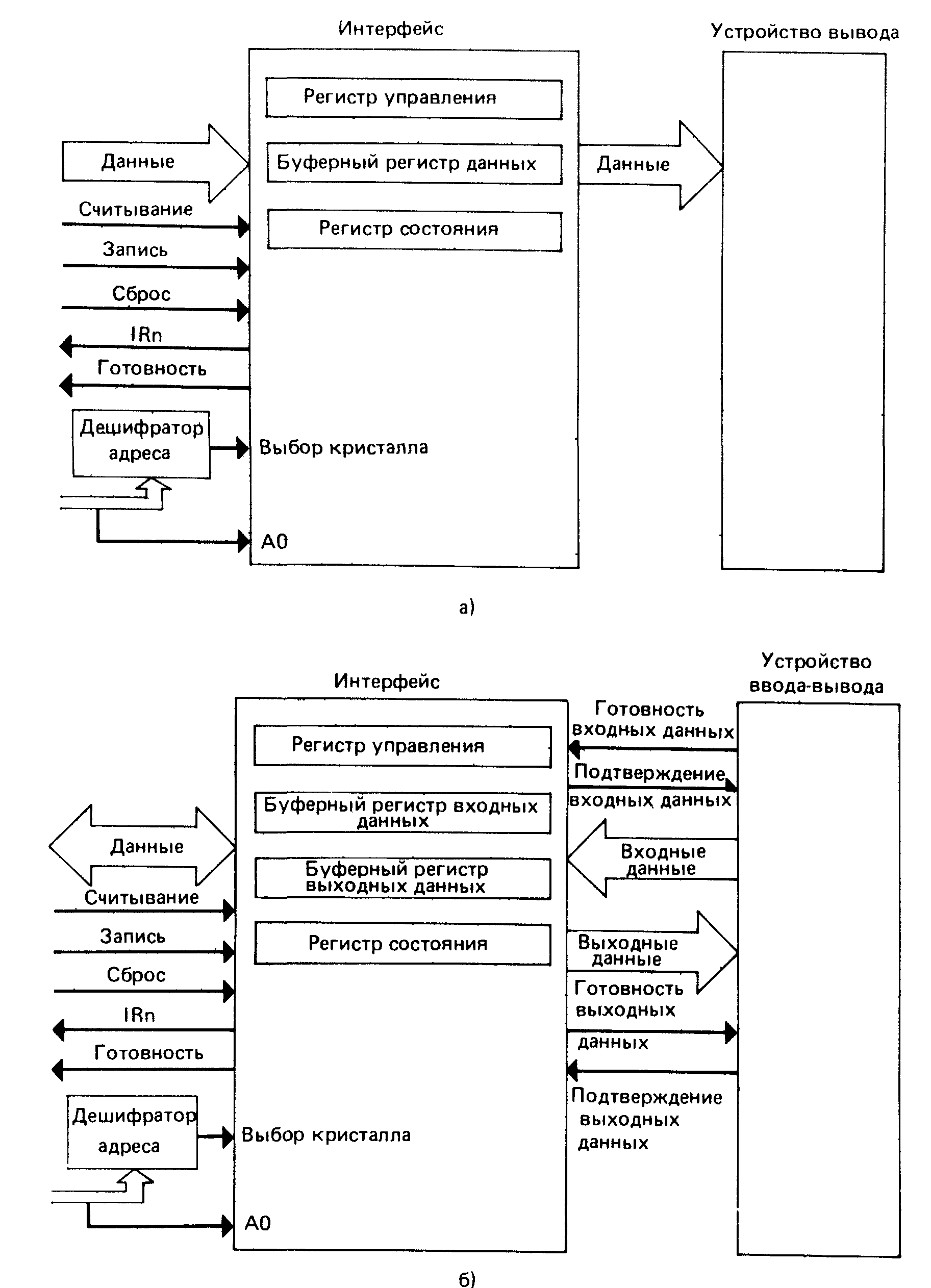

Частью стандарта RS-232-C являются определения и символические обозначения линий управления, содержащих интерфейс или терминал с модемом (см. рис. 9.11). Соединения обычно реализуются 25-контактными разъемами, номера контактов которых приведены во втором столбце. Номера в скобках, находящиеся в первом столбце, относятся к стандарту CCITT. Рис. 9.10. Схема согласования передающей и приемной линий интерфейса RS-232-C  Рис. 9.11. Определения линий управления стандарта RS-232-C Для связи по прямой телефонной линии требуются только восемь первых из показанных на рис. 9.11 линий. При передаче в модем посылается сигнал "запрос передачи" (СА), который подтверждается сигналом "сброса передачи" (СВ). Затем по линии "передаваемые данные" (ВА) начинается собственно передача. При приеме модем возбуждает сигнал на линии "детектор сигнала'"приемной линии" (CF), показывая прием сигнала от модема с другого конца линии связи. Принятые данные передаются в интерфейс или терминал по линии "принятые данные" (ВВ). Сигнал "готовность модема" означает, что модем включен и находится в рабочем режиме. Эта линия должна быть активной как при передаче, так и при приеме. Если линия связи является частью коммутируемой телефонной системы, потребуются еще минимум две линии. Сигнал в модем по линии ''готовность терминала" (CD) управляет коммутацией модема, что позволяет образовать линию связи. Модем посылает в интерфейс или терминал сигнал "индикатор звонка" (СЕ), показывая, что он принимает сигнал звонка. Для ответа на этот сигнал интерфейс или терминал должны реагировать активным сигналом "готовность терминала". Он заставляет модем отвечать "как звенящий телефон". В синхронной связи совместно с данными необходимо передавать синхронизирующую информацию. Для этого предусмотрены две линии "синхросигнал передатчика". Линия "источник DTE" (DA) служит для передачи синхронизирующей информации из интерфейса или терминала в модем, а линия "источник DCF" - для передачи в'другом направлении. Так как модемы синхронной связи часто допускают две скорости передачи данных или два диапазона скоростей, линии "селектор скорости данных" (СИ и С1) несут информацию о скорости передачи. По линии СН эта информация передается из интерфейса или терминала в модем, а по линии CI - в другом направлении, показывая текущую скорость передачи модема. В быстродействующих синхронной или асинхронной линиях связи оказалось эффективнее передавать информацию пакетами, содержащими наряду с данными идентификацию и информацию для обнаружения ошибок. Пакеты обычно применяют при взаимодействии компьютеров друг с другом. Вместе с передачей пакетов необходимы определенные квитирование и контроль, что лучше всего осуществить по вторичной (обратной) низкоскоростной линии связи. Последние пять линий, определенные на рис. 9.11, предназначены именно для вторичных передач. Мы не будем касаться этих линий, так как подробное рассмотрение пакетов и протоколов связи выходит за рамки книги. Следует отметить наличие еще одного стандарта на передачу данных между интерфейсом или терминалом и модемом. Он называется стандартом 20-мА петли и реализуется  Рис. 9.12. Схема передачи и приема сигналов 20-мА петли петлевой линией, в которой имеется ток 20 мА в состоянии маркера (1), а в состоянии пробела (0) ток отсутствует. В данной конфигурации одно из взаимодействующих устройств должно быть активным и служить источником тока, а другое устройство должно быть пассивным. Исторической основой этого стандарта являются механические телетайпы, в которых ток управлял соленоидами, но он сохранился даже в большинстве современных терминалов с дисплеем наряду со стандартом RS-232-C. Схемы для передачи и приема сигналов 20-мА токовой петли приведены на рис. 9.12. Мы не касались многих деталей стандартов. Имеется множество книг по теории и практике передачи данных, некоторые из которых упомянуты в списке литуратуры к данной главе. Мы стремились показать, как соединяются интерфейс компьютера и система связи, и дать информацию, необходимую при проектировании интерфейса.  Рис. 9.13. Последовательный связной интерфейс 8251А 9.1.4 Программируемый связной интерфейс Как пример устройства последовательного интерфейса, рассмотрим микросхему 8251А программируемого связного интерфейса, схема которой представлена Hd рис. 9.13. Эту микросхему можно запрограммировать для асинхронной или синхронной передачи. Буферные регистры входных и выходных данных разделяют порт с одним и тем же интерфейсом. Поспелова гельный двоичный погок со входа RxD вводится в регистр сдвига приемника, а затем биты данных передаются в буферный регистр входных данных, а отгуди в процессор. Выводимые биты данных процессор помещает в буферный регистр выходных данных, затем они передаются в регистр сдвига передатчика и вместе с битами синхронизации — на выход TxD. Содержимое регистра режима, который инициализируется выполняемой программой, определяет синхронный или асинхронный режим и формат передаваемых и принимаемых символов. Регистр управления, который также устанавливается программой, координирует работу интерфейса, а регистр состояния обеспечивает программе определенную информацию. Для синхронной связи необходимы регистры для хранения символов синхронизации. Несмотря на то, что процессор может адресовать семь регистров микросхемы, она ассоциируется с адресами всего двух портов. Вход C/D подключается к линии адреса АО и она дифференцирует адреса двух портов. Микросхема интерпретирует сигналы C/D. RD и WR в соответствии с табл. 9.1. Таблица 9.1 Интерпретация сигналов управления  Остальные комбинации сигналов переводят тристабильные выходы D7-DO в высоко" импедансное состояние. Выбор регистров режима, управления или символа синхронизации зависит от последовательности обращения, схема которой представлена на рис. 9.14. После аппаратного сброса или приказа с установленным в 1 битом сброса следующий вывод с АО = 1 (т. е. с C/D = 1, RD = 1 и WR = 0) предназначен для регистра режима. Форматы регистра режима для асинхронного и синхронного случаев показаны на рис. 9.15. Если два младших бита режима содержат нули, интерфейс переводится в синхронный режим и старший бит определяет число символов синхронизации. При этом следующие один или два байта, выводимые с АО = 1, становятся символами синхронизации. Если два младших бита режима не равны 0, интерфейс работает в асинхронном режиме. В любом случае все последующие байты до другого сброса направляются в регистр управления (если АО = 1) или в буферный регистр выходных данных (если АО = 0). В синхронном режиме скорости в бодах передатчика и приемника, равные частотам сдвига регистров сдвига, совпадают с частотами сигналов на входах ТхС и RxC соответственно. При работе в асинхронном режиме три оставшиеся комбинации младших бит в регистре режимов определяют множитель скорости. Взаимосвязь между частотами  Рис. 9.14. Схема размещения выводимых байт Т\С и RxC входов синхронизации и скоростями в бодах передатчика и приемника имеет следующий вид частота синхронизации = множитель X скорость в бодах. Когда младшие биты регистра режима содержат 10 и скорости в бодах передатчика и приемника равны 300 и 1200, частота на входе ТхС должна быть 4800 Гц, а на входе "RxC - 19,2 кГц В обоих режимах биты 2 и 3 показывают число информационных бит в каждом символе, бит 4 определяет наличие или отсутствие бита паритета, а бит 5 - тип паритета (нечетный или четный). В асинхронном режиме два старших бита показывают число стоповых бит. Для синхронного режима бит 6 показывает, каким является сигнал SYNDET-входным или выходным, а бит 7 задает число символов синхронизации  Рис. 9.15. Форматы регистра режима: асинхронный (а) и синхронный (б) Если контакт SYNDET служит выходом, его сигнал становится активным, когда обнаружено соответствие входного двоичного потока и символа (ов) синхронизации. Когда же поиск символов синхронизации осуществляется внешним устройством, на вход SYNDET подается сигнал о фиксации соответствия. Этот же контакт, но только в качестве выхода применяется и при асинхронной работе. Сигнал на этом выходе называется сигналом обнаружения разрыва и он высоким уровнем отмечает прием символа, состоящего из одних нулей. Формат регистра управления приведен на рис. 9.16. Бит 0 этого регистра должен содержать 1 до вывода данных, а бит 2 должен быть в состоянии 1 до приема данных. Программный ответ модему осуществляется установкой в 1 бита 1, так как при этом на выходе DTR формируется 0, а инверсия DTR обычно подключается к линии CD модема. Состояние 1 бита 3 формирует TxD = 0, вызывая передачу символов разрыва.  Рис. 9.16. Формат регистра управления Примечание. Во всех случаях действие предпринимается, когда бит установлен в 1 Установка в 1 бита 4 вызывает сброс всех бит ошибок в регистре состояния. Бит 5 применяется для выдачи сигнала "запрос передачи" (RTS) в модем. Если инверсия сигнала на контакте RTS подключена к линии СА модема, то загрузка 1 в бит 5 вызывает высокий уровень на линии СА. Установка бита 6 в состояние 1 вызывает реинициализацию 8251А и переход к последовательности сброса (т. е. осуществляется возврат в начало схемы на рис. 9.14 и следующий вывод производится в регистр режима). Бит 7 применяется только в синхронном режиме; установка его в 1 заставляет 8251А начать поиск символа (ов) синхронизации На рис. 9.17. показаны типичные схемы подключения к модемам для асинхронной и синхронной передач. При синхронной передаче предполагается, что синхронизацией управляет модем и его связное оборудование. Кроме того, если это же оборудование применяется для обнаружения символа (ов) синхронизации, оно информирует 8251А об их обнаружении по линии SYNDET. С другой стороны, если символ (ы) синхронизации отыскивает сам 8251А, он может использовать линию SYNDET, чтобы сообщить модему об успешном поиске. Для удовлетворения требований стандарта RS-232-C необходимы драйверы и приемники, преобразующие ТТЛ-совместимые сигналы TxD и RxD в требуемые уровни напряжения (см рис. 9.10) Ниже приведен программный фрагмент, который инициализирует регистр режима и содержит приказ разрешения передатчика и запуска асинхронной передачи со следующим форматом: 7 бит символа, бит четного паритета и 2 стоповых бита. MOV AL,11111010B OUT 51H,AL MOV AL,00110011B OUT 51H,AL Здесь предполагается, что регистры режима и управления имеют адрес 51Н, а частоты синхронизации в 16 раз больше соответствующих скоростей в бодах. Следующий фрагмент переводит 8251А в синхронный режим и заставляет его начать поиск двух смежных символов синхронизации: MOV AL,00111000B OUT 51H,AL MOV A1_,16H OUT 51H,AL MOV AL,10010100B OUT 51H,AL 338  Можно также использовать для выбора скорости - линия модема СН б) Рис. 9.17. Подключения микросхемы 8251А к асинхронному (а) и синхронному (б) модему Примечание. Подключения линий управления зависят от спецификаций модема Как и в первом примере, символы содержат 7 информационных бит и бит четного паритета, но, разумеется, стоповые биты отсутствуют. Формат регистра состояния приведен на рис. 9.18. Биты 1, 2 и 6 отражают состояния сигналов RxRDY, TxE и SYNDET. Бит TxRDY показывает, что буфер выходных данных  Рис. 9.18. Формат регистра состояния пустой. В отличие от контакта TxRDY на этот бит не влияет входной сигнал CTS или бит управления TxEN. Бит RxRDY показывает, что символ принят и готов для ввода в процессор. Биты TxRDY и RxRDY можно использовать для программного ввода-вывода, а сигналы с соответствующих контактов можно подключить к линиям запросов прерываний для организации ввода-вывода по прерываниям. Бит TxRDY автоматически сбрасывается, когда имеется символ для передачи, а бит RxRDY - когда установивший его символ введен процессором. Бит 2 показывает, что регистр сдвига передатчика ожидает загрузки символа из буферного регистра выходных данных._В синхронной передаче, пока этот бит установлен, передатчик будет брать данные из регистров символов синхронизации до загрузки данных в буферный регистр выходных данных. Биты 3, 4 и 5 показывают ошибки паритета, перегрузки и кадра. Когда обнаруживается ошибка, соответствующий ей бит устанавливается в 1. Если инверсию выхода DSR подключить к линии СС, то бит 7 отражает состояние модема - он устанавливается в 1, когда модем включен и находится в рабочем режиме. На рис. 9.19 приведена типичная программа, в которой используется программный ввод-вывод для ввода 80 символов из 8251А (адрес буферного регистра данных равен 0050) и размещения их в буфере памяти, начинающегося с LINE. Внутренний цикл непрерывно проверяет бит RxRDY до тех пор, пока он не устанавливается символом, принятым в буферный регистр входных данных. Затем новый принятый символ пересыла-  Рис. 9.19. Ввод строки символов через интерфейс 8251А ется в память и контролируются биты ошибок Если текущий символ появился до ввода предыдущего символа или во время передачи возникли ошибки паритета или кадра, ввод прекращается и вызывается процедура обработки ошибки, которая обычно проверяет отдельные биты ошибок, печатает соответствующее сообщение и сбрасывает биты ошибок. Ввод символа автоматически сбрасывает бит RxRDY, поэтому если другой символ не принят до начала внутреннего цикла, внутренний цикл должен повторяться до тех пор, пока следующий входной символ не установит RxRDY = 1. Если входные символы имеют меньше 8 бит, неиспользуемые старшие биты в буферном регистре данных всегда возвращаются в состояние 0. Бит паритета не передается в процессор, поэтому контроль ошибок паритета можно осуществить только по состоянию бита ошибки паритета в регистре состояния. Когда при выводе длина символов меньше 8 бит, ненужные старшие биты в буферном регистре выходных данных игнорируются. 9.2 ПАРАЛЛЕЛЬНАЯ СВЯЗЬ Параллельная связь осуществляется одновременной передачей нескольких бит по отдельным линиям. Ее преимущество по сравнению с последовательной связью заключается в том, что для линий с заданной максимальной двоичной скоростью обеспечивается более высокая скорость передачи информации. Недрстажем же является, конечно, стоимость дополнительных пиний, и так как расходы увеличиваются с расстоянием, ' параллельная связь применяется на большие расстояния, если только требуется высокая скорость передачи данных. В отличие от-лоследовательной связи четкие стандарты на параллельную связь отсутствуют. Параллеяьные передачи выполняются либо простым помещением данных в буферный регистр выходных данных интерфейса или восприятием данных из буферного регистра входных данных интерфейса, либо .ими управляют сигналы квитирования и (или) синхронизации. Обычно одновременно передается один символ <или другая единица информации) и необходимости определения конца символа или начала передачи не возникает. Четко определенный формат синхронной или асинхронной передачи отсутствует, но, если действия устройства и интерфейса координирует сигнал синхронизации, передача считается синхронной. Если же применяются только квитирующие сигналы, передача считается асинхронной. Интерфейс можно спроектировать только на вывод, только на ввод, на ввод и вывод по отдельным наборам линий, или выполнять ввод-вывод по одному набору двунаправленных линий. Если интерфейс подключен к строчному принтеру, т должен только выводить данные, а если он обслуживает карточный считыватель, интерфейс должен телько-вводить данные. В интерфейсе, обслуживающем перфоленточные считыватель и перфоратор, потребуются один набор входных линий и один набор выходных линий, но в интерфейсе для устройства, которое не производит одновременные ввод и вывод данных, можно применить один набор двунаправленных линий. "ь На рис. 9.20, а показан типичный выходной параллельный интерфейс, в котором отсутствуют линии управления. В этом случае содержимое буферного регистра данных постоянно выдается на линии данных, связывающие интерфейс и устройство вывода. Если устройство вывода состоит из регистра-защелки и управляемого им набора реле, компьютер может управлять этими реле, просто помещая данные в буферный регистр данных. На рис. 9.20, б изображен типичный параллельный интерфейс с линиями квитирования и отдельными подключениями к периферийному устройству для ввода и вывода. В этом случае при в'ВоДе данные сначала помещаются на шину данных, а затем на линии готовности входных данных устанавливается 1. Интерфейс должен отреагировать загрузкой данных в буфер входных данных и формированием 1 на пинии подтверждения вход:  Рис. 9.20. Типичные интерфейсы параллельной связи: а — только ввод; б — ввод-вывод ных данных. При получении подтверждения устройство снимает сигналы данных и готовности. Когда интерфейс принял данные, он устанавливает бит состояния "готовность" и, возможно, посылает сигнал запроса прерывания. После того как процессор вводит данные, .гюерфьйх- сбрасывав i бит состояния s готовность" и перевопит лина-и данных в высокоимгедансно! состояние. Ei-ли был „делан запрос прерывания, он обрабатывается обычным образом При выводе интерфейс устанавливает бит состояния "го",овнос1ь' и, возможно, формирует запрос прерывания, когда буфер выходных данных освободился- После того как процессор выводит данные, интерфейс сбрасывает ^л \ остояния ' готовность", помещает данные на шину выходных данных и сигналичируе'! у( тройству по линии готовности выходных данных. Когда > стройстзо готово воспринять данные, оно загружает их в регистр-защелку, а затем возвращает подтверждение. После этого интерфейс снимает сигнал готовности выходных данных и вновь устанавливает бит состояния "готовность". |