Архитектура ЭВМ и систем (конспект лекций). Конспект лекций

Скачать 1.1 Mb. Скачать 1.1 Mb.

|

|

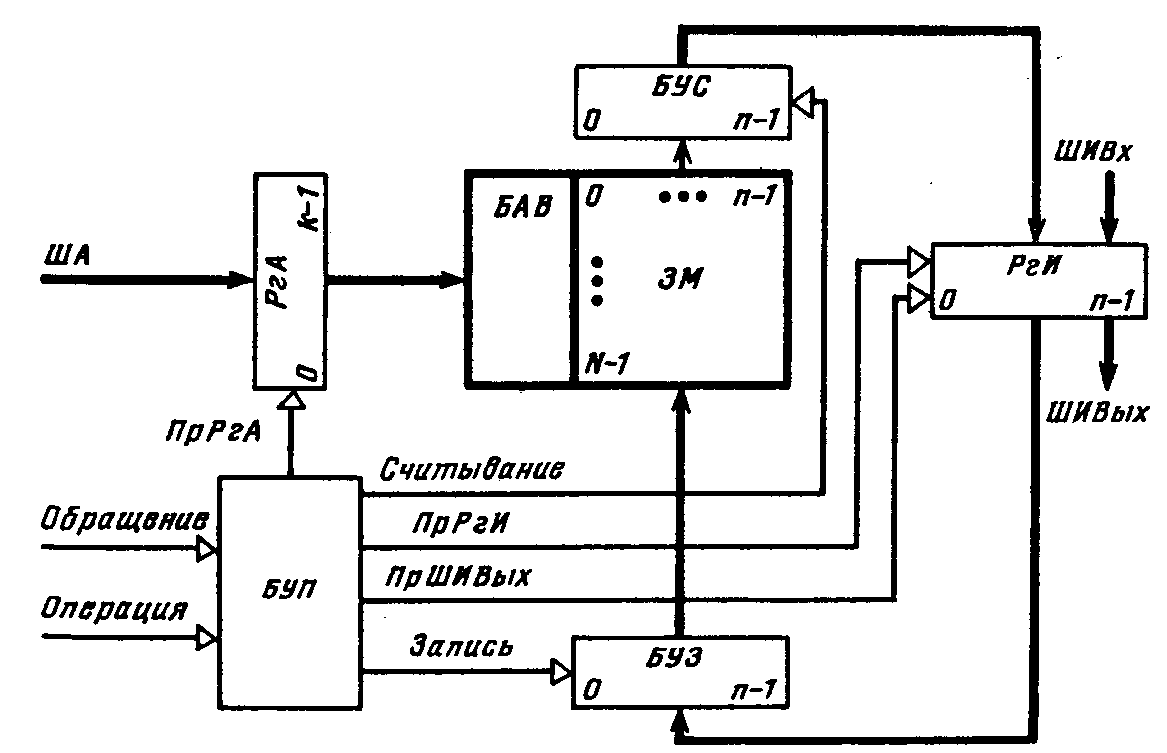

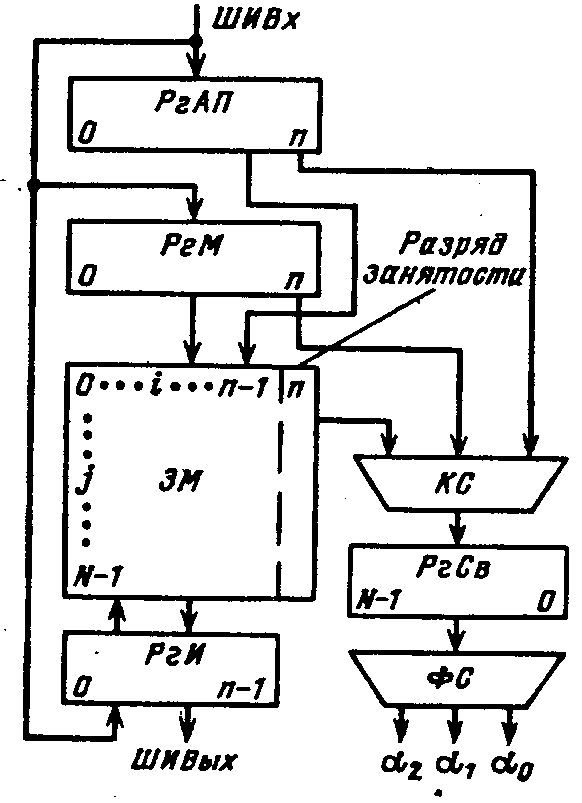

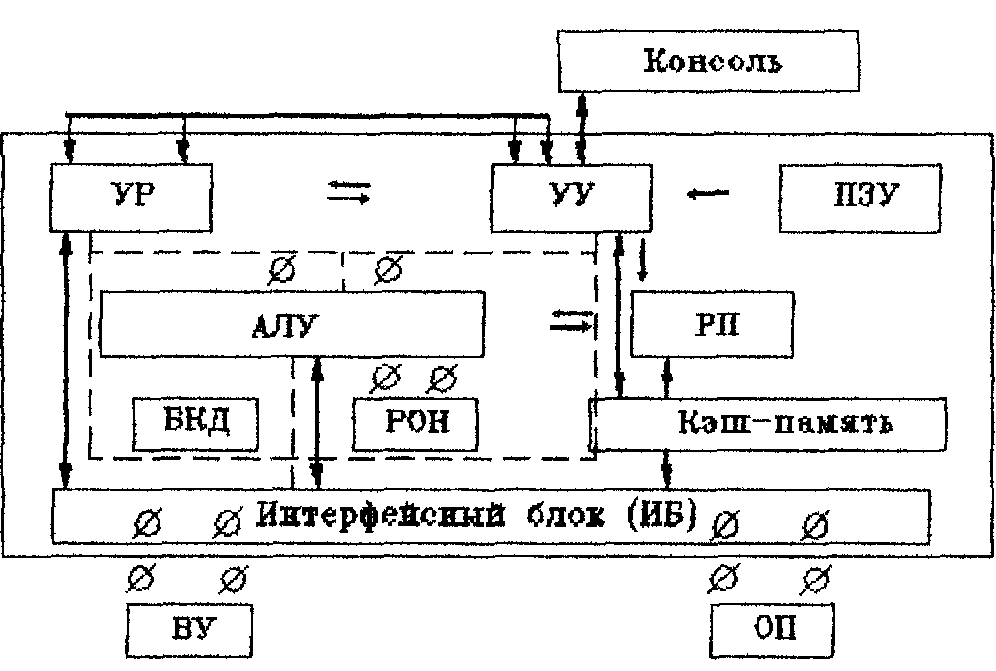

2.1. Общие сведения и классификация устройств памяти Памятью ЭВМ называется совокупность устройств, служащих для запоминания, хранения и выдачи информации. Отдельные устройства, входящие в эту совокупность, называют запоминающими устройствами или памятями того или иного типа. Производительность и вычислительные возможности ЭВМ в значительной степени определяются составом и характеристиками ее ЗУ. В составе ЭВМ используется одновременно несколько типов ЗУ, отличающихся принципом действия, характеристиками и назначением. Основными операциями в памяти являются занесение информации в память — запись и выборка информации из памяти — считывание. Обе эти операции называются обращением к памяти. При обращении к памяти производится считывание или запись некоторой единицы данных — различной для устройств разного типа. Такой единицей может быть, например, байт, машинное слово или блок данных. Важнейшими характеристиками отдельных устройств памяти (запоминающих устройств) являются емкость памяти, удельная емкость, быстродействие. Емкость памяти определяется максимальным количеством данных, которые могут в ней храниться. Удельная емкость есть отношение емкости ЗУ к его физическому объему. Плотность записи есть отношение емкости ЗУ к площади носителя. Например, у HDD емкостью до 10 Гб плотность записи составляет 2 Гбит на кв. дюйм. Быстродействие памяти определяется продолжительностью операции обращения, т. е. временем, затрачиваемым на поиск нужной единицы информации в памяти и на ее считывание (время обращения при считывании), или временем на поиск места в памяти, предназначаемого для хранения данной единицы информации, и на ее запись в память (время обращения при записи). Продолжительность обращения к памяти (время цикла памяти) при считывании где В некоторых устройствах памяти считывание информации сопровождается ее разрушением (стиранием). В таком случае цикл обращения должен содержать операцию восстановления (регенерации) считанной информации на прежнем месте в памяти. Продолжительность обращения (время цикла) при записи где В качестве продолжительности цикла обращения к памяти принимается величина В зависимости от реализуемых в памяти операций обращения различают: а) память с произвольным обращением (возможны считывание и запись данных в память); б) память только для считывания информации («постоянная» или «односторонняя»). Запись информации в постоянную память производится в процессе ее изготовления или настройки. Эти типы памяти соответствуют терминам RAM (random access memory — память с произвольным обращением) и ROM (read only memory — память только для считывания). По способу организации доступа различают устройства памяти с непосредственным (произвольным), с прямым (циклическим) и последовательным доступами. В памяти с непосредственным (произвольным) доступом время доступа, а поэтому и цикл обращения не зависят от места расположения участка памяти, с которого производится считывание или в который записывается информация. В большинстве случаев непосредственный доступ реализуется при помощи электронных (полупроводниковых) ЗУ. В подобных памятях цикл обращения обычно составляет 70 и менее наносекунд. Количество разрядов, считываемых или записываемых в памяти с непосредственным доступом параллельно во времени за одну операцию обращения, называется шириной выборки. В двух других типах памяти используются более медленные электромеханические процессы. В устройствах памяти с прямым доступом, к которым относятся дисковые устройства, благодаря непрерывному вращению носителя информации возможность обращения к некоторому участку носителя для считывания или записи циклически повторяется. В такой памяти время доступа составляет обычно от нескольких долей секунды до нескольких десятков миллисекунд. В памяти с последовательным доступом производится последовательный просмотр участков носителя информации, пока нужный участок носителя не займет некоторое исходное положение. Характерным примером является ЗУ на магнитных лентах, т.н. стримеры (streamer). Время доступа может в неблагоприятных случаях расположения информации достигнуть нескольких минут. Хорошим примером ленточного накопителя является применение адаптера АРВИД с VHS видеомагнитофоном. Емкость этого накопителя составляет 4ГБ/180мин. Запоминающие устройства различаются также по выполняемым в ЭВМ функциям, зависящим в частности, от места расположения ЗУ в структуре ЭВМ. Требования к емкости и быстродействию памяти являются противоречивыми. Чем больше быстродействие, тем технически труднее достигается и дороже обходится увеличение емкости памяти. Стоимость памяти составляет значительную часть общей стоимости ЭВМ. Поэтому память ЭВМ организуется в виде иерархической структуры запоминающих устройств, обладающих различными быстродействием и емкостью. В общем случае ЭВМ содержит следующие типы памяти, в порядке убывания быстродействия и возрастания емкости. Иерархическая структура памяти позволяет экономически эффективно сочетать хранение больших объемов информации с быстрым доступом к информации в процессе обработки. Таблица 2.1. Оперативной или основной памятью (ОП) называют устройство, которое служит для хранения информации (данных программ, промежуточных и конечных результатов обработки), непосредственно используемой в процессе выполнения операций в арифметико-логическом устройстве (АЛУ) и устройстве управления (УУ) процессора. В процессе обработки информации осуществляется тесное взаимодействие процессора и ОП. Из ОП в процессор поступают команды программы и операнды, над которыми производятся предусмотренные командой операции, а из процессора в ОП направляются для хранения промежуточные и конечные результаты обработки. Характеристики ОП непосредственно влияют на основные показатели ЭВМ и в первую очередь на скорость ее работы. На текущий момент оперативная память имеет емкость от нескольких МБ до нескольких ГБ и цикл обращения около 60 нс и менее. Запоминающие устройства ОП изготовляются на интегральных микросхемах с большой степенью интеграции (полупроводниковые ЗУ). В последнее время ряд фирм заявили о начале серийного выпуска чипов динамической памяти емкостью 1Гб. Признанным лидером является Samsung. Самым массовым изделием на сегодняшний день можно считать 64 Мб чипы. В ближайший год предполагается широкое применение 128Мб и 256Мб чипов. В ряде случаев быстродействие ОП оказывается недостаточным, и в состав машины приходится включать СОП (буферную или кэш-память на несколько сотен или тысяч килобайт с циклом обращения, составляющим несколько наносекунд. Такие СОП выполняются на чипах статической памяти. Быстродействие КЭШа должно соответствовать скорости работы арифметико-логических и управляющих устройств процессора. Сверхоперативная (буферная) память используется для промежуточного хранения считываемых процессором из ОП участков программы и групп данных, в качестве рабочих ячеек программы, индексных регистров, для хранения служебной информации, используемой при управлении вычислительным процессом. Она выполняет роль согласующего звена между быстродействующими логическими устройствами процессора и более медленной ОП. В качестве ОП и СОП используются быстродействующие ЗУ с произвольным обращением и непосредственным доступом. Обычно емкость ОП оказывается недостаточной для хранения всех необходимых данных в ЭВМ. Поэтому ЭВМ содержит в своем составе несколько ЗУ с прямым доступом на дисках (емкость одного ЗУ на HDD дисках 1 - 30 Гбайт) и несколько ЗУ с последовательным доступом на магнитных лентах (емкость одного ЗУ 4 – 35 Гбайт). Оперативная память вместе с СОП и некоторыми другими специализированными памятями процессора образуют внутреннюю память ЭВМ (рис. 4.1). Электромеханические ЗУ образуют внешнюю память ЭВМ, а сами они поэтому называются внешними запоминающими устройствами (ВЗУ). Запоминающее устройство любого типа состоит из запоминающего массива, хранящего информацию, и блоков, служащих для поиска в массиве, записи и считывания (а в ряде случаев и для регенерации) информации. 2.2 Адресная, ассоциативная и стековая организации памяти Запоминающее устройство с произвольным обращением, как правило, содержит множество одинаковых запоминающих элементов, образующих запоминающий массив (ЗМ). Массив разделен на отдельные ячейки; каждая из них предназначена для хранения двоичного кода, число разрядов в котором определяется шириной выборки памяти (в частности, это может быть одно, половина или несколько машинных слов). Способ организации памяти зависит от методов размещения и поиска информации в запоминающем массиве. По этому признаку различают адресную, ассоциативную и стековую (магазинную) памяти. Адресная память. В памяти с адресной организацией размещение и поиск информации в ЗМ основаны на использовании адреса хранения слова (числа, команды и т. п.). Адресом служит номер ячейки ЗМ, в которой это слово размещается. При записи (или считывании) слова в ЗМ инициирующая эту операцию команда должна указывать адрес (номер ячейки), по которому производится запись (считывание). Типичная структура адресной памяти, содержит запоминающий массив из N-разрядных ячеек и его аппаратное обрамление, включающее в себя регистр адреса РгА, имеющий k (k log N) разрядов, информационный регистр РгИ, блок адресной выборки БАВ, блок усилителей считывания БУС, блок разрядных усилителей-формирователей сигналов записи БУЗ и блок управления памятью БУП. По коду адреса в РгА БАВ формирует в соответствующей ячейке памяти сигналы, позволяющие произвести в ячейке считывание или запись слова. Ц  Рис.2.1. Структура адресной памяти с произвольным обращением. икл обращения к памяти инициируется поступлением в БУП извне сигнала Обращение. Общая часть цикла обращения включает в себя прием в РгА с шины адреса ША адреса обращения и прием в БУП и расшифровку управляющего сигнала Операция, указывающего вид запрашиваемой операции (считывание или запись). Далее при считывании БАВ дешифрирует адрес, посылает сигналы считывания в заданную адресом ячейку ЗМ, при этом код записанного в ячейке слова считывается усилителями считывания БУС и передается в РгИ. Операция считывания завершается выдачей слова из РгИ на выходную информационную шину ШИВых. При записи помимо выполнения указанной выше общей части цикла обращения производится прием записываемого слова с входной информационной шины ШИВх и РгИ. Затем в выбранную БАВ ячейку записывается слово из РгИ. Блок управления БУП генерирует необходимые последовательности управляющих сигналов, инициирующих работу отдельных узлов памяти. Ассоциативная память. В памяти этого типа поиск нужной информации производится не по адресу, а по ее содержанию (по ассоциативному признаку). При этом поиск по ассоциативному признаку (или последовательно по отдельным разрядам этого признака) происходит параллельно во времени для всех ячеек запоминающего массива. Во многих случаях ассоциативный поиск позволяет существенно упростить и ускорить обработку данных. Это достигается за счет того, что в памяти этого типа операция считывания информации совмещена с выполнением ряда логических операций. Типичная структура ассоциативной памяти представлена на рис. 4.3. Запоминающий массив содержит N (n+1)-разрядных ячеек. Для указания занятости ячейки используется служебный n-й разряд (0 — ячейка свободна, 1 — в ячейке записано слово).  Рис. 2.2. Структура ассоциативной памяти По входной информационной шине ШИВх в регистр ассоциативного признака РгАП в разряды 0..n-1 поступает n-разрядный ассоциативный запрос, а в регистр маски РгМ — код маски поиска, при этом n-разряд РгМ устанавливается в 0. Ассоциативный поиск производится лишь для совокупности разрядов РгАП, которым соответствуют 1 в РгМ (незамаскированные разряды РгАП). Для слов, в которых цифры в разрядах совпали с незамаскированными разрядами РгАП, комбинационная схема КС устанавливает в 1 соответствующие разряды регистра совпадения РгСв и 0 в остальные разряды. Таким образом, значение j-го разряда в РгСв определяется выражением РгСв(j)= где РгАП[i], РгМ[i] и ЗМ[j, i] — значения i-го разряда соответственно РгАП, РгМ и j-и ячейки ЗМ. Комбинационная схема формирования результата ассоциативного обращения ФС формирует из слова, образовавшегося в РгСв, сигналы 0, 1, 2, соответствующие случаям отсутствия слов в ЗМ, удовлетворяющих ассоциативному признаку, и наличия одного (и более) такого слова. Формирование содержимого РгСв и сигналов 0, 1, 2 по содержимому РгАП, РгМ и ЗМ называется операцией контроля ассоциации. Эта операция является составной частью операций считывания и записи, хотя она имеет и самостоятельное значение. При считывании сначала производится контроль ассоциации по ассоциативному признаку в РгАП. Затем при 0 = 1 считывание отменяется из-за отсутствия искомой информации, при 1 = 1 считывается в РгИ найденное слово, при 2 = 1 в РгИ считывается слово из ячейки, имеющей наименьший номер среди ячеек, отмеченных 1 у РгСв. Из РгИ считанное слово выдается на ШИВых. При записи сначала отыскивается свободная ячейка. Для этого выполняется операция контроля ассоциации при РгАП = 111...10 и РгМ = 00...01, при этом свободные ячейки отмечаются 1 в РгСв. Для записи выбирается свободная ячейка с наименьшим номером. В нее записывается слово, поступившее с ШИВх в РгИ. С помощью операции контроля ассоциации можно, не считывая слов из памяти, определить по содержимому РгСв, сколько в памяти слов, удовлетворяющих ассоциативному признаку, например реализовать запросы типа сколько студентов в группе имеют отличную оценку по данной дисциплине. При использовании соответствующих комбинационных схем в ассоциативной памяти могут выполняться достаточно сложные логические операции, такие, как поиск большего (меньшего) числа, поиск слов, заключенных в определенных границах, поиск максимального (минимального) числа и др. Ассоциативная память применяется, например, в аппаратуре динамического распределения ОП. Отметим, что для ассоциативной памяти необходимы запоминающие элементы, допускающие считывание без разрушения записанной в них информации. Это связано с тем, что при ассоциативном поиске считывание производится по всему ЗМ для всех незамаскированных разрядов и негде сохранять временно разрушаемую считыванием информацию. С  Рис.2.3. Стековая память. Рис.2.3. Стековая память.тековая память, так же как и ассоциативная, является безадресной. Стековую память можно рассматривать как совокупность ячеек, образующих одномерный массив, в котором соседние ячейки связаны друг с другом разрядными цепями передачи слов. Запись нового слова производится в верхнюю ячейку (ячейку 0), при этом все ранее записанные слова (включая слово, находившееся в ячейке 0), сдвигаются вниз, в соседние ячейки с большими на 1 номерами. Считывание возможно только из верхней (нулевой) ячейки памяти, при этом, если производится считывание с удалением, все остальные слова в памяти сдвигаются вверх, в соседние ячейки с большими номерами. В этой памяти порядок считывания слов соответствует правилу: последним поступил — первым обслуживается. В ряде устройств рассматриваемого типа предусматривается также операция простого считывания слова из нулевой ячейки (без его удаления и сдвига слова в памяти). Иногда стековая память снабжается счетчиком стека СчСт, показывающим количество занесенных в память слов. Сигнал СчСт = 0 соответствует пустому стеку, СчСт = N - 1 — заполненному стеку. Обычно стековую память организуют, используя адресную память. В этом случае счетчик стека, как правило, отсутствует, так как количество слов в памяти можно выявить по указателю стека. Широкое применение стековая память находит при обработке вложенных структур данных, при выполнении безадресных команд и прерываний. Архитектурная организация процессора ЭВМ Процессор занимает в архитектуре ЭВМ центральное место, осуществляя управление взаимодействием всех основных компонент, входящих в состав ЭВМ Он непосредственно осуществляет обработку информации, и программное управление данным процессом дешифрирует и выполняет команды программ, организует обращения к оперативной памяти (ОП), в нужных случаях инициирует операции ввода/вывода и работу периферийных устройств, воспринимает и обрабатывает запросы, поступающие как от устройств ЭВМ, так и из внешней среды (организация системы прерываний). Выполнение каждой команды состоит из выполнения более мелких операций - микрокоманд, выполняющих определенные элементарные действия. Набор микрокоманд определяется системой команд и логической структурой конкретной ЭВМ. Таким образом, каждая команда ЭВМ реализуется соответствующей микропрограммой, хранящейся в постоянном запоминающем устройстве (ПЗУ). В некоторых ЭВМ (в первую очередь, специализированных) все или часть команд реализуются аппаратно, что позволяет повышать их производительность за счет потери определенной части гибкости системы команд машины. Как один, так и второй способ реализации команд ЭВМ имеет свои плюсы и минусы. Я  Рис 1 Функциональная схема центрального процессора ЭВМ Рис 1 Функциональная схема центрального процессора ЭВМ зык микропрограммирования предназначен для описания цифровых устройств, функционирующих на уровне регистров. Он имеет простые и наглядные средства описания машинных слов, регистров, шин и других базовых элементов ЭВМ. С учетом сказанного, иерархию языков описания вычислительного процесса на ЭВМ можно представить, в общем случае, на четырех уровнях: (1) булева операция (функционирование комбинационных ЛС) => (2) микрокоманда (функционирование узлов ЭВМ) => (3) команда (функционирование ЭВМ) => (4) оператор ЯВУ (описание алгоритма решаемой задачи). Для определения временных соотношений между микрокомандами устанавливается единица времени (такт), в течение которой выполняется самая продолжительная микрокоманда. Поэтому выполнение одной команды ЭВМ синхроимпульсами, генерируемыми специальным устройством процессора - тактовым генератором, тактовая частота (измеряемая в МГц) в значительной степени определяет быстродействие ЭВМ. Естественно, для других классов ЭВМ данный показатель иным образом связывается с производительностью, определяемой такими дополнительными факторами, как. - ширина доступа в память, - время выборки, - разрядность, - архитектура процессора и его сопроцессоров, Укрупненная схема центрального процессора (ЦП) некоторой формальной ЭВМ представлена на рисунке, где изображены только основные его блоки управляющие регистры (УР), устройство управления (УУ), ПЗУ, арифметико-логическое устройство (АЛУ), регистровая память (РП), кэш-память и интерфейсный блок (ИБ). Наряду с перечисленными ЦП содержит ряд других блоков (прерывания, защиты ОП, контроля и диагностики и др.), структура и назначение которых здесь не рассматриваются. Блок УУ вырабатывает последовательность управляющих сигналов, инициирующих выполнение соответствующей последовательности микрокоманд (находящихся в ПЗУ), реализующей текущую команду. Наряду с этим УУ координирует функционирование всех устройств ЭВМ посредством посылки управляющих сигналов обмен данными ЦП <-> ОП, хранение и обработка информации, интерфейс с пользователем, тестирование и диагностика и др. Поэтому УУ целесообразно рассматривать как отдельный блок ЦП; однако на практике большинство управляющих схем распределены по всей ЭВМ. Они связаны большим числом управляющих линий, передающих сигналы для синхронизации операции во всех устройствах ЭВМ и принимающих сигналы об их состоянии. Блок УР предназначен для временного хранения управляющей информации и содержит регистры и счетчики, участвующие совместно с УУ в управлении вычислительным процессом регистр состояния ЦП, программы (ССП), счетчик команд (СК) представляет собой регистр, хранящий в ОП адрес выполняемой команды (в период выполнения текущей команды его содержимое обновляется на адрес следующей команды), регистр команд (РК) содержит выполняемую команду (его выходы связаны с управляющими схемами, генерирующими распределенные во времени сигналы, необходимые для выполнения команд) Блок РП содержит регистры сверхоперативной памяти (более высокого быстродействия, чем ОП) небольшого объема, позволяющие повысить быстродействие и логические возможности ЦП. Эти регистры используются в командах путем сокращенной регистровой адресации (указываются только номера регистров) и служат для хранения операндов, результатов операций, в качестве базовых и индексных регистров, указателей стэка и др. В некоторых ЦП базовые и индексные регистры входят в состав блока УТ, как правило, РП выполняется в виде быстродействующих полупроводниковых интегральных запоминающих устройств Блок АЛУ служит для выполнения арифметических и логических операций над данными, поступающими из ОП и хранящимися в РП, и работает под управлением УУ. АЛУ выполняет арифметические операции над бинарными числами с фиксированной и плавающей точками, над десятичными числами, производит обработку символьной информации над словами фиксированной и переменной длины. Логические операции производятся над отдельными битами, группами битов, байтами и их последовательностями. Тип выполняемой АЛУ операции определяется текущей командой функционирующей в данный момент программы, точнее, АЛУ служит для выполнения любой операции, задаваемой ему УУ. В общем случае обрабатываемая ЭВМ информация состоит из слов, содержащих фиксированное число n битов (например n =8. 16. 32, 64, 128 бит). В этом случае АЛУ должно иметь возможность производить операции над n-битными словами операнды поступают из ОП на регистры АЛУ, а УУ указывает операцию, которую необходимо над ними произвести, результат каждой арифметико-логической операции сохраняется в специальном регистре-сумматоре, являющимся основным регистром для арифметико-логических операций. Сумматор соединен с вентильными схемами для выполнения необходимых операций над его содержимым и содержимым других регистров. Некоторые ЭВМ имеют несколько сумматоров, при количестве, большем 4, они выделяются в специальную группу регистров общего назначения (РОН). Конструктивно АЛУ выполняется на одном или нескольких БИС/СБИС, при этом ЦП может иметь одно АЛУ универсального назначения или несколько специализированных для отдельных видов операции. В последнем случае увеличивается структурная сложность ЦП, но повышается его быстродействие за счет специализации и упрощения схем вычисления отдельных операций. Такой подход широко используется в современных ЭВМ общего назначения и супер-ЭВМ для повышения их производительности Несмотря на различные классы ЭВМ, их АЛУ используют общие принципы выполнения арифметико-логических операции. Различия касаются схемотехнических решений организации АЛУ и принципов реализации операции, обеспечивающих ускорение их выполнения. Интерфейсный блок (ИБ) обеспечивает обмен информацией ЦП с ОП и защиту участков ОП от несанкционированного для текущей программы доступа, а также связь ЦП с периферийными устройствами и другими внешними по отношению к нему устройствами (ВУ), в качестве которых могут выступать другие процессоры и ЭВМ. В частности, ИБ содержит два регистра, обеспечивающие связь с ОП - регистр адреса памяти (РАП) и регистр данных памяти (РДП). Первый регистр используется для хранения адреса ячейки ОП, с которой производится обмен данными, а второй содержит собственно данные обмена. Блок контроля и диагностики (БКД) предназначен для обнаружения сбоев и отказов узлов ЦП, восстановления работы текущей программы после сбоев и локализации неисправностей при отказах. С учетом сказанного представим общую схему выполнения программ процессором. Выполнение программы, находящейся в ОП, начинается с того, что в СК засылается адрес первой ее команды, содержимое СК пересылается в РАП и в ОП посылается сигнал управления считыванием. Через некоторое время (соответствующее времени доступа к ОП) адресуемое слово (в данном случае первая команда программы) извлекается из ОП и загружается в РДП, затем содержимое РДП пересылается в СК. На этой стадии команда готова для декодирования ее УУ и выполнения. Если команда содержит операцию, которая должна быть выполнена АЛУ, то необходимо получить требуемые операнды. Если операнд находится в ОП (а он может быть также в УР), его необходимо выбрать из памяти. Для этого в РАП пересылается адрес операнда и начинается цикл чтения Операнд, выбранный из памяти в РДП, может быть передан в АЛУ. Выбрав таким образом один или несколько операндов, АЛУ может выполнить требуемую операцию, сохранив ее результат в одном из РОН. Если результат операции необходимо запомнить в ОП, он должен быть послан в РДП Адрес ячейки, в которую необходимо поместить результат, пересылается в РАП и начинается цикл записи. Между тем содержимое СК увеличивается, указывая следующую команду, которая должна выполняться. Таким образом, как только завершится выполнение текущей команды, может сразу же начаться выборка на выполнение следующей команды программы. Помимо передачи данных между ОП и ЦП необходимо обеспечить обмен данными с ВУ, что делают машинные команды, управляющие вводом/выводом. Естественный порядок выполнения программ может нарушаться при поступлении сигнала прерывания. Прерывание является требованием на обслуживание, которое осуществляется ЦП, выполняющим соответствующую программу обработки прерывания (ПОП). Так как прерывание и его обработка могут изменить внутреннее состояние ЦП, то оно сохраняется в ОП перед началом работы ПОП. Сохранение состояния достигается пересылкой содержимого РК, УР и некоторой управляющей информации в ОП. После завершения ПОП состояние ЦП восстанавливается, позволяя продолжить выполнение прерванной программы. |