Архитектура ЭВМ и систем (конспект лекций). Конспект лекций

Скачать 1.1 Mb. Скачать 1.1 Mb.

|

Способы задания операндов командыВ ходе предыдущего изложения мы поневоле касались вопроса о том, где располагаются операнды, с которыми работает машинная команда, и как это отражается на содержимом ее полей. В этой части занятия мы рассмотрим этот вопрос более систематизировано и в полном объеме. Это позволит нам уже со следующего занятия перейти непосредственно к практическим вопросам программирования на языке ассемблера. Операнд задается неявно на микропрограммном уровне. В этом случае команда явно не содержит операндов. Алгоритм выполнения команды использует некоторые объекты по умолчанию (регистры, флаги в eflags и т. д.). Например, команды cli и sti неявно работают с флагом прерывания if в регистре eflags, а команда xlat неявно обращается к регистру al и строке в памяти по адресу, определяемому парой регистров ds:bx. Операнд задается в самой команде (непосредственный операнд). Операнд находится в коде команды, то есть является ее частью. Для хранения такого операнда в команде выделяется поле длиной до 32 бит (см. рис. 1). Непосредственный операнд может быть только вторым операндом (источником). Операнд получатель может находиться либо в памяти, либо в регистре. Например: mov ax,0ffffh пересылает в регистр ax шестнадцатеричную константу ffff. Команда add sum,2 складывает содержимое поля по адресу sum с целым числом 2 и записывает результат по месту первого операнда, то есть в память. Операнд находится в одном из регистров. Регистровые операнды указываются именами регистров. В качестве регистров могут использоваться:

Например, команда add ax,bx складывает содержимое регистров ax и bx и записывает результат в bx. Команда dec si уменьшает содержимое si на 1. Операнд располагается в памяти. Это наиболее сложный и в то жe время наиболее гибкий способ задания операндов. Он позволяет реализовать следующие два основных вида адресации: прямую и косвенную. В свою очередь, косвенная адресация имеет следующие разновидности:

Операндом является порт ввода/вывода. Как мы уже отмечали, помимо адресного пространства оперативной памяти микропроцессор поддерживает адресное пространство ввода-вывода, которое используется для доступа к устройствам ввода-вывода. Объем адресного пространства ввода-вывода составляет 64 Кбайт. Для любого устройства компьютера в этом пространстве выделяются адреса. Конкретное значение адреса в пределах этого пространства называется портом ввода-вывода. Физически порту ввода-вывода соответствует аппаратный регистр (не путать с регистром микропроцессора), доступ к которому осуществляется с помощью специальных команд ассемблера in и out. Например, in al,60h ;ввести байт из порта 60h Регистры, адресуемые с помощью порта ввода-вывода, могут иметь разрядность 8, 16 или 32 бит, но для конкретного порта разрядность регистра фиксирована. Команды in и out работают с фиксированной номенклатурой объектов. В качестве источника информации или получателя применяются так называемые регистры-аккумуляторы eax, ax, al. Выбор регистра определяется разрядностью порта. Номер порта может задаваться непосредственным операндом в командах in и out или значением в регистре dx. Последний способ позволяет динамически определить номер порта в программе. Например: mov dx,20h ;записать номер порта 20h в регистр dx mov al,20h ;записать значение 20h в регистр al out dx,al ;вывести значение 20h в порт 20H Операнд находится в стеке. Команды могут совсем не иметь операндов, иметь один или два операнда. Большинство команд требуют двух операндов, один из которых является операндом-источником, а второй - операндом назначения. Важно то, что один операнд может располагаться в регистре или памяти, а второй операнд обязательно должен находиться в регистре или непосредственно в команде. Непосредственный операнд может быть только операндом-источником. В двухоперандной машинной команде возможны следующие сочетания операндов:

У данного правила есть исключения, которые касаются:

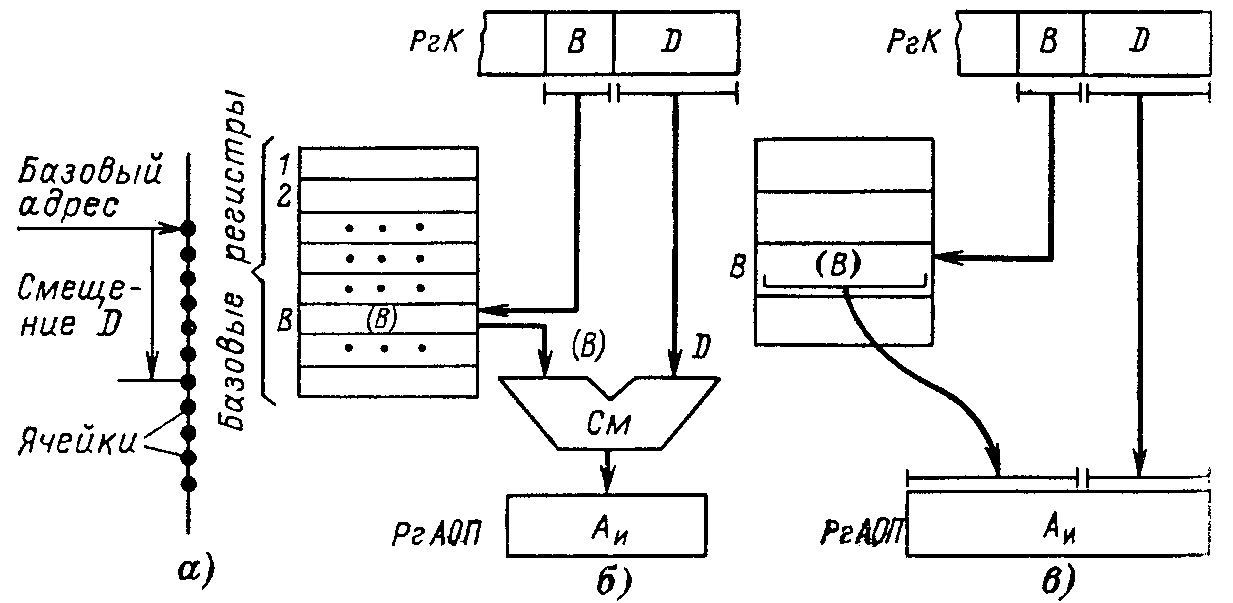

Из перечисленных сочетаний операндов наиболее часто употребляются регистр-память и память-регистр. Ввиду их важности рассмотрим их подробнее. Обсуждение мы будем сопровождать примерами команд ассемблера, которые будут показывать, как изменяется формат команды ассемблера при применении того или иного вида адресации. В связи с этим посмотрите еще раз на рис. 2, на котором показан принцип формирования физического адреса на адресной шине микропроцессора. Видно, что адрес операнда формируется как сумма двух составляющих - сдвинутого на 4 бит содержимого сегментного регистра и 16-битного эффективного адреса, который в общем случае вычисляется как сумма трех компонентов: базы, смещения и индекса. Перечислим и затем рассмотрим особенности основных видов адресации операндов в памяти:

Прямая адресацияЭто простейший вид адресации операнда в памяти, так как эффективный адрес содержится в самой команде и для его формирования не используется никаких дополнительных источников или регистров. Эффективный адрес берется непосредственно из поля смещения машинной команды (см. рис. 1), которое может иметь размер 8, 16, 32 бит. Это значение однозначно определяет байт, слово или двойное слово, расположенные в сегменте данных. Прямая адресация может быть двух типов:

jс m1 ;переход на метку m1, если флаг cf = 1 mov al,2 ... m1:

mov ax,dword ptr [0000] ;записать слово по адресу ;ds:0000 в регистр ax

data segment per1 dw 5 ... data ends code segment mov ax,data mov ds,ax ... mov ax,per1 ;записать слово per1 (его физический адрес ds:0000) в ax

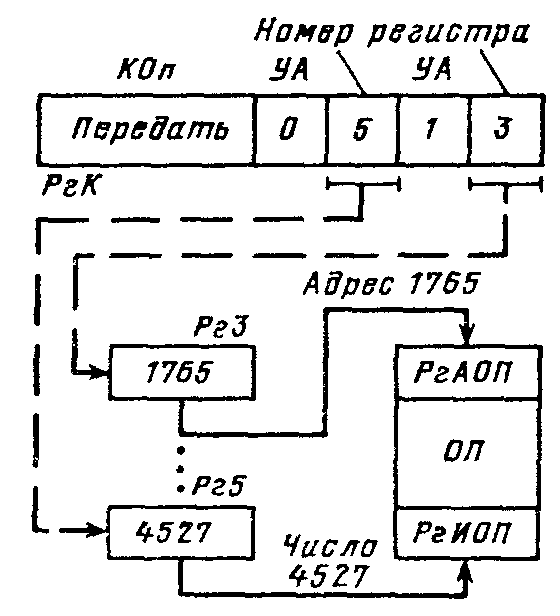

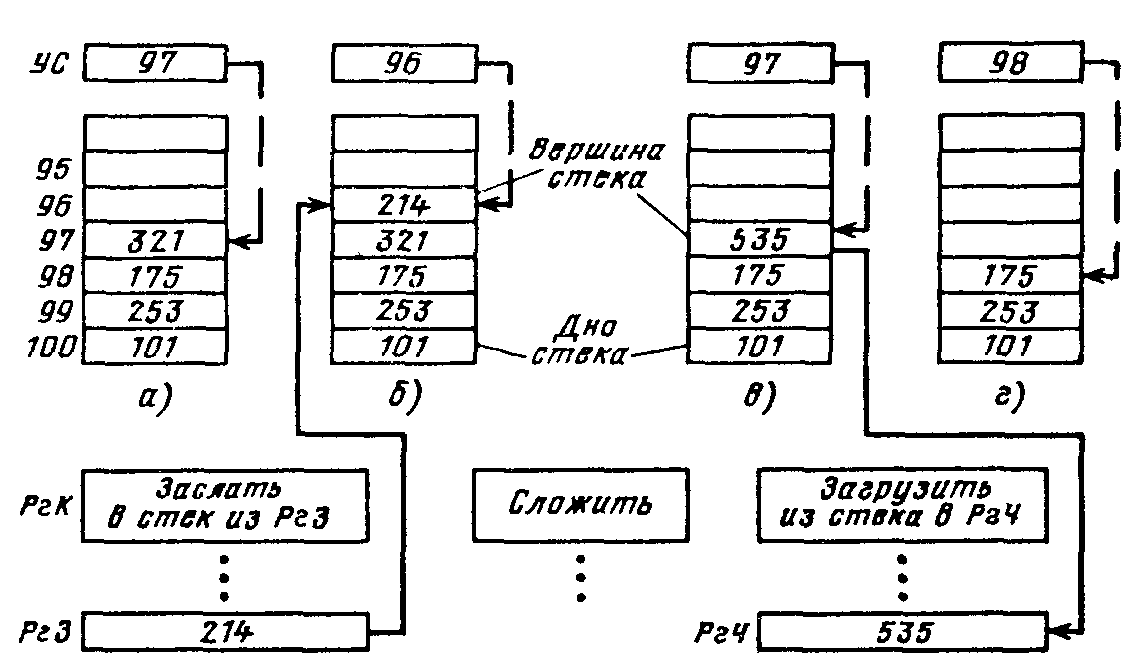

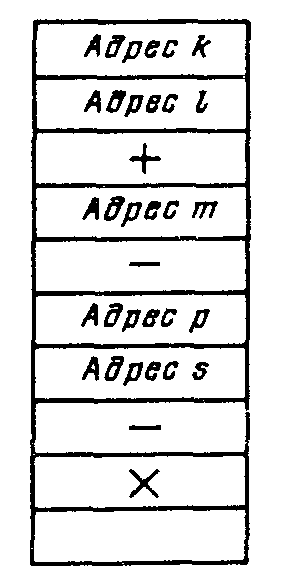

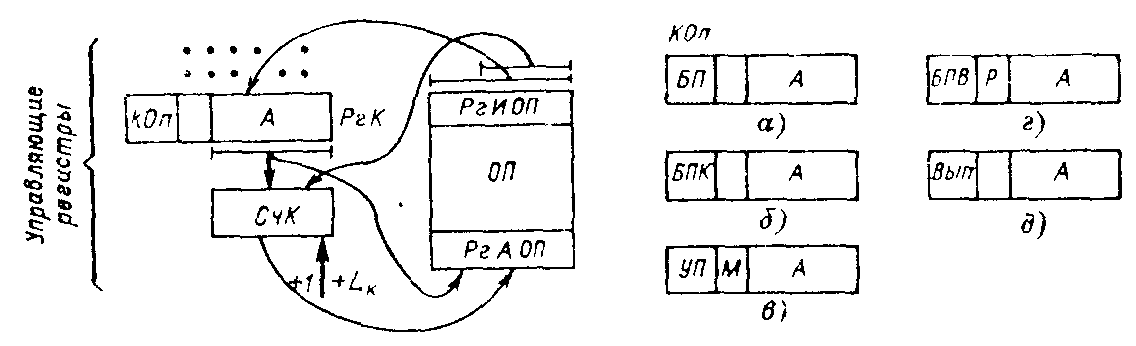

Остальные виды адресации относятся к косвенным. Слово "косвенный" в названии этих видов адресации означает то, что в самой команде может находиться лишь часть эффективного адреса, а остальные его компоненты находятся в регистрах, на которые указывают своим содержимым байт modr/m и, возможно, байт sib. Косвенная базовая (регистровая) адресацияПри такой адресации эффективный адрес операнда может находиться в любом из регистров общего назначения, кроме sp/esp и bp/ebp (это специфические регистры для работы с сегментом стека). Синтаксически в команде этот режим адресации выражается заключением имени регистра в квадратные скобки [ ]. К примеру, команда mov ax,[ecx] помещает в регистр ax содержимое слова по адресу из сегмента данных со смещением, хранящимся в регистре ecx. Так как содержимое регистра легко изменить в ходе работы программы, данный способ адресации позволяет динамически назначить адрес операнда для некоторой машинной команды. Это свойство очень полезно, например, для организации циклических вычислений и для работы с различными структурами данных типа таблиц или массивов. Косвенная базовая (регистровая) адресация со смещениемЭтот вид адресации является дополнением предыдущего и предназначен для доступа к данным с известным смещением относительно некоторого базового адреса. Этот вид адресации удобно использовать для доступа к элементам структур данных, когда смещение элементов известно заранее, на стадии разработки программы, а базовый (начальный) адрес структуры должен вычисляться динамически, на стадии выполнения программы. Модификация содержимого базового регистра позволяет обратиться к одноименным элементам различных экземпляров однотипных структур данных. К примеру, команда mov ax,[edx+3h] пересылает в регистр ax слова из области памяти по адресу: содержимое edx + 3h. Команда mov ax,mas[dx] пересылает в регистр ax слово по адресу: содержимое dx плюс значение идентификатора mas (не забывайте, что транслятор присваивает каждому идентификатору значение, равное смещению этого идентификатора относительно начала сегмента данных). Косвенная индексная адресация со смещениемЭтот вид адресации очень похож на косвенную базовую адресацию со смещением. Здесь также для формирования эффективного адреса используется один из регистров общего назначения. Но индексная адресация обладает одной интересной особенностью, которая очень удобна для работы с массивами. Она связана с возможностью так называемого масштабирования содержимого индексного регистра. Что это такое? Посмотрите на рис. 1. Нас интересует байт sib. При обсуждении структуры этого байта мы отмечали, что он состоит из трех полей. Одно из этих полей - поле масштаба ss, на значение которого умножается содержимое индексного регистра. К примеру, в команде mov ax,mas[si*2] значение эффективного адреса второго операнда вычисляется выражением mas+(si)*2. В связи с тем, что в ассемблере нет средств для организации индексации массивов, то программисту своими силами приходится ее организовывать. Наличие возможности масштабирования существенно помогает в решении этой проблемы, но при условии, что размер элементов массива составляет 1, 2, 4 или 8 байт. Косвенная базовая индексная адресацияПри этом виде адресации эффективный адрес формируется как сумма содержимого двух регистров общего назначения: базового и индексного. В качестве этих регистров могут применяться любые регистры общего назначения, при этом часто используется масштабирование содержимого индексного регистра. Например: mov eax,[esi][edx] В данном примере эффективный адрес второго операнда формируется из двух компонентов (esi)+(edx). Косвенная базовая индексная адресация со смещениемЭтот вид адресации является дополнением косвенной индексной адресации. Эффективный адрес формируется как сумма трех составляющих: cодержимого базового регистра, cодержимого индексного регистра и значения поля смещения в команде. К примеру, команда mov eax,[esi+5][edx] пересылает в регистр eax двойное слово по адресу: (esi) + 5 + (edx). Команда add ax,array[esi][ebx] производит сложение содержимого регистра ax с содержимым слова по адресу: значение идентификатора array + (esi) + (ebx). 9.5. Способы адресации Следует различать понятия адресный код в команде АК и исполнительный адрес АИ. Адресный код - это информация об адресе операнда, содержащаяся в команде. Исполнительный адрес - это номер ячейки памяти, к которой производится фактическое обращение. В современных ЭВМ адресный код, как правило, не совпадает с исполнительным адресом. Выбор способов адресации, формирования исполнительного адреса и преобразования адресов является одним из важнейших вопросов разработки ЭВМ. Рассмотрим способы адресации, используемые в современных ЭВМ. Подразумеваемый операнд. В команде не содержится явных указаний об адресе операнда; операнд подразумевается и фактически задается кодом операции команды. Данный способ используется не часто, однако имеется несколько важных случаев его применения. В качестве примера можно привести команды подсчета, в которых к некоторому числу, (содержимому счетчика) прибавляется фиксированное приращение, чаще единица младшею разряда. Один из операндов - число в счетчике - обычно адресуется явным методом, второй операнд - приращение - не адресуется, в памяти машины не содержится и является подразумеваемым. Подразумеваемый адрес. В команде не содержится явных указаний об адресе участвующего в операции операнда или адреса, по которому помещается результат операции, но этот адрес подразумевается. Например, команда может содержать адреса обоих операндов, участвующих в операции, при этом подразумевается, что результат операции помещается по адресу одного из операндов, или команда указывает только адрес одного операнда, а адрес второго, которым является содержимое специального регистра (называемого регистром результата или аккумулятором), подразумевается. Непосредственная адресации. В команде содержится не адрес операнда, а непосредственно сам операнд. При непосредственной адресации не требуется обращения к памяти для выборки операнда и ячейки для его хранения Это способствует уменьшению времени выполнения программы и занимаемого ею объема памяти. Непосредственная адресация удобна для хранения различного рода констант, однако следует иметь в виду, что при этом способе адресации длина операнда короче кода команды, поскольку часть разрядов команды занята под код операции. Прямая адресация. Исполнительный адрес совпадает с адресной частью команды. Этот способ адресации был общепринятым в первых вычислительных машинах и продолжает применяться в настоящее время в комбинации с другими способами. В указанной форме непосредственная адресация реализуется в ЭВМ со сравнительно длинным машинным словом (32 разряда и более). Относительная адресация или базирование. Исполнительный адрес определяется суммой адресного кода команды АК и некоторого числа AБ, называемого базовым адресом: АИ = АК + АБ. Для хранения базовых адресов в машине могут быть предусмотрены регистры или специально выделенные для этой цели ячейки памяти (базовые регистры). В команде выделяется поле В для указания номера базового регистра. Относительная адресация позволяет при меньшей длине адресного кода команды обеспечить доступ к любой ячейке памяти. Для этого число разрядов в базовом адресе выбирают таким, чтобы можно было адресовать любую ячейку ОП, а адресный код АК, самой команды используют для представления лишь сравнительно короткого «смещения» (обозначают буквой D). Смещение D определяет положение операнда относительно начала массива, задаваемого базовым адресом АБ. Рисунок 3.5 поясняет процесс формирования исполнительного адреса. Большей частью исполнительный адрес при базировании образуется с помощью сумматора согласно выражению (рис. 3.5)  г  Рис. 3.5. Базирование (относительная адресация): а - образование адреса элемента одномерного массива; б - формирование исполнительного адреса суммированием; в - формирование исполнительного адреса совмещением де В и D - коды (числа), стоящие в соответствующих полях команды: (В) -содержимое регистра с номером В. При В = 0 относительная адресация блокируется. Более подробно обращение к ОП при относительной адресации можно представить в следующем виде: если РгК[В] = 0 то РгАОП := РгК[0] иначе РгАОП := РгB + РгК[D]; Счит: РгИОП := ОП [РгАОП}: Суммирование при образовании АИ связано с потерей времени. Поэтому применяют также формирование исполнительного адреса методом совмещения (рис. 3.5,в). В этом случае базовый адрес содержит старшие, а смещение - младшие разряды исполнительного адреса, которые объединяются в РгАОП согласно операции конкатенации слова: РгАОП := РгВ|РгК[D]; Однако при совмещении базовый адрес может задавать не любую ячейку, а только те ячейки, адреса которых содержат 0 в младших разрядах, соответствующих смещению. Относительная адресация обеспечивает так называемую перемещаемость программ, т. е. возможность передвижения программ в памяти без изменений внутри самой программы. Укороченная адресация. Для уменьшения длины кода команды часто применяется так называемая укороченная адресация. Суть ее сводится к тому, что в команде задаются только младшие разряды адресов, старшие разряды при этом подразумеваются нулевыми. Такая адресация позволяет использовать только небольшую группу фиксированных ячеек с начальными (короткими) адресами и поэтому может применяться лишь совместно с другими способами адресации. Регистровая адресация есть частный случай укороченной, когда в качестве фиксированных ячеек с короткими адресами используются регистры (ячейки сверхоперативной или местной памяти) процессора. Например, если таких регистров 16, то для адреса достаточно четырех двоичных разрядов. Регистровая адресация наряду с сокращением длины адресов операндов позволяет увеличить скорость выполнения операций, так как уменьшается число обращений к ОП. Косвенная адресация. Адресный код команды указывает адрес ячейки памяти, в которой находится адрес операнда или команды. Таким образом, косвенная адресация может быть иначе определена как «адресация адреса». На косвенную адресацию указывает код операции команды, а в некоторых ЭВМ в команде отводится специальный разряд (указатель адресации - УА), и цифра 0 или 1 в нем указывает, является адресная часть команды прямым адресом или косвенным. Обращение к ОП за операндом при косвенной адресации представляет собой следующую процедуру: РгАОП := РгК [А]; Счит: РгИОП := ОП[РгАОП]; если УА=0 то идти к М иначе РгАОП := РгИОП; Счит: РгИОП := ОП [РгАОП]; М: РгАЛУ := РгИОП; В некоторых ЭВМ используется многоступенчатая косвенная адресация. В этом случае ячейки памяти содержат также разряд-указатель косвенной адресации (УА). Если этот разряд указывает на продолжение косвенной адресации, то машина последовательно выбирает из памяти адреса до тех пор, пока не будет найдена ячейка, в которой разряд-указатель определит прямую адресацию. Адрес из этой последней ячейки и является искомым исполнительным адресом. Косвенная адресация широко используется в малых и микроЭВМ, имеющих короткое машинное слово, для преодоления ограничений короткого формата команды. Р  Рис. 3.6 Совместное использование регистровой прямой и регистровой косвенной адресации для преодоления ограничений короткого слова команды. ассмотрим широко применяемое в микропроцессорах, малых и микроЭВМ совместное использование укороченной (регистровой) и косвенной адресаций (рис.3.6). Пусть необходимо передать число 4527 из Рг5 в ячейку ОП 1765. Длина адресных полей команды достаточна лишь для указания коротких номеров регистров, она не позволяет задать в команде полный адрес ячейки памяти. Поэтому операнд 4527 указывается регистровой косвенной адресацией (УА=0), а для задания адреса 1765 приходится воспользоваться регистровой косвенной адресацией (УА=1), при которой в команде указывается номер регистра (в рассматриваемом примере РгЗ), предварительно загруженного полным адресом ячейки, в которою производится передача. Автоинкрементная и автодекрементная адресации. Поскольку регистровая косвенная адресация требует предварительной загрузки регистра из ОП косвенным адресом, что связано с потерей времени, такой тип адресации особенно эффективен при обработке массива данных, если имеется механизм автоматического приращения или уменьшения содержимого регистра при каждом обращении к нему, называемый соответственно авто инкрементной и автодекрементной адресацией. В этом случае достаточно 1 раз загрузить в регистр адрес первого обрабатываемого элемента массива, а затем при каждом обращении к регистру в нем в результате инкрементной (декрементной) процедуры формируется адрес следующего элемента массива. При автоинкрементной адресации по содержимому регистра сначала содержимое регистра используется как адрес операнда, а затем получает приращение, равное числу байт в элементе массива. При автодекрементной адресации сначала содержимое указанного в команде регистра уменьшается на число, равное числу байт в элементе массива, а затем используется как адрес операнда. Автоинкрементная и автодекрементная адресации могут рассматриваться как упрощенный вариант индексации - весьма важного механизма преобразования адресных частей команд и организации вычислительных циклов, поэтому их часто называют автоиндексацией. Адресация слов переменной длины. Эффективность вычислительных систем, предназначенных для обработки данных (экономических, плановых и др.), повышается, если имеется возможность выполнять операции со словами переменной длины. В этом случае в машине должна быть предусмотрена адресация слов переменной длины, которая обычно реализуется путем указания в команде местоположения в памяти начала слова и его длины. Обычно в ЭВМ одновременно используется несколько типов адресации Тип адресации указывается либо неявно кодом операции, либо в явной форме в специальном поле адресной части команды. 3.6. Стековая адресация Стековая память, реализующая безадресное задание операндов, является эффективным элементом современной архитектуры ЭВМ, особенно широко используемым в микропроцессорах, малых и микроЭВМ, а также в некоторых суперЭВМ. Учитывая своеобразие стековой адресации, ее рассмотрение выделено в отдельный параграф. Стек представляет собой группу последовательно пронумерованных регистров (аппаратурный стек) или ячеек памяти, снабженных указателем стека (обычно регистром) (УС), в котором автоматически при записи и считывании устанавливается номер (адрес) последней занятой ячейки стека (вершины стека}. При операции записи заносимое в стек слово помещается в следующую по порядку свободную ячейку стека, а при считывании из стека извлекается последнее поступившее в него слово. Таким образом, в стеке реализуется правило «последний пришел - первый ушел». Указанное правило при обращении к стеку реализуется автоматически, и поэтому при операциях со стеком возможно безадресное задание операнда — команда не содержит адреса ячейки стека, но содержит адрес (или он подразумевается) ячейки памяти или регистра, откуда слово передается в стек или куда помещается из стека. Механизм стековой адресации поясняется на рис.3.7. При выполнении команды передачи в стек слова из регистра или ячейки ОП сначала указатель стека увеличивается на 1 (в перевернутом стеке уменьшается на 1), а затем слово помещается в ячейку стека, указываемую УС. При команде загрузки из стека регистра или ячейки памяти сначала слово извлекается из вершины стека, а затем указатель стека уменьшается на 1 (в перевернутом стеке увеличивается на 1). Как это ни кажется на первый взгляд удивительным, но при соответствующем расположении операндов в стеке можно вычислять выражения полностью безадресными командами, указывающими только вид операции. Такая команда извлекает из стека в соответствии с кодом операции один или два операнда, выполняет над ними предписанную операцию и заносит результат в стек. В  Рис 9.7 Стековая адресация в «перевернутом стеке»: а - исходное состояние стека; б - стек после выполнения команды «Заслать в стек из РгЗ»; в - стек после выполнения команды «Сложить», г — стек после выполнения команды «Загрузить из стека в Рг4» ычисления с использованием стековой памяти удобно описывать и программировать с помощью польской инверсной (бес скобочной) записи арифметических выражений ПОЛИЗ. Эта запись производится по следующему правилу: читаем арифметическое выражение слева направо и последовательно друг за другом выписываем встречающиеся операнды. Как только окажется, что все операнды некоторой операции выписаны, записываем знак этой операции и продолжаем выписывать операнды. Если операция имеет операндом результат некоторой предыдущей операции и знак последней выписан, то считаем этот операнд выписанным. Например, выражение (k + l - m) (p - s) в  Рис. 3.8. Программа вычисления выражения с использованием стековой памяти ПОЛИЗ имеет вид k l + m – p s - *. Выражение в ПОЛИЗ не содержит скобок, но порядок действий определяет однозначно. При использовании стековой памяти последовательность символов в выражении ПОЛИЗ, может рассматриваться как программа вычисления исходного арифметического выражения (рис. 3.8), если под буквами понимать команды засылки, содержащие только адреса в ОП соответствующих операндов, засылаемых в стек, а под знаками операции безадресные команды, содержащие только коды операций. Команда второго типа инициирует извлечение из стека двух (или одного) слов, выполнение над ними указанной в команде операции и засылку результата в вершину стека Безадресные команды на основе стековой адресации предельно сокращают формат команд, экономят память и способствуют повышению производительности ЭВМ. Однако при такой структуре команд возникают осложнения с построением команд передачи управления и работы с периферийными устройствами. В современной архитектуре процессоров и микропроцессоров стек и стековая адресация широко ИСПОЛЬЗУЮТСЯ при организации переходов к подпрограммам и возврате от них, а также в системах прерывания. Весьма широко стеки и безадресные команды используются в вычислительном комплексе «Эльбрус». 9.7. Команды, процедуры и микропрограммы передачи управления в программах Рассмотрим команды, управляющие порядком исполнения команд. При естественном порядке после выполнения очередной команды выбирается команда, расположенная в следующей по порядку ячейке памяти. Обычно адрес команд хранится в специальном регистре, называемом счетчиком команды (СчК), содержимое которого после выполнения каждой команды автоматически увеличивается на 1, а если память имеет побайтную адресацию, то оно увеличивается на столько, сколько байт содержит текущая команда (приращение адреса команды LК). Выборка очередной и формирование адреса следующей команды (АСК), часто называемого «продвинутым адресом», происходит (при естественном порядке) следующим образом (рис. 9.9):

РгАОП := СчК; Счит: РгИОП := ОП[РгАОП]; РгК := РгИОП; . . . . . . . . . . . . . (Выполнение текущей команды) . . . . . . . . . . . . . АСКЕП: СчК := СчК + LК; Естественный порядок выполнения команд может быть нарушен: 1) командами перехода (командами передачи управления); 2) командами замещения (Выполнение); 3) сменой состояния программы; 4) запросами прерывания программы. Команды перехода (передачи управление). Известны многочисленные варианты команд перехода, однако общий принцип состоит в том, что адресная часть команды перехода непосредственно или после суммирования с содержимым базового регистра передается в счетчик команд, и, следовательно, после данной команды может быть выполнена команда из произвольной ячейки памяти, номер которой определяется адресной частью команды перехода. Для упрощения изложения материала рассмотрим процедуры выполнения команд переходов без относительной адресации. Различают два основных вида команд перехода: безусловный переход (БП) и условный (УП). Упрощенные структуры этих команд показаны на рис. 3.10. Команда БП (рис. 3.10, а) совершает переход всегда независимо от каких-либо условий. Обыкновенно следующей за командой БП выполняется команда, адрес которой указан в адресной части команды БП, т. е. АСКЕП : СчК := РгК [А}; Другим вариантом команды БП является безусловный переход по косвенному адресу (БПК) (рис. 3.10,б). На косвенную адресацию указывает код операции команды или специальное поле в формате команды, определяющее тип адресации. Управление передается команде, расположенной в ячейке, адрес которой указан в адресной части команды БПК. В этом случае выполняется следующая процедура: РгАОП := РгК[А]; Счит : РгИОП := ОП[РгАОП]; АСКБПК: СчК := РгИОП[А]; При условном переходе адрес следующем команды зависит от выполнения некоторого условия. Обычно, если условие выполняется, происходит переход к команде по адреса, указанному в адресной части команды УП. В противном случае выбирается следующая по порядку команда, адрес которой определяется, как обычно, содержимым СчК, увеличенным на приращение адреса команды LК. Так же как и при БП, в команде УП могут использоваться относительная и косвенная адресации. Условия перехода (например, результат предыдущей команды равен, больше или меньше 0, переполнение разрядной сетки и др.) задаются кодом операции УП или в виде отдельного поля маска условия М в команде УП (рис. 3.10, в). В этом случае следующая команда определяется по правилу если Ус [М] = 1 то АСКУП : СчК := РгК [А] иначе АСКЕП : СчК := СчК + LК; Здесь Ус[М] —логическая функция (условие), заданная маской М. Если условие перехода задается кодом операции команды, то в приведенном выражении Ус[М] надо заменить на Ус[К0п]. Обычно выполнение машинной команды сопровождается выработкой кода признака результата ПР, формируемого в специальном регистре РгПР. Команда УП анализирует сформированный предыдущей командой ПР. Смысл кодов ПP может быть установлен различным для разных операций. Например, в ЕС ЭВМ двухразрядный признак результата ПР при выполнении арифметических операций принимает значения, приведенные в табл. 3.1 (ПР[0] и ПР[1] — нулевой и первый разряды ПР). С помощью двухразрядной маски можно задать в качестве условия УП любое значение ПР. Таблица 9.1

| |||||||||||||||||||||||||||||||||||||||||||