ЭССОИ_КР_1_вар_3. Контрольная работа 1 по дисциплине Электронные средства сбора, обработки промышленной и деловой информации учебное пособие В. Л. Савчук Электронные средства сбора, обработки промышленной и деловой информации Часть 1

Скачать 1.23 Mb. Скачать 1.23 Mb.

|

|

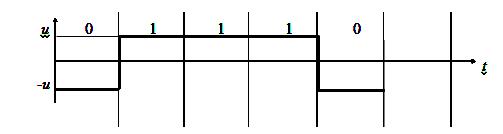

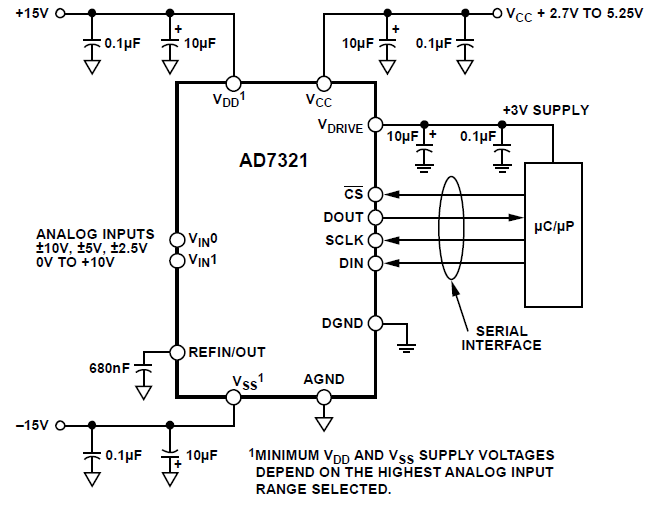

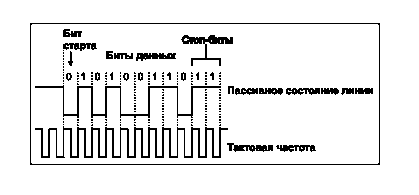

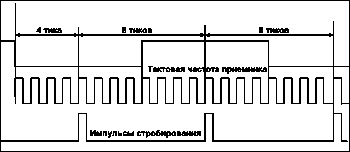

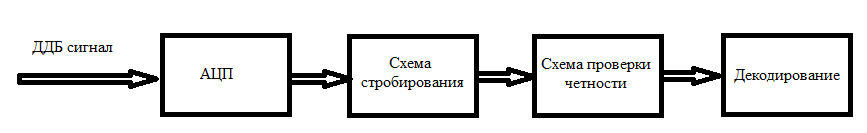

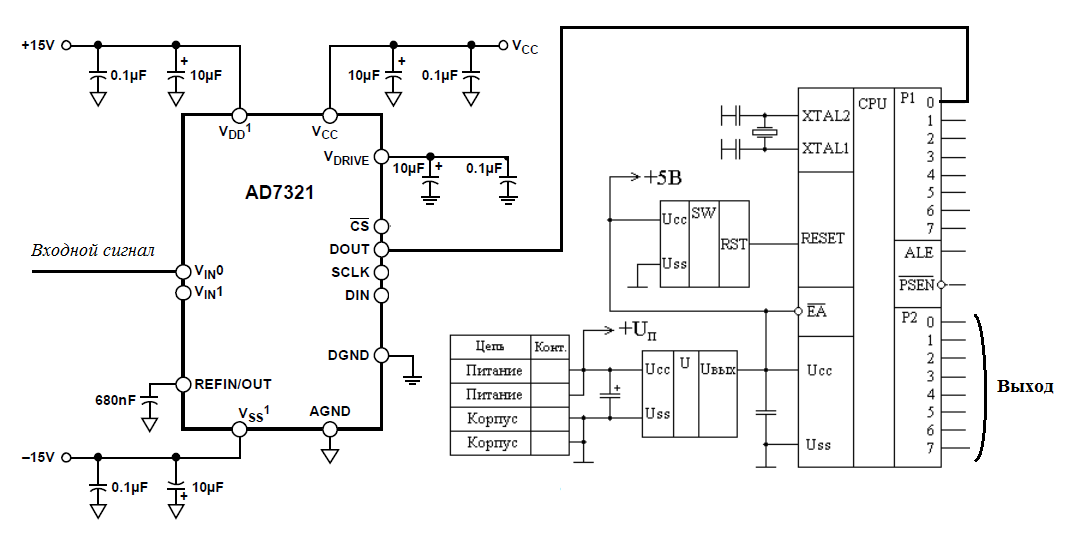

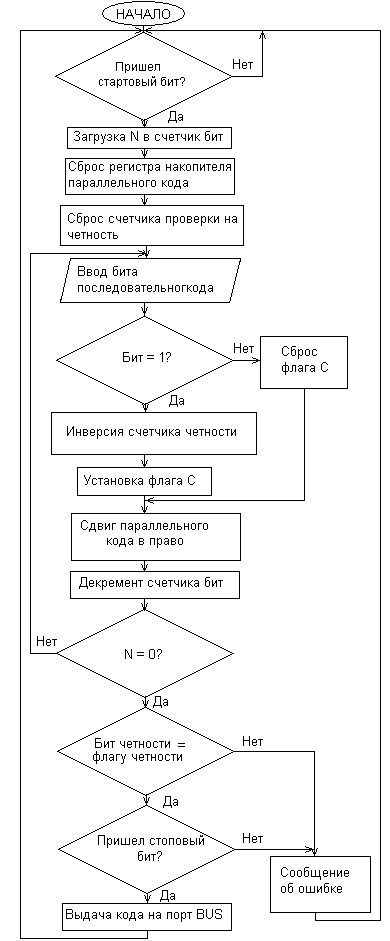

Томский межвузовский центр дистанционного образования Томский государственный университет систем управления и радиоэлектроники (ТУСУР) Кафедра промышленной электроники (ПрЭ) Контрольная работа №1 по дисциплине «Электронные средства сбора, обработки промышленной и деловой информации » учебное пособие В. Л. Савчук «Электронные средства сбора, обработки промышленной и деловой информации Часть 1» учебное методическое пособие В. Л. Савчук «Электронные средства сбора, обработки промышленной и деловой информации» Выполнил студент гр. специальности 210106 9 мая 2012 г. г. Задание Разработать декодер двуполярного двоичного беспаузного сигнала с проверкой на четность. Формат информационной части кода 8 бит. Режим асинхронный с одним стартовым и стоповым битом. Выполнение Рассмотрим основные пункты задания и определимся со способом решения поставленной задачи. Для преобразования двуполярного беспаузного аналогового сигнала в цифровой можно использовать аналогово-цифровые преобразователи кода АЦП.  Рисунок 1 – Двуполярный беспаузный сигнал. Для того, чтобы сформировать 1 кадр данных потребуется в нашем случае 11 бит данных в каждом кадре: 1 старт-бит + 8 информационных + 1 бит четности + 1 стоп бит, следовательно, необходим как минимум двенадцатиразрядный АЦП. Выберем в качестве микросхемы АЦП микросхему AD7321 ,которая имеет широкий диапазон входных аналоговых сигналов.  Рисунок 2 – Схема типичного подключения АЦП Типичный кадр данных в асинхронном канале начинается со стартового бита, за которым следует 8 битов данных. Завершается такой кадр одним или двумя стоп-битами (в нашем случае одним). Стартовый бит имеет полярность противоположную пассивному состоянию линии и переводит приемник в активное состояние. Пример передачи такого кадра показан на рис. 1.  Рис. 3. Пример передачи кадра в асинхронном режиме Одним из способов обеспечения надежной синхронизации является применение в приемнике частоты, например, в 8 раз больше частоты следования данных. При этом стробирование данных может производиться примерно в середине сигнала бита (см. рис. 2).  Рис. 4 - Схема синхронизации и стробирования с 8-кратной тактовой частотой приемника Общую структурную схему можно изобразить как:  Рисунок 5 – Структурная схема декодирования сигнала Итак, поскольку задача декодирования заданного сигнала комплексная и достаточно сложная, то в нашем случае задачу удобнее решить аппаратно-программным способом с использованием микроконтроллера. Также для реализации данной задачи достаточно использовать один из простейших микроконтроллеров, например, МК48 или МК51. Рассмотрим решение задачи на основе микроконтроллера К1816ВЕ48. Схема аппаратной реализации представлена на рисунке 6.  Рисунок 6 – Аппаратная реализация декодера. Разработаем программный алгоритм решения задачи в виде блок-схемы алгоритма (см. рисунок 7). Листинг управляющей программы микроконтроллера представлен в приложении А. Поступающий в микроконтроллер последовательный сигнал на линию порта Р0.0 дешифрируется в параллельный и осуществляется проверка на четность. Если код верен, то он выводится на порт BUS (порт P2 ) микроконтроллера. Счетчик проверки на четность инвертируется с приходом единицы и в результате при совпадении бита четности и счетчика четности код сообщения верен, иначе выдается сообщение об ошибке в виде сигнала на линию порта P1.0. По приходу стопового бита программа “зацикливается” и ожидает прихода следующего стартового бита, иначе выдается сигнал на линию порта P1.1. В данной программе так же применено стробирование сигнала, т. е. При приходе стартового бита осуществляется задержка на пол такта и, если сигнал сохранился, то только в этом случае будет осуществлен выход из цикла и дешифрирование сообщения. Задержка на один и пол такта реализуется с учетом времени на выполнение операторов основной программы. Задержка может формироваться от 80 мкс до 20 мс. Вычисляется: для Т–(Т-35-7.5-17.5), где 35-время выполнения операторов основной программы, 7,5-время выполнения STOP TCNT, 17,5-время выполнения операторов подпрограммы задержки, и для Т/2–(Т/2-25-7.5-17.5), где 25-время выполнения операторов основной программы, 7,5-время выполнения STOP TCNT, 17,5-время выполнения операторов подпрограммы задержки. Времена даны для частоты тактового генератора 6 МГц. Максимальная частота преобразования 12.5 кГц, минимальная 50 Гц.  Рис 7. Блок-схема работы микроконтроллера. Список используемой литературы. Шарапов А.В.Цифровые и микропроцессорные устройства: Учебное пособие. – Томск:-2003. - 166 с. Савчук В.Л. Электронные средства сбора, обработки промышленной и деловой информации: Учебное методическое пособие. – Томск:-1997. – 19 с. Савчук В.Л. Электронные средства сбора, обработки промышленной и деловой информации: Учебное пособие. Часть 1: – Томск:-2002. – 76 с. Представление электрических сигналов в цифровой форме. - [Электронный источник] - http://book.itep.ru/2/22/pres_22.htm Архитектура микроконтроллеров MCS-48. [Электронный ресурс ] - http://digteh.ru/MCS48/MCS_48.php С Т Хвощ, Н Н Варлинский, Е А Попов – Микро процессоры и микроЭВМ в системах автоматического управления. Справочник. Издательство «Машиностроение» 1987 г. Однокристальные микроЭВМ. Справочник. М.: МИКАП, 1994, — 400 с. ПРИЛОЖЕНИЕ А Листинг 1 – Управляющая программа микроконтроллера WAIT: JNT0 WAIT ; ОЖИДАНИЕ СТАРТОВОГО ИМПУЛЬСА CALL DELAYX ; СТРОБИРОВАНИЕ СТАРТОВОГО JNT0 WAIT ; ИМПУЛЬСА MOV R7, #8 ; ЗАГРУЗКА СЧЕТЧИКА БИТОВ CLR A ; ОЧИСТКА АККУМУЛЯТОРА MOV P1, A ; ОЧИСТКА ПОРТА Р1 CLR F0 ; СБРОС СЧЕТЧИКА ЧЕТНОСТИ LOOP: CLR C ; СБРОС ПОСЛЕДОВАТЕЛЬНОГО БИТА CALL DELAYT ; ЗАДЕРЖКА НА ПЕРИОД СИГНАЛА JT0 ROTATE ; ЕСЛИ 0 ТО ПЕРЕХОД CPL F0 ; ИНАЧЕ ИНВЕРСИЯ СЧЕТЧИКА ЧЕТНОСТИ И CPL C ; УСТАНОВКА ФЛАГА ПЕРЕНОСА ROTATE: RRC A ; СДВИГ ВПРАВО ЧЕРЕЗ ПЕРЕНОС DJNZ R7, LOOP ; ЕСЛИ НЕ КОНЕЦ ТО ПОВТОРИТЬ CALL DELAYT ; ЗАДЕРЖКА НА ОДИН ТАКТ JNT0 ODD ; ЕСЛИ БИТ ЧЕТНОСТИ 1 ТО ПЕРЕХОД JF0 ERROR ; ИНАЧЕ ЕСЛИ СЧ. ЧЕТНОСТИ 1 ТО ОШИБКА JMP OUT ; ПЕРЕХОД НА ВЫВОД ODD: CPL F0 ; ЕСЛИ ПОСЛЕ ИНВЕРСИИ СЧЕТЧИК JF0 ERROR ; ЧЕТНОСТИ В 1 ТО ОШИБКА OUT: CALL DELAYT ; ЗАДЕРЖКА НА ТАКТ JT0 ERROR2 ; ЕСЛИ СТАРТОВОГО БИТА НЕТ, ТО ОШИБКА OUTL BUS, A ; ВЫВОД ЧИСЛА НА ПОРТ BUS CALL DELAYT ; ЗАДЕРЖКА НА ТАКТ JMP WAIT ; ЗАЦИКЛИВАНИЕ ERROR: MOV A, #01 ; ВЫВОД НА ЛИНИЮ Р1.1 1 OUTL P1, A ; CALL DELAYT ; CALL DELAYT ; JMP WAIT ; ЗАЦИКЛИВАНИЕ ERROR2: MOV A, #2 ; ВЫВОД НА ЛИНИЮ Р1. OUTL P1, A ; CALL DELAYT ; JMP WAIT ; ЗАЦИКЛИВАНИЕ DELAYX: MOV R6, A ; ПОДПОГРАММА ЗАДЕРЖКИ НА ПОЛ ТАКТА MOV A, #NOT((T/2-25-7.5-17.5)/80-1) ; MOV T, A ; ЗАГРУЗКА ТАЙМЕР СЧЕТЧИКА STRT T ; СТАРТ ТАЙМЕР СЧЕТЧИКА EN TCNTI ; РАЗРЕШЕНИЕ ПРЕРЫВАНИЯ MOV A, R6 ; ВОССТАНОВЛЕНИЕ АККУМУЛЯТОРА RET ; DELAYT: MOV R6, A ; ПОДПРОГРАММА ЗАДЕРЖКИ НА ТАКТ MOV A, #NOT((T-35-7.5-17.5)/80-1) ; MOV T, A ; ЗАГРУЗКА ТАЙМЕР СЧЕТЧИКА STRT T ; СТАРТ ТАЙМЕР СЧЕТЧИКА EN TCNTI ; РАЗРЕШЕНИЕ ПРЕРЫВАНИЯ MOV A, R6 ; ВОССТАНОВЛЕНИЕ АККУМУЛЯТОРА RET ; |