Контрольная работа по дисциплине Аппаратное и программное обеспечение мпс

Скачать 53.45 Kb. Скачать 53.45 Kb.

|

|

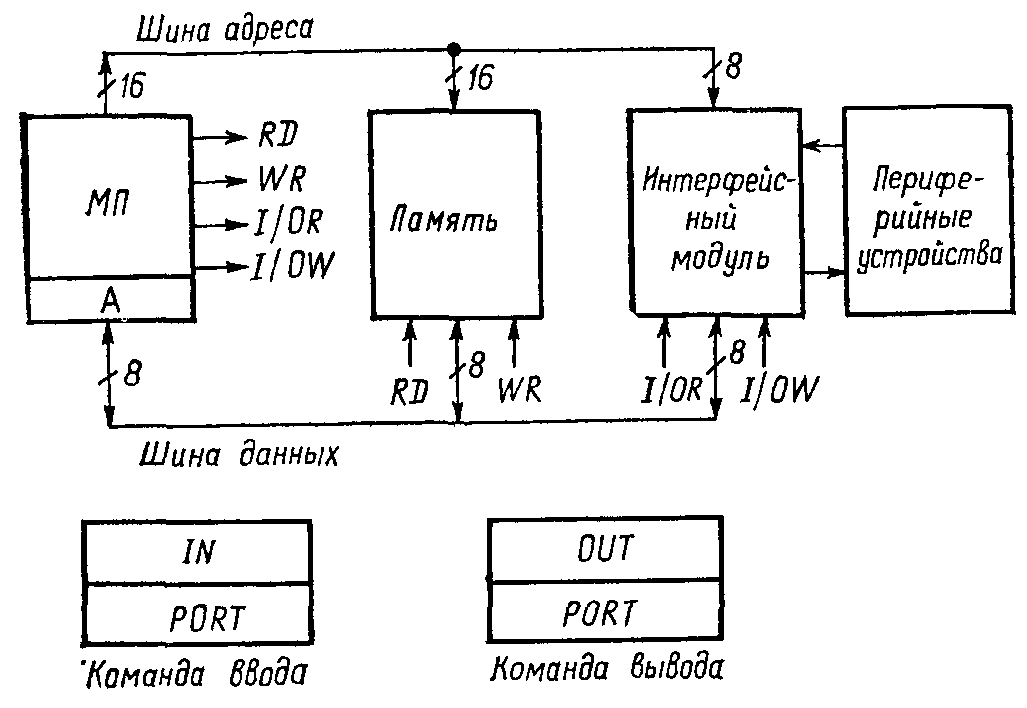

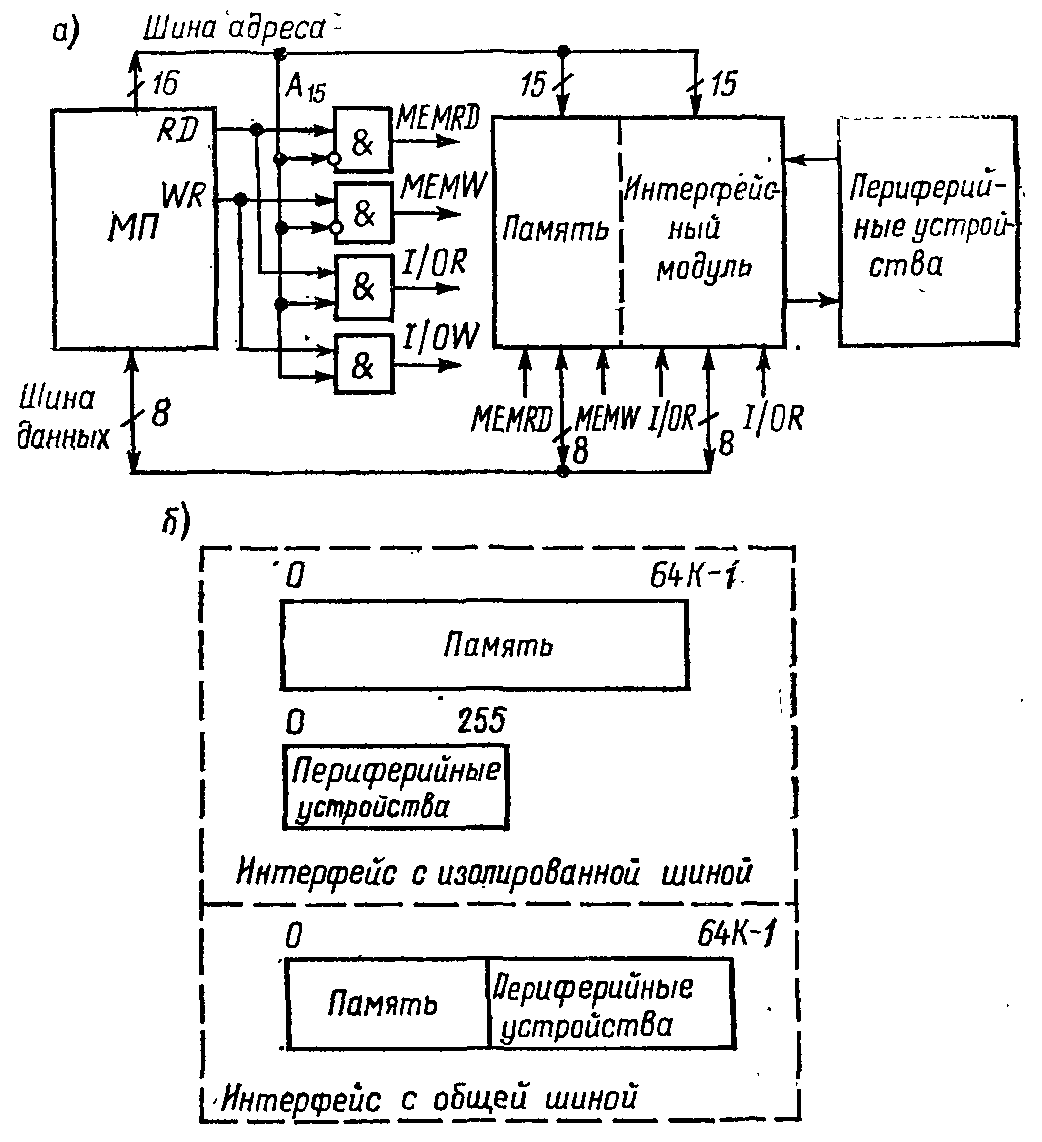

Министерство образования и науки Российской Федерации Федеральное государственное бюджетное образовательное учреждение высшего образования «Ивановский Государственный энергетический университет им. В. И. Ленина» Кафедра электроники и микропроцессорных систем Контрольная работа по дисциплине «Аппаратное и программное обеспечение МПС» Вариант 10 Выполнил: Студент гр. 4- 76 Тихов А. С. шифр 615010 Иваново 2019 Контрольная работа №1 5. Преимущества и недостатки микропроцессорных систем с мультиплексированными и разделёнными шинами адреса данных и управления В системную магистраль (системную шину) микропроцессорной системы входит три основные информационные шины: адреса, данных и управления. Шина данных — это основная шина, ради которой и создается вся система. Количество ее разрядов (линий связи) определяет скорость и эффективность информационного обмена, а также максимально возможное количество команд. Шина данных всегда двунаправленная, так как предполагает передачу информации в обоих направлениях. Наиболее часто встречающийся тип выходного каскада для линий этой шины — выход с тремя состояниями. Обычно шина данных имеет 8, 16, 32 или 64 разряда. Понятно, что за один цикл обмена по 64-разрядной шине может передаваться 8 байт информации, а по 8-разрядной — только один байт. Разрядность шины данных определяет и разрядность всей магистрали. Например, когда говорят о 32-разрядной системной магистрали, подразумевается, что она имеет 32-разрядную шину данных. Шина адреса — вторая по важности шина, которая определяет максимально возможную сложность микропроцессорной системы, то есть допустимый объем памяти и, следовательно, максимально возможный размер программы и максимально возможный объем запоминаемых данных. Количество адресов, обеспечиваемых шиной адреса, определяется как 2N, где N — количество разрядов. Например, 16-разрядная шина адреса обеспечивает 65 536 адресов. Разрядность шины адреса обычно кратна 4 и может достигать 32 и даже 64. Шина адреса может быть однонаправленной (когда магистралью всегда управляет только процессор) или двунаправленной (когда процессор может временно передавать управление магистралью другому устройству, например контроллеру ПДП). Наиболее часто используются типы выходных каскадов с тремя состояниями или обычные ТТЛ (с двумя состояниями). Как в шине данных, так и в шине адреса может использоваться положительная логика или отрицательная логика. При положительной логике высокий уровень напряжения соответствует логической единице на соответствующей линии связи, низкий — логическому нулю. При отрицательной логике — наоборот. В большинстве случаев уровни сигналов на шинах — ТТЛ. Для снижения общего количества линий связи магистрали часто применяется мультиплексирование шин адреса и данных. То есть одни и те же линии связи используются в разные моменты времени для передачи как адреса, так и данных (в начале цикла — адрес, в конце цикла — данные). Для фиксации этих моментов (стробирования) служат специальные сигналы на шине управления. Мультиплексированная шина адреса/данных обеспечивает меньшую скорость обмена, требует более длительного цикла обмена (рис. 1). По типу шины адреса и шины данных все магистрали также делятся на мультиплексированные и немультиплексированные.  Рис. 1. Мультиплексирование шин адреса и данных. В некоторых мультиплексированных магистралях после одного кода адреса передается несколько кодов данных (массив данных). Это позволяет существенно повысить быстродействие магистрали. Иногда в магистралях применяется частичное мультиплексирование, то есть часть разрядов данных передается по немультиплексированным линиям, а другая часть — по мультиплексированным с адресом линиям. Шина управления — это вспомогательная шина, управляющие сигналы на которой определяют тип текущего цикла и фиксируют моменты времени, соответствующие разным частям или стадиям цикла. Кроме того, управляющие сигналы обеспечивают согласование работы процессора (или другого хозяина магистрали, задатчика, master) с работой памяти или устройства ввода/вывода (устройства-исполнителя, slave). Управляющие сигналы также обслуживают запрос и предоставление прерываний, запрос и предоставление прямого доступа. Сигналы шины управления могут передаваться как в положительной логике (реже), так и в отрицательной логике (чаще). Линии шины управления могут быть как однонаправленными, так и двунаправленными. Типы выходных каскадов могут быть самыми разными: с двумя состояниями (для однонаправленных линий), с тремя состояниями (для двунаправленных линий), с открытым коллектором (для двунаправленных и мультиплексированных линий). 9. Объясните, какие машинные циклы осуществляются при выполнении команд MOV M, A; LDA ADDR; INR M; CALL ADDR. По команде MOV выполняется пересылка данных из второго операнда в первый. MOV M, A A → M По команде LDA ADDR загружается аккумулятор из ячейки памяти с адресом ADDR. LDA ADDR M(ADDR) → A По команде INR M инкрементируется регистр M. INR M M = M + 1 По команде CALL ADDR вызывается подпрограмма, находящаяся по адресу ADDR. 12. Опишите преимущества и недостатки микропроцессорных систем с общими шинами и адресным пространством памяти и внешних устройств и с разделением этих шин. Обмен информацией между процессором, памятью и периферийными устройствами осуществляется по системе шин, состав и назначение которых, правила использования, функциональное и физическое разделение при передаче данных, адресов, управляющих сигналов различны для разных ЭВМ. Однако есть принципиально общие закономерности в организации интерфейса, процедуре обмена информацией между двумя устройствами, одно из которых является источником, а другое – приемником информации. Некоторые устройства могут являться приемниками и источниками информации, что требует наличия шин данных для приема и передачи. Передача данных между приемником и источником информации инициируется управляющими сигналами, которые обеспечивают выдачу и прием кодов, проверку состояния готовности устройств, формирование сигналов для выбранного режима обмена. Необходимые сигналы инициируются командами обмена информацией между процессором и периферийными устройствами, процессором и памятью. Если устройство, например источник информации, связано более чем с одним приемником, то также необходимо адресовать выбираемое устройство. При использовании группы шин для приема и выдачи данных, выдачи адреса в режиме разделения времени требуется дополнительный внешний буферный регистр для хранения адреса, что также увеличивает машинный цикл. В настоящее время наиболее распространенным является вариант использования раздельных однонаправленных адресных и двунаправленных шин данных. Однако в некоторых 16-битных однокристальных МП имеет место использование шин данных для передачи полного адреса или старших разрядов адреса. Это позволяет использовать освободившиеся выводы для увеличения числа входов обработки запросов прерываний, организации каналов ввода и вывода информации последовательным кодом. Многообразие в организации и использовании шин данных, адресов и управляющих сигналов является не принципиальным, а только следствием ограничений технологии и числа выводов интегральных схем. Для обмена информацией в общем случае необходимо осуществить следующие основные действия: адресацию периферийного устройства, с которым необходимо произвести обмен, и области памяти, если это требуется; анализ состояния периферийного устройства с целью определить его готовность к обмену для обеспечения совместимости по быстродействию; выполнение требуемых управляющих функций в периферийном устройстве, например, начальный сброс, перемотку, старт, останов и др.; передачу и буферирование данных, если необходимо; окончание процесса обмена путем засылки в процессор сигнала прерывания. Несмотря на многообразие типов ЭВМ, можно выделить две основные организации интерфейса между процессором, памятью и периферийными устройствами: 1. Двухшинную организацию, или интерфейс с изолированной системой шин, который используется в мини-ЭВМ «Электроника-100», М-6000 и др. Название «двухшинная» отражает тот факт, что с функциональной точки зрения есть два такта передачи кодов, процессор — память и процессор — периферийные устройства, обращение к которым осуществляется отдельными группами команд. Однако можно утверждать, что в такой организации имеются четыре шины для передачи кодов в обоих направлениях, или еще можно дополнительно учесть адресные группы шин. Эта неоднозначность часто проистекает из-за того, что разработчики по-своему описывают уже известные организации, делая акцент на отличиях в непринципиальных моментах. Ниже используется понятие «интерфейс с изолированной шиной». 2. Одношинную организацию интерфейса, или интерфейс с общей шиной. Он использован в отечественных мини-ЭВМ М-400, СМ-3(4) и других. Впоследствии многие разработчики микро-ЭВМ стали широко использовать данный способ построения интерфейса. Например, в микро-ЭВМ «Электроника-60» используется модифицированный вариант данной организации, отличительными особенностями которого являются 38 линий вместо 56, передача адреса и данных по общим линиям, сокращенное число входов прерываний и некоторые другие. Интерфейс с изолированной шиной. Данный тип организации интерфейса иллюстрируется на рис. 2. Характерной его особенностью является раздельная адресация памяти и периферийных устройств при обмене информацией. Это осуществляется путем использования отдельных групп команд для обмена информацией с периферийными устройствами и памятью.  Рис. 2. Интерфейс с изолированной шиной Недостатками организации интерфейса с изолированной шиной являются следующие: 1. Обмен выполняется только через аккумулятор МП, и для передачи данного в регистр общего назначения, если аккумулятор занят, требуется выполнение четырех команд. 2. Число подключаемых периферийных устройств ввода или вывода информации не более 256. 3. Для обработки содержимого буферного регистра периферийного устройства, например для анализа готовности к обмену, его необходимо передать в МП. Интерфейс с общей шиной. При данной организации интерфейса часть общего адресного пространства отводится для периферийных устройств, регистры которых адресуются так же, как и ячейки памяти (рис. 3,а). Обращение к периферийным устройствам осуществляется посредством набора команд, используемых для передачи данных с памятью. При этом команды ввода и вывода не используются, а в некоторых МП и процессорах вовсе отсутствуют. Такой принцип построения интерфейса реализуется в МП КР580 путем выделения, например, старшего разряда шины адреса А15 в качестве признака обращения к памяти (0 – 32К) или периферийным устройствам (32К – 64К). На рис. 3,б показано распределение адресного пространства в интерфейсе с общей шиной по сравнению с интерфейсом с изолированной шиной. Под периферийные устройства можно выделить любое адресное пространство при использовании в качестве признака обращения вместо А15 нескольких старших разрядов кода адреса. В качестве управляющих сигналов для обращения к памяти используются сигналы чтения RD и записи WR, а к периферийным устройствам — сигналы I/OR для вывода и I/OW для ввода информации, формируемой в соответствии с рис. 4-4, а.  Рис. 3. Интерфейс с общей шиной (а); распределение адресного пространства (б). К достоинствам интерфейса с общей шиной можно отнести следующие: 1. Расширение набора команд для обращения к периферийным устройствам, что позволяет сократить объем программ и повысить быстродействие. Примерами дополнительных команд для МП КР580 являются следующие: MOV г, М — ввод кода в любой регистр; MOV М, г — вывод кода из любого регистра; MVIM, Data — загрузка в буферный регистр периферийного устройства 8-битного кода; LHLD — ввод 16-битного кода в регистровую пару; SHLD — вывод 16-битного кода из регистровой пары; ANA М — логическое умножение содержимого аккумулятора и буферного регистра периферийного устройства; ADD М — сложение содержимого аккумулятора и буферного регистра периферийного устройства. 2. Значительное увеличение числа подключаемых к МП периферийных устройств. 3. Возможность внепроцессорного обмена данными между периферийными устройствами, если в системе команд имеются команды передачи между ячейками памяти. 4. Возможность обмена информацией не только с аккумулятором, но и с любым регистром МП. В качестве недостатка интерфейса с общей шиной можно отметить сокращение области памяти и усложнение дешифрующих схем. В настоящее время структура интерфейса с общей шиной является очень распространенной в мини- и микро-ЭВМ. |