арх. Контрольная работа по курсу Архитектура Вычислительных Систем

Скачать 0.85 Mb. Скачать 0.85 Mb.

|

|

Контрольная работа по курсу «Архитектура Вычислительных Систем» (N – номер варианта по списку группы) 1. Раздел «Характеристики и классификация ВМ. Типовые комбинационные схемы» Синтезировать комбинационную схему по таблице истинности. Определить ее сложность (в вентилях) и время задержки (во временах tз на вентиль) : В таблице 1 А3 А2 А1 А0 – двоичный код из номера варианта (N mod 16) + 1. Пример: 0 1 1 1 = 7 Таблица 1. X1 X2 X3 Y=F(x1, x2, x3) 0 0 0 1 0 0 1 A0 1 0 1 0 0 0 1 1 1 1 0 0 A1 1 1 0 1 A2 1 1 1 0 0 1 1 1 A3 0 Составить комбинационную схему (КС) по таблице истинности функции (табл.1). Проверить правильность синтеза КС, подав на входы схемы все варианты наборов входных сигналов и сравнив значение логической функции на выходах с заданной таблицей. Определить сложность схемы C в логических элементах и время задержки T, в tзлэ (время задержки на одном логическом элементе). А3А2А1А0 -0111 Таблица 1. Таблица истинности комбинационной схемы

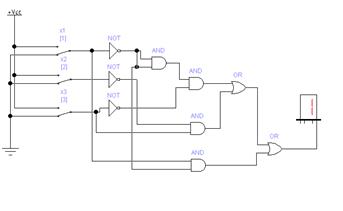

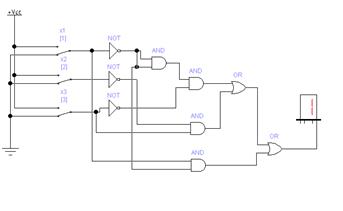

Минимизированная функция: Построенная схема:  Комбинационная схема Сложность схемы: С=9Слэ, Время задержки: t=5tлэ. Составить таблицу истинности и КС одноразрядного полного двоичного сумматора. Определить сложность схемы C и время задержки T. Таблица 2. Таблица истинности для одноразрядного полного сумматора

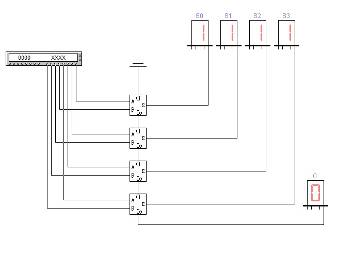

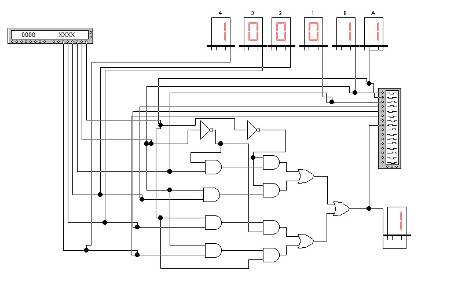

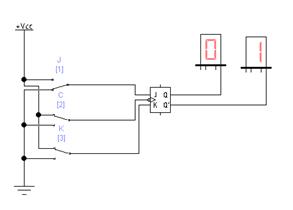

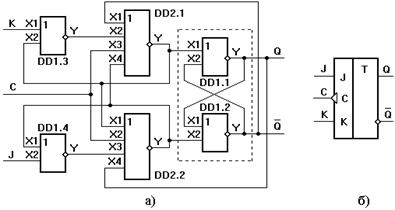

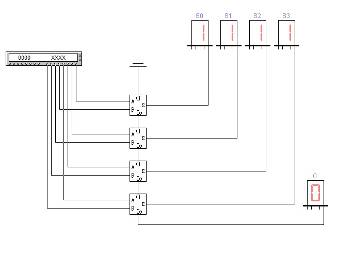

Схема одноразрядного полного двоичного сумматора Сложность схемы: С=7Слэ, Время задержки: t=3tлэ. Составить схему параллельного сумматора с последовательным переносом на 4 разряда и проверить ее работоспособность. Определить сложность схемы C и время задержки T.  Схема параллельного сумматора с последовательным переносом на 4 разряда Сложность схемы: С=4СSM=4*7=21Слэ, Время задержки: t=4*tSM=4*3=12tлэ. Синтезировать схему 4-х разрядного мультиплексора 2 x 1. Поместить мультиплексор в подсхему. Определить сложность схемы C и время задержки T.  Схема 4-х разрядного мультиплексора 2х1 Сложность схемы: С=13Слэ, Время задержки: t=4tлэ. Синтезировать схему JK - триггера с управлением по спаду тактового импульса на базе библиотечного JK - триггера. Получить таблицы установки и временные диаграммы работы триггеров.  Исследование JK триггера  Синтезировать схему для перевода числа из прямого кода в дополнительный. Синтезировать схему одноразрядного полного двоичного сумматора – ОПДС - (без вариантов). Определить ее сложность (в вентилях) и время задержки (во временах tз на вентиль) Составить комбинационную схему (КС) по таблице истинности функции (табл.1). Проверить правильность синтеза КС, подав на входы схемы все варианты наборов входных сигналов и сравнив значение логической функции на выходах с заданной таблицей. Определить сложность схемы C в логических элементах и время задержки T, в tзлэ (время задержки на одном логическом элементе). А3А2А1А0 -0111 Таблица 1. Таблица истинности комбинационной схемы

Минимизированная функция: Построенная схема:  Комбинационная схема Сложность схемы: С=9Слэ, Время задержки: t=5tлэ. Составить таблицу истинности и КС одноразрядного полного двоичного сумматора. Определить сложность схемы C и время задержки T. Таблица 2. Таблица истинности для одноразрядного полного сумматора

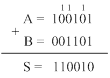

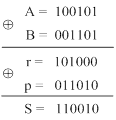

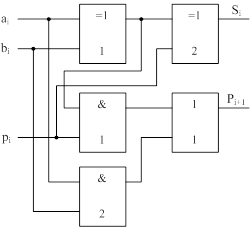

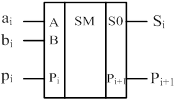

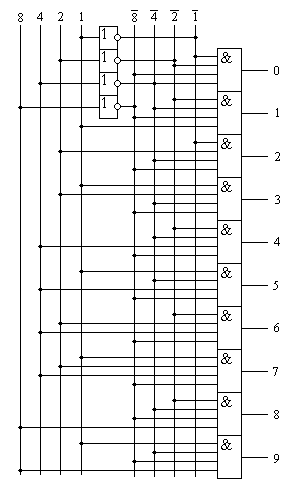

Схема одноразрядного полного двоичного сумматора Сложность схемы: С=7Слэ, Время задержки: t=3tлэ. Составить схему параллельного сумматора с последовательным переносом на 4 разряда и проверить ее работоспособность. Определить сложность схемы C и время задержки T.  Схема параллельного сумматора с последовательным переносом на 4 разряда Сложность схемы: С=4СSM=4*7=21Слэ, Время задержки: t=4*tSM=4*3=12tлэ Синтезировать схему параллельного сумматора с последовательным переносом, составленного из ОПДС. Количество разрядов определяется как N mod 4 + 2. Определить ее сложность (в вентилях) и время задержки (во временах tз на вентиль). N mod 4 – операция определения остатка от деления N на 4, то есть число от 0 дот 3. Эмпирический способ построения сумматора базируется на том, что алгебраическое сложение кодов чисел по существу сводится к совокупности элементарных логических операций.  Сложением по модулю 2 (mod 2) получится следующее:  Таким образом, для каждого i-ого разряда можно записать следующие логические выражения: где ai, bi - i-й разряд слагаемого а и b соответственно; ri - промежуточная сумма по mod 2 в i-ом разряде; pi - перенос в i-ый разряд; Si - сумма в i-ом разряде. По полученным выражениям можно построить схему электрическую функциональную одноразрядного сумматора, представленную на рисунке 8.  Рисунок 8 - Сумматор одноразрядный Схема электрическая функциональная Условное графическое обозначение (УГО) ОС-3 представлено на рисунке 9.  Рисунок 9 - Сумматор одноразрядный ОС-3 УГО Таким образом, для построения четырехразрядного сумматора с последовательным переносом, схема электрическая функциональная которого представлена на рисунке 10, необходимо использовать четыре одноразрядных сумматора ОС-3, соединенных последовательно цепями переносов. Синтезировать схему полного дешифратора с M входами и K выходами, где M = (N mod 3) + 1. Определить ее сложность (в вентилях) и время задержки (во временах tз на вентиль). Рассмотрим пример разработки схемы дешифратора из двоичного кода в десятичный. Десятичный код обычно отображается одним битом на одну десятичную цифру. В десятичном коде десять цифр, поэтому для отображения одного десятичного разряда требуется десять выходов дешифратора. Сигнал с этих выводов можно подать на десятичный индикатор. В простейшем случае над светодиодом можно просто подписать индицируемую цифру.Таблица истинности десятичного дешифратора приведена в таблице 1. Таблица 1. Таблица истинности десятичного дешифратора.

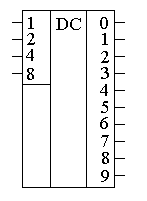

Для реализации принципиальной схемы дешифратора воспользуемся методом СДНФ, так как в его таблице истинности на каждом выходе присутствует всего одна логическая единица. В результате получим схему дешифратора, реализующего таблицу истинности, приведённую в таблице 1. Эта схема приведена на рисунке 1.  Рисунок 1. Принципиальная схема двоично-десятичного дешифратора Как видно по принципиальной схеме дешифратора, для реализации каждой строки таблицы истинности потребовался логический элемент "4И". Логические элементы "ИЛИ" не потребовались, так как в таблице истинности на каждом выходе присутствует только одна логическая единица. Дешифраторы выпускаются в виде отдельных микросхем или используются в составе более сложных микросхем. В настоящее время десятичные или восьмеричные дешифраторы используются в основном как составная часть других микросхем, таких как мультиплексоры, демультиплексоры, ПЗУ или ОЗУ. Условно-графическое обозначение микросхемы дешифратора на принципиальных схемах приведено на рисунке 2. На этом рисунке приведено обозначение двоично-десятичного дешифратора, полная внутренняя принципиальная схема которого изображена на рисунке 1.  Рисунок 2. Условно-графическое обозначение двоично-десятичного дешифратора Точно таким же образом можно получить принципиальную схему и для любого другого декодера (дешифратора). Наиболее распространены схемы восьмеричных и шестнадцатеричных дешифраторов. Для индикации такие дешифраторы в настоящее время практически не используются. В основном такие дешифраторы используются как составная часть более сложных цифровых модулей. II | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||