арх. Контрольная работа по курсу Архитектура Вычислительных Систем

Скачать 0.85 Mb. Скачать 0.85 Mb.

|

|

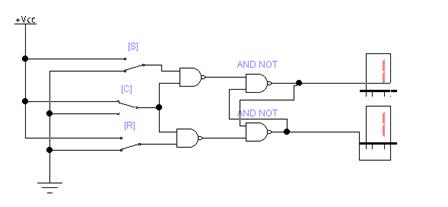

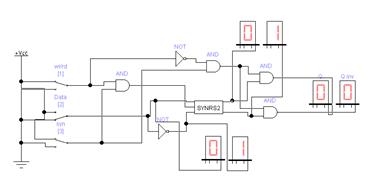

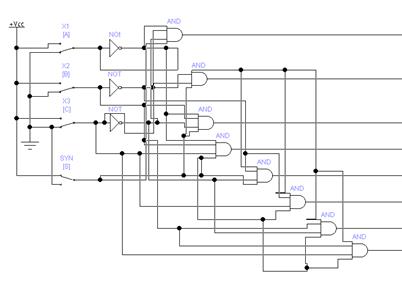

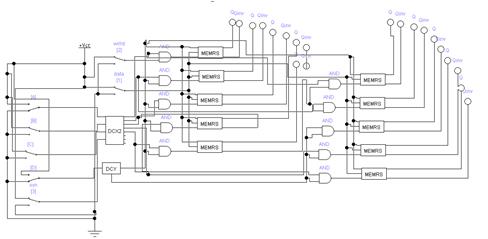

Раздел «Системы памяти» Синтезировать схему ячейки памяти по варианту. Вариант определяется как (N mod 6) + 1: типа 2D на базе RS триггера типа 3D на базе RS триггера типа 2D на базе JK триггера типа 3D на базе JK триггера типа 2D на базе D триггера типа 3D на базе D триггера Синтезировать схему одной ячейки ОЗУ адресного типа с прямым доступом для устройства типа 3D на RS-триггерах.  Синхронный RS триггер Сложность схемы: С=4Слэ, Время задержки: t=2tлэ.  Сложность схемы: С=10Слэ, Время задержки: t=6tлэ. Синтезировать схему запоминающего устройства на базе ячейки, полученной в п.1, типа 3D на RS-триггерах с организацией 5х2.  Схема дешифратора DCX Сложность схемы: С=35Слэ, Время задержки: t=4tлэ. Таблица 3. Таблица истинности дешифратора DCX

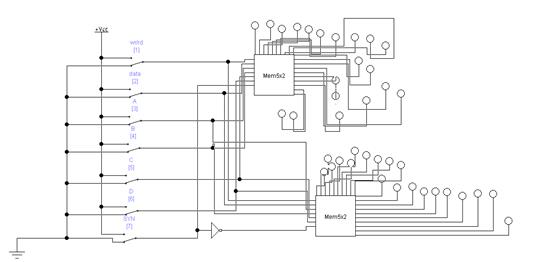

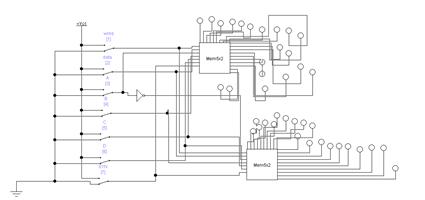

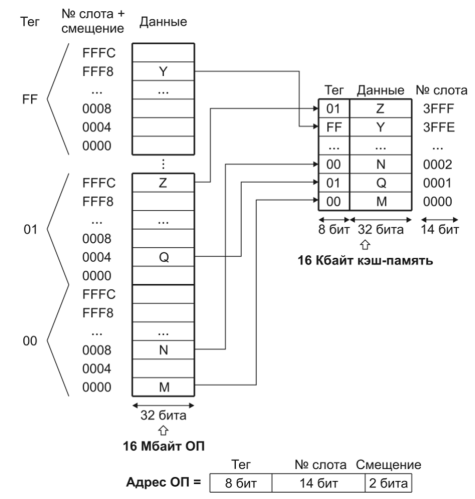

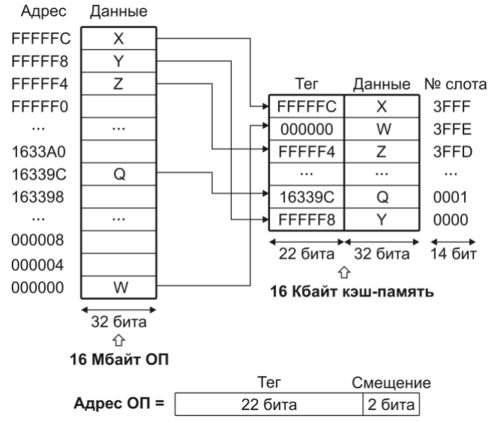

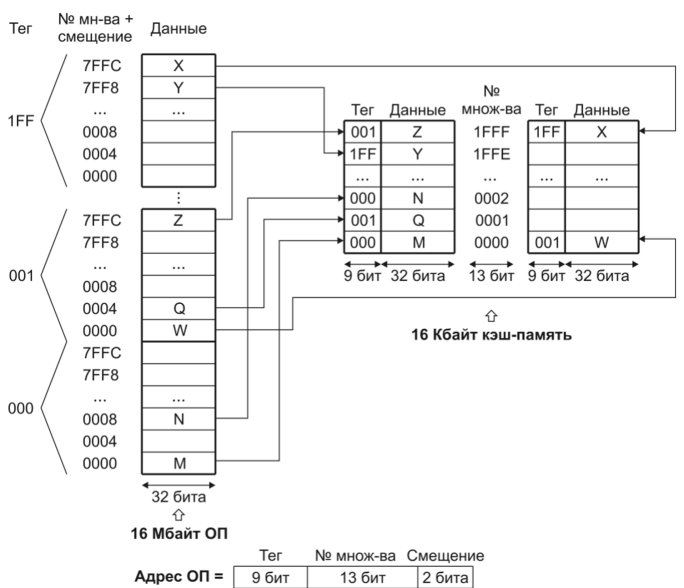

Схема дешифратора DCY Таблица 4. Таблица истинности DCY  Схема массива ячеек памяти типа 3D 5x2 Сложность схемы: С=10Сmem+CDCX+CDCY +10Сand=10*10Слэ+35Cлэ+Cлэ+ 10Cлэ =146Слэ, Время задержки: t=tDCX+tmem + tDCY =11tлэ. На базе ЗУ, полученного при выполнении предыдущего задания, синтезировать схему ЗУ вдвое большего объема (с удвоенным количеством адресуемых слов). Реализовать 2 варианта: а) дополнительный бит адреса является старшим; б) дополнительный бит адреса является младшим (расслоение памяти). а) дополнительный бит адреса является старшим:  Удвоение массива для варианта а) Сложность схемы: С=2СMem5x2+Слэ=2*146+1=293Слэ, Время задержки: t=tлэ+tMem5x2=11+1=12tлэ. б) дополнительный бит адреса является младшим (расслоение памяти):  Удвоение массива для варианта б) Сложность схемы: С=2СMem5x2+Слэ=2*146+1=292Слэ, Время задержки: t=tлэ+tMem5x2=11+1=12tлэ. Построить блок памяти из устройств памяти меньшего объема (можно функциональную схему, без Quartus) : с последовательным распределением адресов по устройствам и с расслоением памяти. Объем всего модуля памяти : V = 2 (30 - ((N mod 8) + 1)) ; Объем одного устройства : V1 = 2 21 слов 0x001 --> 1 ячейка 2 микросхемы; 0x002 --> 1 ячейка 3 микросхемы; 0x003 --> 1 ячейка 4 микросхемы; 0x004 --> 2 ячейка 1 микросхемы; Для заданного варианта размещения программы в оперативной памяти, объема основной памяти и заданных характеристик кэш-памяти (варианта отображения строк основной памяти на строки буферной памяти, количества строк буферной памяти, времени обращения к буферной памяти и к основной памяти) рассчитать коэффициент попадания в кэш-память, эффективное время обращения и ускорение при использовании кэш-памяти. Как изменятся рассчитанные параметры при изменении варианта отображения, при повторном выполнении программы (оценить качественно) ? Объем строки : 16 слов. Объем основной памяти : 1024 слова. Объем КЭШ-памяти : 128 слов; Вариант отображения: 1,5) прямое отображение; 2, 6) полностью ассоциативная КП; 3, 7) множественно ассоциативная память с 2 множествами; 4, 8) множественно-ассоциативная 2 - канальная; Время обращения к основной памяти 50 нс, время подкачки (при промахе – считывание всех 16 слов): 400 нс; Время обращения к КЭШ-памяти (при попадании) : 10 нс; Программа размещается в адресах с N + 10 по N + 30, с N + 50 по N + 80, с N + 150 по N + 160, затем выполняется цикл с 508 + N по 528 + N адрес 10 – N раз. Существует три схемы отображения адресов оперативной памяти в кэш-память: прямая, ассоциативная и множественно-ассоциативная. В зависимости от схемы отображения адресов различают три типа кэшпамяти: кэш-память с прямым отображением, кэш-память с ассоциативным отображением и кэш-память с множественно-ассоциативным отображением. Рассмотрим каждую из перечисленных схем отображения адресов на следующем примере. Пусть основная память составляет 16 Мбайт (16 Мбайт = 224 байт), кэш-память имеет объем 64 Кбайта, размер кэш- строки составляет 4 байта. В кэш-памяти с прямым отображением адрес ячейки данных в памяти состоит из трех частей: тега, индекса и смещения внутри блока. Согласно длине блока (4 байта) основная память объединяет 2" блока, а кэш-память содержит 214 кэш-строк. Логика кэш-памяти с прямым отображением интерпретирует 24 разряда адреса блока как 8-битный тег (старшие разряды адреса), 14-битный индекс (средние разряды адреса) и 2-битное смещение (младшие разряды адреса) .  Следующая формула устанавливает отображение адресов основной памяти и строк кэш-памяти: S = A mod С, где S - адрес строки (индекса) кэш-памяти; А - адрес блока основной памяти; С - число строк в кэш-памяти. Так, блоки с номерами 000000, 010000, ..., FF0000 основной памяти отображаются в строку кэшпамяти с номером 0, блоки с номерами 000004, 010004, ..., FF0004 основной памяти отображаются в строку с номером 1 и так далее. Кэш-память с прямым отображением имеет высокую скорость выполнения операций, простую и недорогую реализацию, с одной стороны; с другой стороны, видно, что данный алгоритм в одну и ту же строку кэш-памяти отображает несколько блоков оперативной памяти, в нашем случае 28 блоков. Это означает, что если в программе последовательно происходят обращения к элементам памяти, отстоящим на величину, кратную размеру кэш-памяти, то все эти элементы будут претендовать на одну и ту же строку кэш-памяти. Несмотря на то что в кэшпамяти в данный момент может быть сколько угодно пустых строк. Такая ситуация называется эффектом буксования кэш-памяти. Буксование служит примером неэффективной работы кэш-памяти, поскольку для размещения каждого следующего элемента данных, участвующего в вычислении, необходимо вытеснить предыдущий элемент данных из кэш-памяти и обратиться в оперативную память. Устранив этот эффект, можно существенно уменьшить время работы программы. В кэш-памяти с ассоциативным отображением любой блок памяти может быть записан в любую кэш-строку. Поэтому здесь эффект буксования кэш-памяти отсутствует. При ассоциативном отображении адрес блока представляется в виде двух компонентов: тега и смещения внутри блока (рис. 12).  Для примера на рис. 11 адрес состоит только из тега, занимающего 22 разряда, и смещения, занимающего два младших разряда. В отличие от прямого отображения в адресе не задается номер слота. Нахождение нужной строки в кэш-памяти сводится к сравнению тега адреса блока затребованных данных с тегами всех строк параллельно. Одновременное сравнение - это сложная аппаратная задача. Поэтому время доступа к ассоциативной кэш-памяти, как правило, значительно больше, чем время доступа к кэш-памяти с прямым отображением. При отсутствии свободной строки в кэш-памяти любая из ее строк может быть заменена на требуемую строку. В кэш-памяти с множественно-ассоциативным отображением (или наборно-ассоциативным отображением) несколько блоков памяти с одинаковым индексом и разными тегами могут быть записаны в одно множество (набор). Количество блоков в множестве называется степенью ассоциативности. На практике типичными размерами множества бывают 2, 4, 8, 16. Множественно-ассоциативная кэш-память может быть представлена как несколько параллельно работающих кэш-памятей прямого отображения, которые принято называть банками. Число банков равно степени ассоциативности кэш-памяти. Для данной схемы отображения адресов адрес состоит из трех компонентов: тега, номера множества и смещения в блоке. Решение, в какой именно банк размещать блок данных, принимает кэш-контроллер. Выбор нужной кэш-строки в банке однозначно определяется номером множества, получаемым из адреса блока. На рис. 13 приведен пример множественно-ассоциативной кэшпамяти со степенью ассоциативности, равной двум. Поскольку количество кэш-строк в кэш-памяти равно 2 , а каждое множество содержит по две кэш-строки (по числу банков), число множеств будет 213, соответственно разрядность номера множества будет 13 бит. Разрядность смещения для адресации 4 байт блока равна 2 битам, и на тег остается 9 старших бит адреса. В множественно-ассоциативной кэш-памяти, как и в кэш-памяти прямого отображения, возможен эффект буксования. Но здесь он происходит гораздо реже, так как для него требуется уже не одно, а несколько обращений, претендующих на одно и то же множество кэш- строк. Причем число таких конфликтующих обращений должно быть больше степени ассоциативности кэш-памяти.  В табл. 1 приведены характеристики кэш-памятей некоторых современных микропроцессоров: объем, степень ассоциативности (ст.а.) и размер кэш-строки. Все представленные процессоры многоядерные. Видно, что большинство современных микропроцессоров имеет два- три уровня кэш-памяти, причем первые один или два уровня дублируются на каждом ядре и разделены на кэш-память команд и кэш-память данных, а кэш-память последних уровней является общей для всех ядер. Размер кэш-памяти становится больше с увеличением уровня. Таблица 1 Параметры кэш-памяти современных микропроцессоров

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||