9305_АникинаАА. Курсовая работа по дисциплине архитектура эвм вариант 3 студентка группы 9305 Аникина Анна Проверил

Скачать 0.6 Mb. Скачать 0.6 Mb.

|

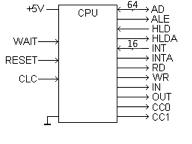

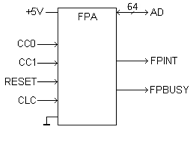

1.4. Средства реализации моделиВ качестве языка реализации используется язык Java. 1.5. Результаты проектированияВ процессе выполнения курсового проекта разрабатываются: - архитектура ЦП; - приложение (программный эмулятор). В процессе разработки архитектуры определяются: 1. Форматы команд и данных. 2. Регистровая модель процессора (включая пользовательские и системные регистры). 3. Структура выводов кристалла. 4. Система команд (включая семантику их выполнения и установку флажков). 5. Обобщенный алгоритм функционирования процессора (включая алгоритмы выполнения основных команд). 6. Алгоритмы выполнения основных операций на шине (чтение, запись, ввод, вывод, захват шины, прерывание). Необходимо предусмотреть пакетный режим обмена между ОП и кэш-памятью. 7. Внутренняя организация (до структурного уровня) (включая механизмы виртуальной памяти, механизмы защиты памяти и механизмы работы с кэш-памятью). В процессе разработки модели создаются: UML диаграммы, описывающие функционирование модели; - собственно приложение; - комплект документации на программную систему. Должны быть разработаны следующие UML диаграммы: - диаграммы вариантов использования (use case diagrams); - диаграмма классов (class diagram). В состав документации на созданное приложение входят: - руководство оператора; - руководство системного программиста; - программа и методика испытания. 2. Последовательность выполнения курсового проекта2.1. Общая последовательностьВыполнение проекта осуществляется в следующем порядке: 1. Разработка архитектуры ЦП. 2. Разработка программной модели. 3. Разработка документации на программный проект. 4. Оформление отчета. 2.2. Разработка архитектуры ЦП2.2.1. Уточнение структуры системыРазрабатываемый процессор предназначен для использования в качестве центрального процессора (ЦП) рабочей станции В состав станции входят: несколько процессорных кристаллов, составляющих предмет разработки; ОЗУ; системный чип; контроллеры внешних устройств; видеоадаптер. Имеются две шины – быстрая системная шина и шина ввода-вывода, разделенные системным чипом. В качестве шины ввода-вывода обычно используется стандартная шина, например PCI. Системный чип (чипы) содержит внешнюю логику (таймеры, часы реального времени, контроллеры ПДП и т. п.).  2.2.2. Разработка архитектуры внешних выводов  AD – совмещенная шина адреса и данных; ALE – сигнал ALE используется для фиксации адреса на внешнем регистре – защелке; HLD – запрос прямого доступа; HLDA – подтверждение прямого доступа; INT – 16 входов запросов на прерывание; INTA – подтверждение запроса на прерывание; RD,WR – линии управляют чтением и записью в память; IN,OUT – линии для управлением чтением и записью в порт; СС0, СС1 – линии служат для синхронизации работы CPU и FPA WAIT – устанавливается в 1, когда сопроцессор закончил вычисления; RESET – сигнал сброса; CLC – синхронизация; FPINT – прерывание особой ситуации сопроцессора; FPBUSY – сигнал занятости сопроцессора. Процессор Сигнал ALE используется для фиксации адреса на внешнем регистре-защелке, а пара сигналов HLD и HLDA – для реализации механизма захвата шины. Сигналы INT и INTA являются сигналами запроса и подтверждения прерывания. Если на корпусе имеется достаточное число свободных выводов, то целесообразно ввести несколько уровней запроса на прерывание. Линии RD (Чтение), WR (Запись), IN (Ввод), OUT (Вывод), задают выполняемую на шине операцию. Сигнал WAIT используется для организации взаимодействия с внешним математическим сопроцессором. На контакт WAIT поступает сигнал от сопроцессора об окончании вычислений. Контакт READY (Готовность) служит для приема сигнала готовности от медленных внешних устройств. Назначение выводов питания, RESET и CLC (Синхронизация) очевидны. Сопроцессор На вывод FPBUSY подается единичный сигнал, указывающий на то, что сопроцессор занят. По линии FPINT выдается сигнал прерывания в случае возникновения ошибочной ситуации (типа попытки деления на нуль). Назначение прочих выводов такое же, как и одноименных выводов ЦП. |