|

|

9305_АникинаАА. Курсовая работа по дисциплине архитектура эвм вариант 3 студентка группы 9305 Аникина Анна Проверил

Виртуальная память

По заданию модель памяти должна удовлетворять требованиям, предъявляемым многопользовательской многозадачной ОС типа UNIX.

Многозадачность – свойство операционной системы или среды программирования обеспечивать возможность параллельной (псевдопараллельной) обработки нескольких процессов. Для запуска нескольких процессов необходимо для каждого выделить собственное адресное пространство, что не совсем эффективно, поскольку много процессов используют лишь малую часть своего адресного пространства и физического адресного пространства может не хватить.

Для решения этой проблемы используется виртуальная память.

Виртуальная память – система основной и дисковой памяти, организуемая для расширения адресного пространства.

Физическое адресное пространство ФАП - совокупность адресов, соответствующих реально адресуемым физическим ячейкам памяти

Виртуальное адресное пространство ВАП – это совокупность адресов, которая может использоваться для доступа к данным.

Виртуальная память делит ФАП на блоки и выделяет их разным процессам.

Разделяют несколько типов организации виртуальной памяти.

При страничной организации памяти :

Виртуальная память делится на блоки одинаковой длины - страница (page), обычно размер страницы - 4Кб – 8Кб (степень двойки)

Физическая память, соответственно, делится на фреймы или кадры (frame) такого же размера

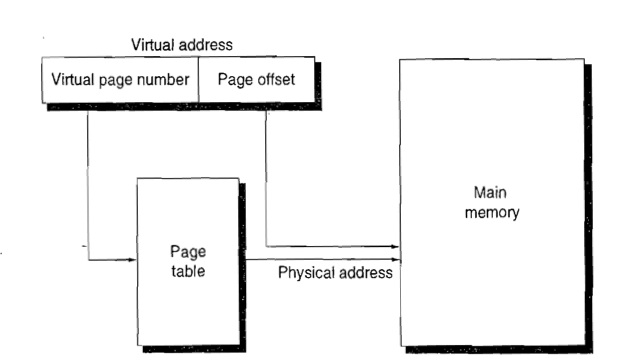

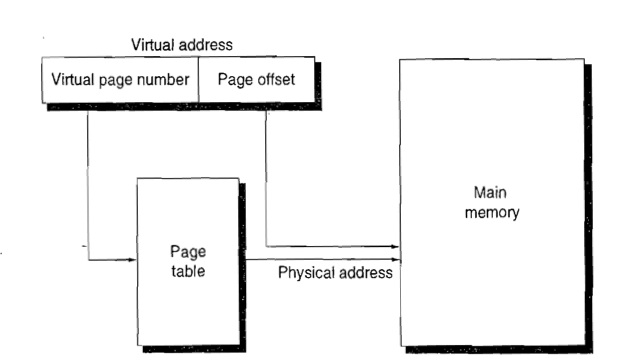

Система отображения виртуальных адресов в физические сводится к системе отображения виртуальных страниц в физические и представляет собой таблицу страниц.

Таблицы страниц обычно хранятся в оперативной памяти. Для ссылки на таблицу страниц используется специальный регистр процессора.

Для ускорения страничного преобразования в процессоре имеется специальная кэш-память (сверхбыстродействующей буферной памяти), называемая TLB (Translation Lookaside Buffer).

При каждом преобразовании номера виртуальной страницы в номер физической страницы результат заносится в TLB: номер физической страницы в память данных, а виртуальной - в память тегов. Таким образом, в TLB попадают результаты нескольких последних операций трансляции адресов. При каждом обращении к ОП преобразователь адресов сначала производит поиск в памяти тегов TLB номера требуемой виртуальной страницы. При попадании адрес соответствующей физической страницы берется из памяти данных TLB. Если в TLB зафиксирован промах, то процедура преобразования адресов производится с помощью страничной таблицы, после чего осуществляется запись новой пары «номер виртуальной страницы - номер физической страницы» в TLB.

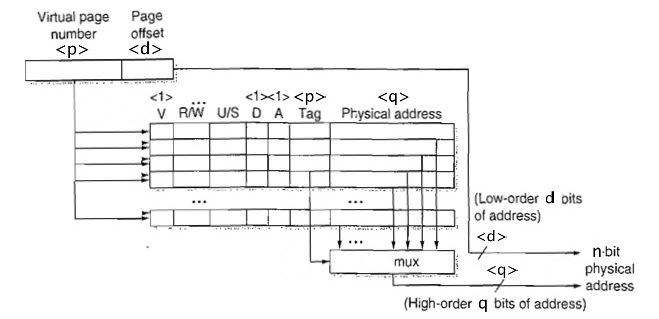

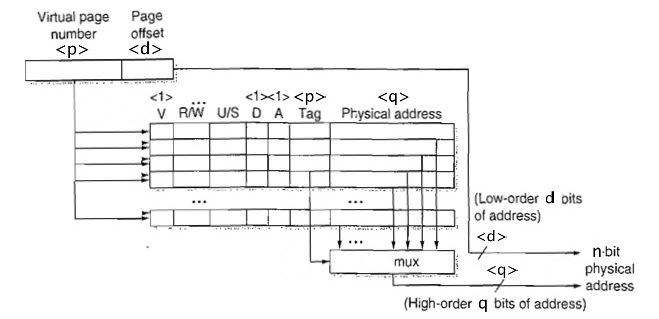

Виртуальный адрес состоит из виртуального номера страницы (p) и смещения (d). Номер виртуальной страницы используется как индекс в таблице страниц для нахождения записи (entry) о виртуальной странице. Из этой записи в таблице страниц находится номер кадра (page frame number), затем прибавляется смещение и формируется физический адрес. Помимо этого запись в таблице страниц содержит информацию об атрибутах страницы, в частности биты защиты.

Атрибуты

Признак присутствия V устанавливается в единицу, если виртуальная страница в данный момент находится в основной памяти. В этом случае в поле номера физической страницы находится соответствующий номер. Если V = 0, то при попытке обратиться к данной виртуальной странице преобразователь адреса генерирует сигнал страничного сбоя (page fault), и операционная система предпринимает действия по загрузке страницы с диска в ОП. Загрузка страницы с диска в ОП сопровождается записью в соответствующую строку страничной таблицы (указывается номер физической страницы, куда была загружена виртуальная страница).

D (Dirty) — признак, который устанавливается перед операцией записи по адресу, в преобразовании которого участвует данная строка. Таким образом помечается “грязная” страница, которую в случае замещения необходимо выгрузить на диск.

Признак прав доступа А - признак доступа, который устанавливается перед любым чтением или записью по адресу, в преобразовании которого участвует данная строка.

Механизм защиты страниц различает два уровня привилегий: пользователь (User) и супервизор (Supervisor). Пользователю соответствует уровень привилегий 3, супервизору — уровни 0, 1 и 2. Строки таблиц имеют атрибуты защиты страниц — биты U/S (User/Supervisor) и R/W (Read/Write).

Для того чтобы избежать необходимости иметь огромную таблицу в памяти все время, а хранить лишь несколько ее фрагментов можно использовать используют многоуровневую таблицу страниц.

Регистровая память процессора

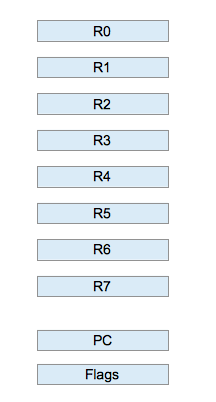

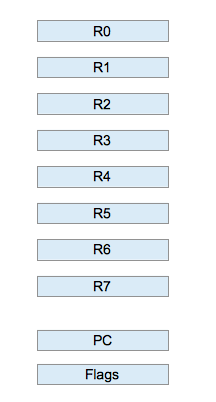

8 регистров функционально ориентированного типа, 64-разрядные.

Функциональная ориентация РОН подразумевает их разбиение на группы в зависимости от функционального назначения

Определенные регистры предназначены для хранения определенных форматов данных (64 разрядные числа, 32 разрядные числа, 8 разрядные числа)

R0 – содержит в себе 8 разрядные числа

R1-R2 разделенные регистры по 32 разряда, содержат 32 разрядные числа

R3-R7 – регистры 64-разрядные

R0: ориентированы для хранения 8-разрядных чисел

64

|

56

|

55

|

48

|

47

|

40

|

39

|

32

|

31

|

24

|

23

|

16

|

15

|

8

|

7

|

0

|

111

|

110

|

101

|

100

|

011

|

010

|

001

|

000

|

R1 ориентированы для хранения 32-разрядных чисел

R2: ориентированы для хранения 32-разрядных чисел

R3: ориентированы для хранения 64-разрядных чисел

R4: ориентированы для хранения 64-разрядных чисел

R5: ориентированы для хранения 64-разрядных чисел

R6: ориентированы для хранения 64-разрядных чисел

R7: ориентированы для хранения адресов

Регистр флагов:

Флаги состояния:

С – Флаг переноса из старшего разряда

Z – Флаг нулевого значения устанавливается, если результат равен нулю.

S – Флаг знака

равен значению старшего значащего бита результата, который является знаковым битом в знаковой арифметике.

O - Флаг переполнения

устанавливается, если целочисленный результат слишком длинный для размещения в целевом операнде (регистре или ячейке памяти). Этот флаг показывает наличие переполнения в знаковой целочисленной арифметике (в дополнительном коде)

Системные флаги

T - Флаг трассировки (пошаговое выполнение)

установка этого флага разрешает пошаговый режим отладки, когда после каждой выполненной инструкции происходит прерывание программы и вызов специального обработчика прерывания

I – Флаг разрешения прерываний

Бит маскирования прерываний (I)-запрещает все маскируемые прерывания при установке его в 1. Бит I автоматически устанавливается при возникновении любого прерывания сразу же после сохранения регистров в стеке, но до передачи управления по вектору прерывания. Если внешнее прерывание происходит в тот момент, когда ,бит I установлен в 1, то запрос на прерывание фиксируется и обрабатывается после сброса бита I. После обслуживания прерывания, команда возврата из прерывания восстанавливает содержимое регистров. Таким образом, после обработки прерывания I-бит сбрасывается, а при начальной установке бит I устанавливается в 1.

Регистровая память сопроцессора

Сопроцессор содержит 8 регистра R8...R15 по 64 разряда каждый.

Кроме этих регистров сопроцессор содержит регистр флажков и управления, работа с которыми производится специальными командами.

Значения бит:

B – бит занятости сопроцессора,

Z – признак нуля результата;

S – знак результата;

O – переполнение;

I – разрешение прерывания исключительной ситуации;

RC – режим округления:

00 – в минус бесконечность

01 – в плюс бесконечность

10 – к ближайшему целому

11 – в сторону нуля.

B

|

Z

|

S

|

O

|

I

|

0

|

RC

|

7

|

6

|

5

|

4

|

3

|

2

|

1

|

0

|

|

|

|

Скачать 0.6 Mb.

Скачать 0.6 Mb.