9305_АникинаАА. Курсовая работа по дисциплине архитектура эвм вариант 3 студентка группы 9305 Аникина Анна Проверил

Скачать 0.6 Mb. Скачать 0.6 Mb.

|

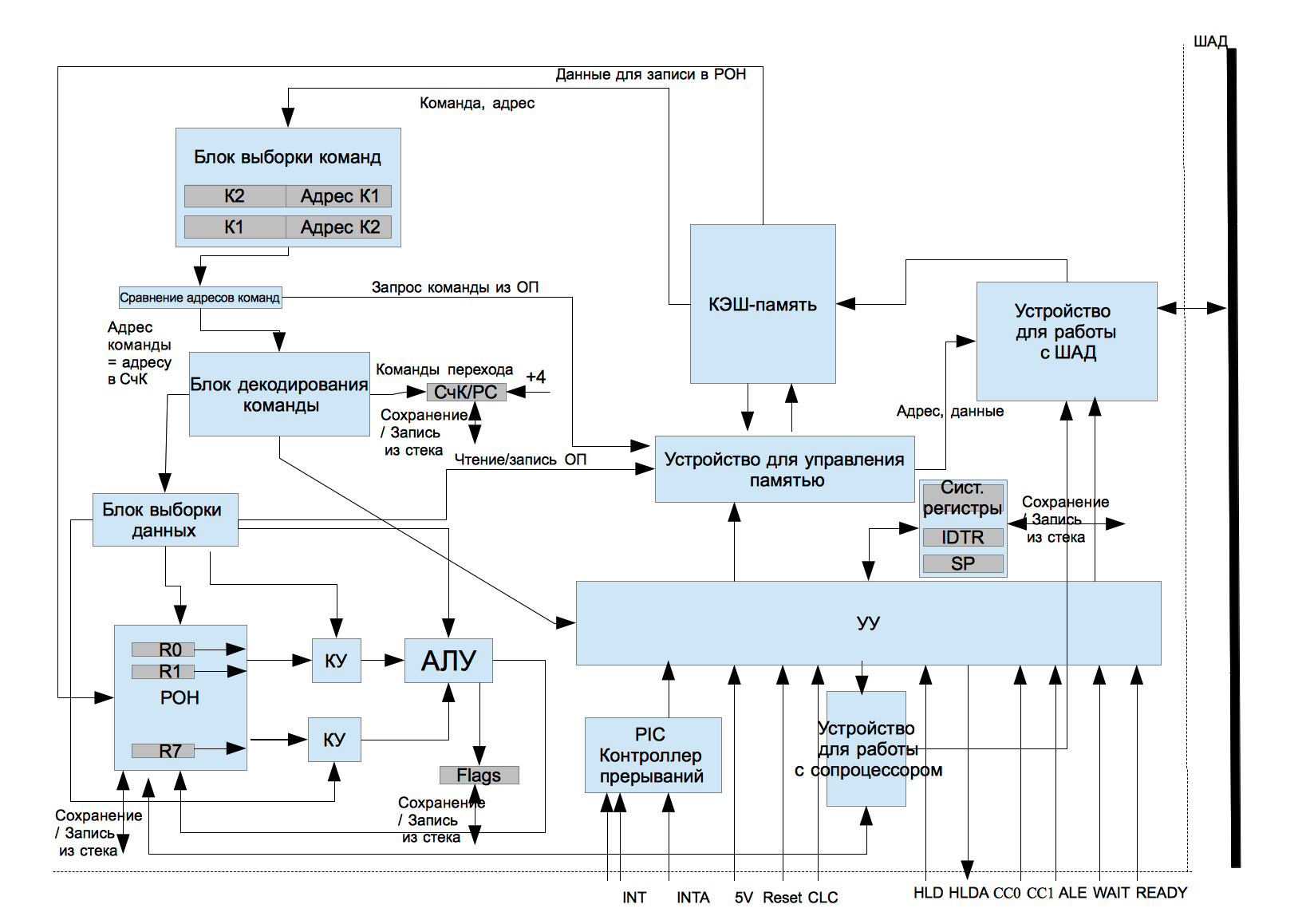

2.2.7. Внутренняя организацияВ процессоре реализуется конвейерный принцип обработки информации. Если некоторый процесс обработки информации может быть разбит на последовательные этапы, выполняемые независимо параллельно работающими обрабатывающими устройствами, и результаты предыдущего этапа являются исходными данными для следующего, то такой процесс называется конвейерной обработкой, а система обрабатывающих устройств - конвейером. Этапы конвейера часто называют ступенями Используется двухступенчатый конвейер.  Для двухступенчатого конвейера выделяются фаза выборки команды и фаза выполнения команды. Параллельно и асинхронно могут работать два процессора: процессор памяти и исполнительный процессор. Процессор памяти обеспечивает работу с памятью команд и памятью данных, а также с кэш-памятью. На исполнительный процессор возлагаются функции, связанные с дешифрацией и выполнением команд

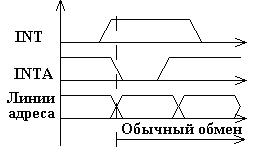

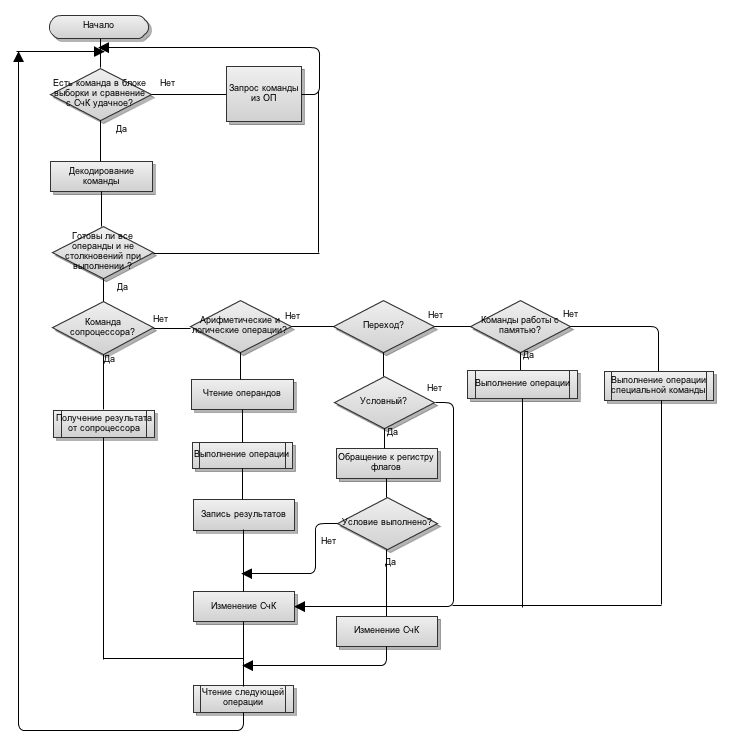

Структурная схема центрального процессора Структурная схема центрального процессора2.2.8. Основные алгоритмы функционированияВыполнение одной инструкции процессора содержит пять следующих шагов: Проверяется наличие следующей команды в блоке выборки команд. Команда передается в блок декодирования Блок декодирования команд расшифровывает команду Если это команда перехода, то в счетчик команд записывается адрес перехода и управление передается в блок выборки инструкций , иначе счетчик команд увеличивается на размер команды и передает управление в блок выборки данных Блок выборки данных считывает из КЭШ-памяти или ОП требуемые для выполнения команды данные и передает управление УУ (устройству управления) Управляющее устройство (УУ) определяет, какому блоку выполнения инструкций обработать текущую задачу, и передает управление этому блоку Блоки выполнения инструкций выполняют требуемые командой действия и передают управление УУ.  Общий алгоритм функционирования процессора Общий алгоритм функционирования процессораАлгоритм функционирования сопроцессора 2.2.9. Алгоритмы выполнения отдельных операцийЧтение команды из ОЗУ Запрос на чтение команды из памяти. Сравнение совпадает ли адрес команды и тег в кэш-памяти При совпадении – кеш-попадание и возвращается копия данных из кэша. При кэш промахе – чтение из ОП: адрес устанавливается в качестве адреса на системной шине. ОЗУ получает адрес и выдает на системную шину данные, которые перехватывает процессор. Добавление блока данных в кэш. Вернуть копию данных из кэша? Декодирование команды Команда из блока выборки помещается в регистр команд. Инкрементируется PC. Осуществляется дешифрация команды. В зависимости от кода операции, определяется тип команды и перечень необходимых действий. Устройство управления формирует необходимые машинные циклы, обеспечивающие исполнение текущей команды. Командный цикл завершается после выполнения всех машинных циклов, инициализируемых блоком управления. Обработка регистровой команды Выборка операндов. В зависимости от значений адресных полей регистра команд срабатывает комбинационное устройство, подключаются нужные регистры или определенные байты регистра. Операнды подаются на входы АЛУ. Управляющий сигнал для АЛУ в зависимости от содержимого регистра команд указывает АЛУ тип данных и их разрядность. Устройство управления дает разрешение на «захват» операндов, которые передаются напрямую в АЛУ. Производится формирования результата соответствующей операции: арифметической, логической, перехода. Результат заносится в регистр указанный в коде операции. Обработка команды типа регистр – память Формирование адреса операнда производится в зависимости от типа адресации. Если осуществляется чтение из памяти, то на шине данных выставляется значение соответствующей ячейки памяти. Устройство управления устанавливает направление передачи, осуществляет коммутацию внутренней и системных шин. А затем данные с шины записываются в кэш, а затем в указанный регистр центрального процессора. Если осуществляется запись в памяти, то на шине данных выставляется значение соответствующего регистра центрального процессора. Перед тем как записать в память, данные проверяются на наличие и записываются в кеш-память. Устройство управления задает направление передачи, осуществляет коммутацию внутренней и системных шин. А затем данные с шины из указанного регистра центрального процессора записываются нужную ячейку памяти. Обработка безусловных переходов (Б/П) Формирование адреса операнда производится в зависимости от типа адресации. Реализуется безусловный переход – счетчику команд присваивается значение сформированного адреса. Новый командный цикл изменит последовательный ход программы. Обработка условных переходов (У/П) Формирование адреса операнда производится в зависимости от типа адресации. В зависимости от кода операции, признак нулевого результата проверяется на соответствие с нулем или единицей. Если проверка показала совпадение, реализуется переход – счетчику команд присваивается значение сформированного адреса. Новый командный цикл изменит последовательный ход программы. Обработка прерываний Контроллер прерывания устанавливает линию прерывания INT на системной шине. Когда центральный процессор готов к обработке прерывания он устанавливает символ подтверждения прерывания на шине INTA для внешнего устройства. Считывается вектор прерывания по соответствующему адресу таблицы прерываний. Центральный процессор удаляет вектор прерывания с шины. Центральный процессор помещает в стек счетчик команд, значения системных регистров, необходимую служебную информацию. Определяется местонахождение нового счетчика команд, используя вектор прерывания в качестве индекса в таблице памяти. Новый счетчик команд указывает на начало программы обслуживания прерываний для устройства, вызвавшего прерывание. После обработки прерывания восстанавливаются все сохраненные регистры. Центральный процессор возвращается в то состояние, в котором он находился до прерывания. После этого процессор продолжает работу с того места, в котором он остановился. 2.2.10. Разработка алгоритмов выполнения |