3_ЦАП_АЦП. Лекция 3 Цифроаналоговый и аналоговоцифровой преобразователи

Скачать 93.5 Kb. Скачать 93.5 Kb.

|

|

ЦСУА 3.1 Л Е К Ц И Я 3 Цифро-аналоговый и аналогово-цифровой преобразователи. Общепринятая аббревиатура ЦАП и АЦП. В англоязычной литературе применяются термины DAC и ADC. Цифро-аналоговые преобразователи служат для преобразования информации из цифровой формы в аналоговый сигнал. ЦАП широко применяется в различных устройствах автоматики для связи цифровых ЭВМ с аналоговыми элементами и системами. ЦАП в основном строятся по двум принципам:

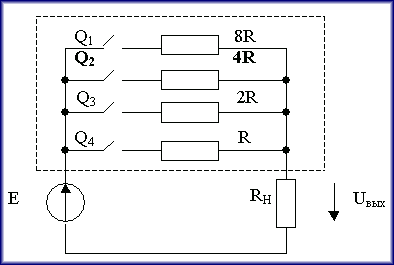

Принцип работы взвешивающего ЦАП состоит в суммировании аналоговых сигналов, пропорциональных весам разрядов входного цифрового кода, с коэффициентами, равными нулю или единице в зависимости от значения соответствующего разряда кода. ЦАП преобразует цифровой двоичный код Q4Q3Q2Q1 в аналоговую величину, обычно напряжение Uвых.. Каждый разряд двоичного кода имеет определенный вес i-го разряда вдвое больше, чем вес (i-1)-го. Работу ЦАП можно описать следующей формулой: Uвых=e*(Q1 1+Q2*2+Q3*4+Q4*8+…), где e - напряжение, соответствующее весу младшего разряда, Qi - значение i -го разряда двоичного кода (0 или 1). Например, числу 1001 соответствует Uвых=е*(1*1+0*2+0*4+1*8)=9*e.  ЦСУА 3.2 Упрощенная схема реализации ЦАП представлена на рис1. В схеме i – й ключ замкнут при Qi=1, при Qi=0 – разомкнут. Резисторы подобраны таким образом, что R>>Rн. Принцип работы АЦП состоит в измерении уровня входного сигнала и выдаче результата в цифровой форме. В результате работы АЦП непрерывный аналоговый сигнал превращается в импульсный, с одновременным измерением амплитуды каждого импульса. Внутренний ЦАП преобразует цифровое значение амплитуды в импульсы напряжения или тока нужной величины, которые расположенный за ним интегратор (аналоговый фильтр) превращает в непрерывный аналоговый сигнал. Для правильной работы АЦП входной сигнал не должен изменяться в течение времени преобразования, для чего на его входе обычно помещается схема выборки-хранения, фиксирующая мгновенный уровень сигнала и сохраняющая его в течение всего времени преобразования. На выходе АЦП также может устанавливаться подобная схема, подавляющая влияние переходных процессов внутри АЦП на параметры выходного сигнала В основном применяется три типа АЦП:

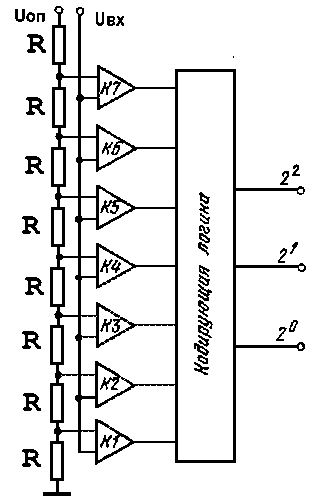

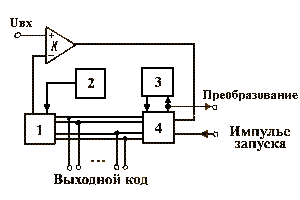

Краткое описание принципа работы параллельных АЦП. Преобразователи этого типа осуществляют одновременно квантование сигнала с помощью набора компараторов, включенных параллельно источнику сигнала (см. рис.). Пороговые уровни компараторов установлены с помощью резистивного делителя в соответствии с используемой шкалой квантования. В таком АЦП количество компараторов равно 2N--1, где N - разрядность цифрового кода (для восьмиразрядного - 255). При подаче на такой набор компараторов исходного сигнала на выходах последних будет иметь место проквантованный сигнал, представленный в унитарном коде. Для преобразования этого кода в двоичной используются логические схемы, называемые обычно кодирующей логикой. Такая чрезвычайно простая структура параллельных АЦП делает их самыми быстрыми из известных преобразователей и позволяет достигать частот преобразования 100...200 МГц. Однако их объем приблизительно удваивается с каждым новым разрядом, что в общем ограничивает их число. Обычно оно не превышает 6... 8. В этом типе кодирующей логики используется непосредственный переход от унитарного кода, имеющего место на выходе компараторов, к двоичному.  Структурная схема 3-разрядного параллельного АЦП Пример: Максимальное входное напряжение 10В должно соответствовать коду «5» на выходе АЦП. Тогда требуемое значение опорного напряжения может быть найдено из соотношения:  , откуда , откуда Краткое описание принципа работы последовательных АЦП. Преобразователь этого типа является наиболее распространенным вариантом последовательных АЦП с двоично-взвешенными приближениями (см. рис.). В основе работы этого класса преобразователей лежит принцип последовательного сравнения измеряемой величины с 1/2, 1/4, 1/8 и т.д. от возможного максимального значения ее. Это позволяет для m-разрядного АЦП выполнить весь процесс преобразования за m последовательных шагов приближения (итераций) и позволяет получить с помощью таких АЦП в зависимости от числа используемых разрядов до 105-106 преобразований в секунду. В то же время статическая погрешность этого типа преобразователей, определяемая в основном используемым в нем ЦАП, может быть очень малой, что позволяет реализовать разрешающую способность до 16 двоичных разрядов.   Сигнал готовности данных Структурная схема АЦП последовательных приближений: 1 - ЦАП; 2 - источник опорного напряжения; 3 - генератор тактовых импульсов; 4 - программное устройство управления и счетчик. ЦСУА 3.4 Этот преобразователь состоит из компаратора, счетчика и ЦАП. На один вход компаратора поступает входной сигнал, а на другой — сигнал обратной связи с ЦАП. Работа преобразователя начинается с прихода импульса запуска, который включает накопительный счетчик. Выходной код последнего подается на ЦАП, осуществляющий его преобразование в напряжение обратной связи. Процесс преобразования продолжается до тех пор, пока напряжение обратной связи сравняется с входными напряжениями и сработает компаратор, который своим выходным сигналом прекратит поступление счетных импульсов на счетчик и осуществит считывание с него выходного кода, представляющего цифровой эквивалент входного напряжения в момент окончания преобразования Вопросы программирования АЦП и ЦАПМикропроцессорный тренажер, изучаемый в данном курсе и используемый при проведении лабораторных работ, снабжен многофункциональной платой 5710 производства американской фирмы Octagon Systems. Состав платы 5710. Плата 5710 содержит два канала аналогового вывода (два 12-ти разрядных АЦП DAC813 производства фирмы Burr-Brown), 16 однопроводных или 8 дифференциальных каналов аналогового ввода, обеспечиваемые одной 12-ти разрядной микросхемой АЦП последовательного типа AD574 фирмы Analog Devices, и коммутатором аналоговых сигналов. Кроме того, плата снабжена микросхемой таймера – счетчика Intel 82C54, и микросхемой программируемого параллельного интерфейса 82С55. Одна такая плата оборудована всем необходимым для построения современной цифровой системы управления, например, электроприводом прокатного стана. Сначала рассмотрим программирование ЦАП. . Последовательность действий должна быть следующей.

Для диапазона выводимых ЦАП значений аналогового сигнала 5В, таблица соответствия входных и выходных значений имеет вид:

Для того, чтобы сформировать на выходе ЦАП напряжение V, лежащее в диапазоне 5В, необходимо воспользоваться следующей формулой: Пример. Для получения на выходе ЦАП напряжения V=--2.75 В, необходимо на ЦАП выдать код Для диапазона выводимых ЦАП значений аналогового сигнала 0, +10В, таблица соответствия входных и выходных значений имеет вид:

Для того, чтобы сформировать на выходе ЦАП напряжение V, лежащее в диапазоне 0, +10В, необходимо воспользоваться следующей формулой: ЦСУА 3.5 Пример. Для получения на выходе ЦАП напряжения V=-+2.75 В, необходимо на ЦАП выдать код

Дело в том, что хотя разрядность ЦАПа – 12, но за один раз записать в регистры ЦАПа двенадцатиразрядное число нельзя, потому что разрядность шины данных у модуля 5710 – 8. Делается это так. Необходимо подготовленный Code разделить без остатка на 256 (девятиразрядное число). Это и будет MSB. Затем необходимо найти остаток от деления Code на 256 – это и будет LSB. Пример. Для рассмотренного выше 1 случая Code=922. Это число при делении без остатка на 256 дает 3. Остаток от деления составит Таким образом, получаем MSB=3, LSB=154. Пример. Для рассмотренного выше 2 случая Code=1126. Это число при делении без остатка на 256 дает 4. Остаток от деления составит 1126-4*256=102. Таким образом, получаем MSB=4, LSB=102.

Таблица адресов регистров микросхем ЦАП:

Где BASE=0x110 - базовый адрес платы 5710. Программирование АЦП Алгоритм действий при программировании АЦП такова.

Адресом регистра выбора номера канала в плате 5710 является BASE+0x09.

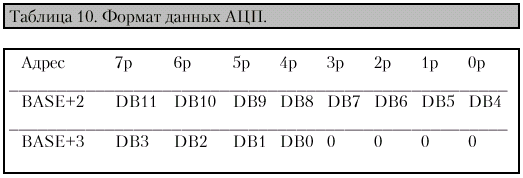

ЦСУА 3.6 Чтение и компоновка данных. Как и в случае с ЦАП, мы не сможем за одно обращение считать двенадцатиразрядный код. Чтение данных производится поочередно за две операции. Сначала по адресу BASE+0x02 считываются данные с 4 по 11-й бит (старший байт, или MSB). Затем по адресу BASE+0x03 считываются данные с 0 по 3-й бит (младший полубайт, или LSB). При этом физически биты с 0 по 3-й физически расположены с 4 по 7 в считываемом слове, см. таблицу.  Таким образом, данные размещаются по двум независимым адресам и должны быть программным путем скомбинированы для достижения 12-ти разрядного результата. Другими словами, биты MSB c 0 по 7-й должны стать битами с 4-го по 11-й в результирующем 12-ти разрядном числе. А биты LSB c 4-го по 7-й должны стать битами с 0-го по 3-й. Делать это можно операциями циклического сдвига вправо и влево. Пример на языке С: Code=((MSB<<4)+(LSB>>4)).

Считанный код представляет собой 12-ти разрядное число в диапазоне от 0 до 4095. Таблица соответствия дискретных кодов аналоговым значениям приведена выше. Для получения значения в вольтах можно пользоваться формулой, обратной вышеприведенной для ЦАП: Для случая Code=922 получим: Для случая Code=1126 получим: |