7-15схтabлек. Лекция. Комбинациялы типті цифрлы рылылар. Екілік сумматорлар (осыштар). Бір разрядты сумматорлар (осыштар) Кп разрядты сумматорлар (осыштар). Арифметикалы логикалы рылылар

Скачать 0.85 Mb. Скачать 0.85 Mb.

|

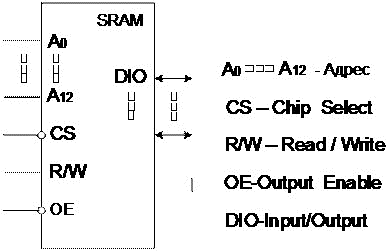

6.3.3 Статикалық оперативті сақтау құрылысының сыртқы ұйымдастыруы және уқыт диаграммалары.Статикалық оперативті құрлғылар номенклатурасында микросхемалар бір разрядты және (словарлы) сөздікпен ұйымдастырылған микросхемалармен берілген. Статикалық сақтау құрылғысының сыртқы ұйымдастыру 64 Кбита (8К×8) сиымдылығы 68 суретте көрсетілген. В номенклатуре статических ЗУ представлены микросхемы с одноразрядной и словарной организацией. Внешняя организация статического ЗУ ёмкостью 64 Кбита (8К×8) показана на рисунке 68.Еске сақтау құрылғысының мүмкін болған сигналдарының жиынтығы  68сурет Статикалық еске сақтау құрылғысының сыртқы ұйымдастырудың мысалы. A — адресі. Разрядтығы n еске сақтау құрылғысының ұяшықтарының санымен анықталады, яғни сақтау құрылғысында максимал мүмкін сөздердің санымен N=2n,ал n=log2N. Мысалы, ЕСҚ сиымдылығы 8К сөз тең болса, сөзбен білдіретін оның13-разрядты адрестері болады: A=a12a11a10…a0,ал сиымдылығы 64Ксөздің-16-разрядты адрестері: A=a15a14a13…a0 DI және DO — кіріс және шығыс шиналары; m — олардың разрядтығы. Қарастырылған мысалда DIжәне DO жалпы бір DIO шинаға біріктірілген. CS— Кристалдың таңдауы: берілген микросхемаға жұмыс істеуге рұқсат ете ме немесе тиым салама. R/W — оқу немесе жазу. R/W=1— «оқу», R/W=0 — «жазу». CE — Chip Enable — шығысқа рұқсат ету, оның пассивті күйі 9кесте ЕСҚ жұмыс істеу режимінің берілуі

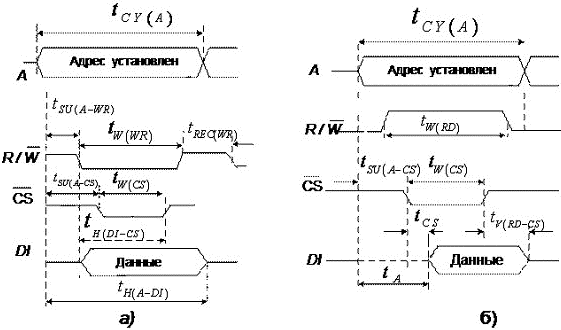

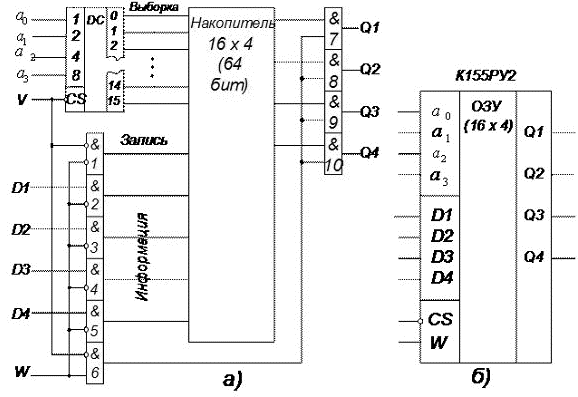

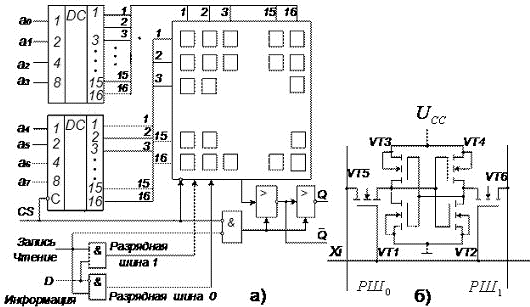

69сурет Үрдістердің уақыт диаграммалары. Жазу а)және оқу б)статикалық еске сақтау құрылғысында Функционирование ЗУ во времени регламентируется временными диаграммами, устанавливаемые изготовителями. В основу кладутся определённые требования. Например, чтобы исключить возможность обращения к другой ячейке, рекомендуется подавать адрес раньше, чем другие сигналы, с опережением на время его декодирования. Адрес должен держаться в течение всего цикла обращения к памяти. Затем следует подать сигналы, определяющие направление передачи данных и, если предполагается запись, то записываемые данные, а также сигнал выборки кристалла. Среди этих сигналов будет и стробирующий, т.е. выделяющий временной интервал непосредственного выполнения действия. Таким сигналом для разных ЗУ может служить как сигнал R/W, так и сигнал Если задана операция чтения, то дополнительно подаётся сигнал разрешения выхода. После подачи указанных выше сигналов ЗУ готовит данные для чтения, что требует определённого времени. По заднему фронту сигнала R, положение которого должно обеспечивать установление правильных данных на выходе ЗУ, данные считываются из ЗУ. Требования к взаимному расположению двух сигналов (например, A и B) задаётся временами предустановки, доступа, удержания и сохранения. Время предустановки сигнала A относительно сигнала B: tSU(A–B) — это интервал между началами обоих сигналов. 69 а, б суретте tSU(A–CS) және tSU(A–WR) белгіленген.. Бұл CS және WR сигналдарын алдын ала адреске байланысты орнату уақыты. Жету уақыты A символымен белгіленеді(Access деген сөзден)-басқаратын сигналдардың пайда болуынан шығыста ақпараттық сигналдың пайда болуының арасындағы уақыт интервалы. Адреске байланысты жету уақыты tA(A) белгілейді, кейде жәй tAдейді.. Осыған ұқсас, CS сигналына байланысты жету уақыты tA(CS) тең, оны tCSбелгілейді. Ұстау уақыты— А сигналының басталуымен және В сигналының аяқталуының арасындағы уақыт интервалы. tH(A–B). tH(A–DI) оқу циклы. Адресті, кірістегі берілгендерді алғанша ұстап тұратын уақыт. Сақтау уақыты tV(A–B) —А сигналының аяқталуымен В сигналының аяқталуының арасындағы уақыт интервалы. 69,б суретте «кристаллдарды таңдау» (немесе оқу сигналы)сигналдарына байлынысты берілгендерді сақтау уақыты.Бұл интервал ақпаратты оқығанда қате болу ықтималдығын азайту үшін қолданады. Сигналдың ұзақтығы tWбелгіленеді.(индекс Width-ені сөзден). 15.1 ОЕСҚ микросхемаларыСоңғы уақытта КМОП технолгиясы бойынша дайындалған статикалық ОЕСҚ интенсивті дамып келе жатыр.Технологиялық үрдістің топологиялық нормалары азайған сайын өзінің қасиетерін сақтай отырып тезәсерлігі жоғары болып бара жатыр В последнее время наиболее интенсивно развиваются статические ОЗУ выполненные по технологии КМОП, которые по мере уменьшения топологических норм технологического процесса приобретают всё более высокое быстродействие при сохранении своих традиционных преимуществ. МС К155РУ2 —ТТЛ технологиясымен дайындалған МС, ұйымы 16×4=64 (70,асурет) және 2D құрылымы бар ОЕСҚ .ЭЖ(электрондық жады) массиві 16 жолдан және 4 бағанадан тұратын матрица Әр бағанның элементтері берілгенің ішкі разрядтық сызығымен қосылған және барлық сөздердің бір атты биттерін сақтайды. Жады ұяшығы жалпы сигналмен басқарылатын 4 тригерден тұрады. CS=0 тең болғанда шығарылып қойған адреске сәйкес бір ұяшығы жұмыстық күйге өтеді де, оның сигналдары И(7…10) элементтерінің кірісіне түседі. CS=1 тең болғанда дешифратордың барлық шығысында төменгі деңгейлер болады да , барлық триггерлер жинақтауыштың кіріс шиналарынан ажыратылады. При CS=1 на всех выходах дешифратора низкие уровни и, следовательно, все триггеры отключены от входных шин накопителя. CS=0 және W=0 болғанда таңдап алған ұяшыққа D1…D4 кірістерінен ақпараттық сигналдар түседі және И1 элементінде «жазу» сигналы шығарылады. D1…D4кірістерінен кіріс а При CS=0 и W=0 на выбранную ячейку поступают информационные сигналы с входов D1…D4 и элементом И1вырабатывается сигнал «Запись». Входная информация со входов D1…D4 записывается в ячейку. При CS=0 и W=1 формируется сигнал «Чтение» и информация из выбранной ячейки читается с выходов Q1…Q4.  70 сурет МС К155РУ2: а) Құрылымдық сұлба, б) шарты белгісі Микросхемы К176РУ2, К561РУ2 256×1 ұйымдастыруымен КМОП технологиясы бойынша дайындалған және 3D құрылымымен еске сақтау құрылғысы (71,а сурет).  71сурет Микросхема К176РУ2: а)Құрылымдық сұлба; б) Жады элементі. МС К176РУ2 құрлымдық сұлбасы 71,а суретте келтірілген.Сұлба екі дешифратордан тұрады: DC бағаны бар, DC жолы бар.Дешифраторлардың 8разрядтан тұратын адрестен 4 разряды берілетін 4 кірісі баржәне 16 шығысы бар.Әр бір жады ұяшығы бағанамен жолдадың қиылысында тұратын болғандықтан, екі дешифратор 16×16=256 жады элементіне қарауға мүмкіндік береді. Структурная схема МС К176РУ2 приведена на рисунке 71,а. Схема содержит два дешифратора: DC столбцов и DC строк. Дешифраторы имеют по 4 входа, на которые подаётся по 4 разряда из общего 8-разрядного адреса, и по 16 выходов. Каждая ячейка памяти находится на пересечении строки и столбца, поэтому два дешифратора обеспечивают обращение к 16×16=256 элементам памяти. Жадының әр элементі статикалық RS-триггерболып саналады.(71,б сурет). Тригердің екі парафазалық кіріс/шығысы бар. РШ0 және РШ1 разрядты шиналармен тригер VT5 және VT6 кілтері арқылы қосылған. Парафазалық пішінде ақпарат РШ1өзінің мәнінің тура түрінде, ал РШ0 инверсті түрде разрядтық шиналар арқылы тригерге жазылар кезде беріледі де , ал оқылған кезде басқа жаққа бұрылады Каждый элемент памяти представляет собой статический RS-триггер (рисунок 71,б). Триггер имеет два парафазных входа/выхода. С разрядными шинами РШ0 и РШ1 триггер соединён через ключи VT5 и VT6. По разрядным шинам к триггеру подводится при записи и отводится при считывании информация в парафазной форме представления по РШ1 своим прямым значением, а по РШ0 — инверсным. В режимах «Запись» и «Чтение» при возбуждении строки сигналом выборки Xi=1, снимаемым с дешифратора адреса строк, ключи VT5 и VT6 открываются и подключают триггер к разрядным шинам. При Xi=0 ключи закрыты и триггер отключён (изолирован) шин, а информация в них хранится. При считывании информации ключи подключают элемент памяти к разрядным шинам, они принимают потенциалы выходов триггера и через устройство ввода/вывода передают их на выход микросхемы. РШ охватывают все элементы одного столбца, а переходит в активное состояние только один ЭП, соответствующий выбранной строке. Из него и считывается информация. СНГ шығарылған микросхемалар сериясында жақсы дамыған болып, КМОП технологиясы мен дайындалған ақпараттық сиымдылығы 1024×1 (К537РУ1)ден 8192×8 (К537РУ17)дейін және К537 ақпараттық сиымдылығы 1024×1 (К537РУ1) ден 8192×8 (К537РУ17)дейін және n-МОП технологиясымен n-МОП технологиясымен дайындалған К132 ақпараттық сиымдылығы 1024×1 (К132РУ2)ден 65536×1 (К132РУ10)дейін. Әр түрлі технологиямен жасалған ОЕСҚ негізгі параметрлері 10 кестеде келтірілген. 10 кесте ОЕСҚ негізгі параметрлерінің мәні

Список использованных источников1 Быстров Ю.А. Электронные цепи и микросхемотехника: Учебник. – М.: Высш, шк., 2002. – 384 с. 2 Гусев В. Г. Электротехника и микропроцессорная техника: Учебник для вузов. – М.: Высшая школа, 2006. – 800 с. 3 Нарышкин А. К. Цифровые устройства и микропроцессоры: Учеб.пособие для студ. Высш. Учеб. Заведений – М.: Издательский центр «Академия» , 2006. – 320 с. 4 Новиков Ю. В. Введение в цифровую схемотехнику – М.: Интернет – Университет Информационных Технологий; БИНОМ. Лаборатория знаний, 2007. – 373 с. 5 Угрюмов Е. П. Цифровая схемотехника. – СПб. : БХВ – Петербург, 2001. - 528 с. 6 Цифровые и аналоговые интегральные микросхемы: Справочник / С. В. Якубовский, Л. И. Ниссельсон, В. И. Кулешова и др.; Под редакцией С. В. Якубовского, — М. : Радио и связь, 1989. – 496 с. Лит.:Алексенко А. Г., Основы микросхемотехники, М., 1971; Поспелов Д. А., Логические методы анализа и синтеза схем, 3 изд., М., 1974. |