7-15схтabлек. Лекция. Комбинациялы типті цифрлы рылылар. Екілік сумматорлар (осыштар). Бір разрядты сумматорлар (осыштар) Кп разрядты сумматорлар (осыштар). Арифметикалы логикалы рылылар

Скачать 0.85 Mb. Скачать 0.85 Mb.

|

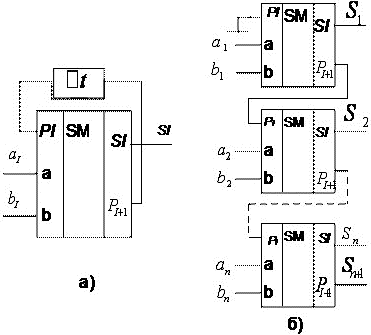

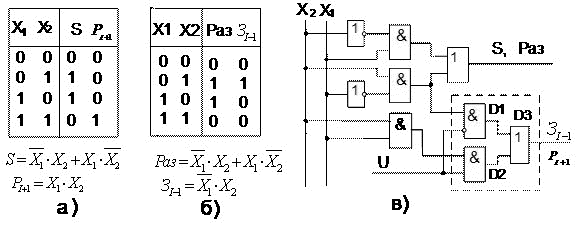

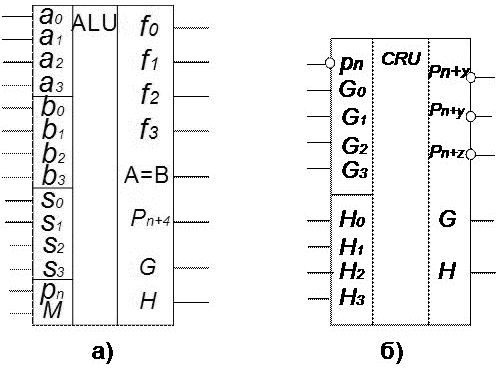

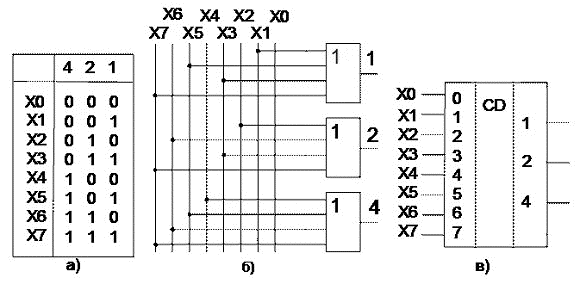

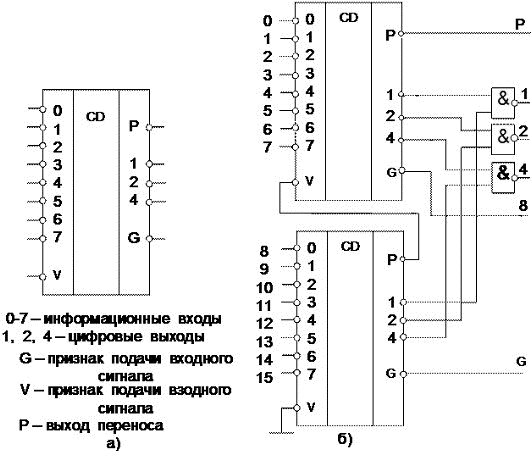

7.1.2 Көпразрядты сумматорлар.Көпразрядты сумматорлар жасау әдістері:-тізбектеп қосу; -тізбектеп тасымалдау параллель қосумен; -параллель тасымалдау параллель қосумен.  24сурет. Көпразрядты сандарды қосу:а) -тізбектеп; б)параллель тізбектеп тасымалдаумен. Тізбектеп қосу үшін барлық разрядтарға ортақ бір сумматор қолдынылады. 24,а сурет. Операндтар аI және bI кірісі арқылы синхронды кіші разрядтан бастап енгізілу керек. Кідірту тізбегі тасымалдауимпульсінің PI+1бір тактыға кететін уақыт ұзақтығындай сақтайды, яғнинымен қосылатын келесі разрядтың қосындылар жұбы келгенше.Кідіртуді D-триггер орныдайды. Тізбектеп қосқанда, барлық разрядқа жалпы бір суматор қолдынылады.(24,а сурет) Кіші разрядтан бастап синхронды аI жәнеbI кірістері арқылы суматорға операндтар кіргізілу керек. Кідірту тізбегі тасмалдау импульсін PI+1.бір тактылық уақыт ішінде сақтайды,яғни онымен қосылатын келесі разрядтың қосындылар жұбы келгенше.Кідіртуді D-триггер орындайды. Қосу нәтижесі кіші разрядтан бастап тізбектей саналады.Операндтарды сақтау ,кіргізу үшін және Қосындыларды жазу үшін кәдімгі ығыстыру регистрі қолдынылады. Бұл әдістің жетістілігі –аз аппараты шығындар.Жетістілігі біруақытта екі жұп қосынды қосылатындығынан –жылдам әсер етуі баяулайды. Тізбектеп тасмалдайтын параллель сумматор сұлбасы 24,б).суреттте көрсетілген. Суматорлардың саны сандардың разрядтар санына тең.Әр сумматордың тасмалдау шығуы PI+1келесі үлкен разрядтың кірсімен жалғанады.Мұнда еш бір тасмалдау сигналы түспейді,сондықтан, кіші разрядтың тасмалдау кірісіне «0» потенциалы тұрғызылады. aI және bI қосындылары барлық разрядтары бір уақытта қосылады, ал PI тасмалдау Алғы разрядтағы қосу амалы орындалғаннан кейін түседі. Сигнал бүкіл суматорлар тізбегі бойымен тарағанша, жоғарғы разрядтың шығысында тасмалдау сигналы қалыптаспайды. Мұндай сумматорлардың тезәсерлігі тасмалдау кедергісімен шектеледі. Параллель тасмалдауы бар параллель сумматорларПараллель тасмалдауды ұйымдастыру үшін арнайы арналған түйіндер-тез тасмалдау болктары қолдынылады. Жеделдетіп тасмалдау принципін мынада: әр бір екі разрядқа қосымша екі сигнал арналған: G —тасмалдау құру және H — тасмалдау таралуы. GI = aI·bI HI = aI + bI GI=1болған жағдайды,яғни aI=bI=1, бұл берілген i-разрядта келесі жоғарғы разрядқаPI+1 алмасу сигналы алдынғы разрядтағы функциялардың қосындысына тәуелсіз қалыптасады . Егерде aI немесе bI «1»тең болса ,яғни HI=1 тең болса,келесі разрядқа бастапқы разрядтан алмасу сигналы болғанда ғана көшірледі. Егерде GI=1,яғни aI=bI=1, алдынғы разрядтарға қосындылардың қалыптасуына тәуелсіз, i-разрядта келесі жоғарғы разрядқа апаратын PI+1 тасмалдау сигналы қалыптастырылады. Егерде қосындылардың біреуі aI немесе bI ,«1» тең болса, яғниHI=1. Келесі разрядқа тасмалдау тек қана сигал болғанда ғана іске асырылады. Егерде HI=HI–1=1 және PI алдынғы i-ші разрядтан алмасу сигналы болса онда көшіру i+2 разрядқа істеледі Жалпы жағдайда үдемелі ауысу үрдісін қалыптастыру мына теңдеумен беріледі: PI+1 = GI + HI·GI–1 + HI·HI–1·GI–2 + … + HI·HI–1·…·H2·H1·P1 Тез тасмалдау блоктары интегралдық түрде орындалған жеке микросхема немесе сумматор сұлбасымен немесе бір микросхемада арифметика-логикалық құрылғы түрде шығарылады. 7.1.3 арифметика-логикалық құрылғы Негізгі арифметикалық амалдарға қосу және алу жатады. Алу амалдарын қосу әдісмен орындау үшін кері және қосымша кодтар жасалған. Алу амалын орындау үшін, азайтқышты қосымша кодқа өткізіп бірінші қосылғышқа қосу керек.Алынған нәтижені қосымша кодта көрсетілген. Оны сосын тікелей кодқа өткізу керек.Оң сандардың тікелей және кері кодтары бірдей.Теріс сандарды косымша кодқа айналдырғанда,барлық разрядтарын тура кодтың инверсия жасап және кіші разрядына бірді қосу керек. Қосымша кодты тікелей кодқа айналдырғанда,алынған нәтижені инверсия жасап кіші разрядқа бірдіі қосу керек Сонымен қосу әдісімен алу амалы қосымша уақыт шығымын қажет етеді және есептеу құрлғылардың жылдамдығын азайтады. ЭЕМ жылдамдығын өсіру үшін , арифметикалық және логикалық амалдарды түрлендірмей сандардың тікелей кодтарымен орындауды қамтамасыз ететін, құрамдастырылған арифметико-логикалық құрылғылар істелген және қолдынылады. Қосу және алу амалдарын орындау үшін , бір разрядты арифметикалық құрылғылардың істеу әдістері 25 суретте көрсетілген. Қосу және алу амалдарының логикалық өрнектерін салыстырғанда, қосу(25,а сурет) және алу(25,б сурет) амалдарының өрнектері бір бірне сәйкес келеді,ал қарызға алу өрнегі қосу және алу амалдарының бөлігі болып табылады.  25 сурет.Ақиқат кестсі және құрылым формулалары қосу а),алу б) және бір разрядты АЛҚ сұлбасы в). Сонымен алу амалын орындау үшін қосымша сигналдар алудың қажетілігі жоқ,қосымша аппаратық шығымдар керек болмайды.операцияның коды сәйкес көшіру және қарызға алу сигналдарын комутациялауын қамтамасыз өткізу қажет. 25, в) суретте U кернеуінен келетін екі әр полярлы сигналмен басқару ісін орындайтын орындайтын басқару құрылғысы ролін екі клапанды қарапайым АЛҚ сұлбасы келтірілген.. 25суреттте сұлбаның бұл бөлігі пунктир сызықпен белгіленген. U=0 болғанда алу амалы орындалады, ал U=1 — қосу амалы орындалады. 25, в) суретінде Басқару кернеуінен U әрполярлы сигналдармен басқарылатын Көпразрядты АЛҚ интегралдық микросұлба түрінде шығарылады немесе процессордың негізі болып оның құрамына кіреді. МС 564ИП3 (26,а сурет) —бұл 16 арифметикалық және 16 логикалық операциялар жасайтын төртразрядты параллель АЛҚ  26сурет. 4-разрядты АЛУ 564ИП3 сұлбасы а) 564ИП4 тездетіп тасмалдау сұлбасы б). A(а0–а3) — бірінші операнд, B(b0–b3) — екінші операнд, S(s0–s3) — операция коды — 4 разрядты. Егер M=0, онда арифметикалық амалдар орындалады: 24=16,M=1 болғанда логикалық операциялар орындалады: 24=16. Барлығы 16+16=32 операция. F(f0–f3) —операция нәтижесі. A=B шығысында «1»пайда болады ,егер азайту амалын орындағанда операцияның нәтижесі «0»тең болса , яғни A=B. АЛҚ параллель типті болғандықтан оның G генерация шығысыжәне H тасмалдау таралуы бар. Pn және Рn+ -шығатын және кіретінтасмалдар. Тізбектей тасмалдайтын параллель сумматордағы дай, МС АЛҚ өңдейтін сөздердің разрядтығын үлкейту үшін оны тізбектеп қосуға болады.Бұл жағдайда операция орындау уақыты өседі.Бұл уақытты азайту үшін, АЛҚ жылдам әсер етуін өсіру МС үшін, 564ИП4 жылдам тасмалдайтын сұлбаны қолдану керек. 26, б)сурет. Төрт МС АЛҚ және бір жылдам тасмалдайтын МС 16 разядты толық параллель АЛҚалуға болады.Оның қосу уақыты бір микросұлбаның қосу уақытына тең. 8. Кодтайтын және декодтайтын құрылғылар. Шифраторлар. Дешифраторлар (декодерлер). 8.1 Шифраторылар Шифратор (кодер) –кірісіне берілген (кіретін) басқаратын сигналдарды n-разрядты екілік кодқа айналдыруға арналған функциональды түйіншік. Сонымен қатар, мұндай сигналдар немесе командалар ондық сандар болуы мүмкін, мысалы шифратордың көмегімен екілік кодқа түрленетін командының номері . Мысал ретінде 3-разрядты шифратордың сұлбасын жасайық. Алдымен сигналдың коды екілік кодпен берілген,кодтар кестесін (ақиқат кестесін) сызайық.(27,а сурет) .НЕМЕСЕ элементерімен іске асырылған сұлба 27,б суретінде көрсетілген.  27сурет. 3-разрядты ширатордың кодтар кестесі. а), оның функциональдық сұлбасы б) және ШГБ в). Жалпы жағдайда ,екілік кодты қолданғанда 2n кіріс сигналдарын кодтауға болады. Егерде кірісінің біреуіне де жалпы жағдайда кіріс сигналы берілмейтін болса,онда жоғарғыда қаралған сұлбада «000» шығу коды X0 кіріске сигнал бергенде баршығыстар болады. X0 сигналын бірмағаналы идентификация жасау үшін, интегралдық сұлбаларда тағы бір сигнал қалыптасады, ол кіріс сигналдың берілуінің белгісі,бұл басқа мақсаттарда да қолданылады.28 суретте 3 разрядты басым (приортетті) 8 кірісі бар шифратордың ШГБ(шарты графикалық белгісі) көрсетілген  28сурет. 3-разрядты басым (приоритетті) шифратор К555ИВ1 а) және екі МС жалғағаны б) Кез келген кірісіне сигнал берілгенде, G=1, P=0 болып тағайындаладыда, ал цифрлық шығыстарында-сигнал берілген кірістің номерінің екілік коды шығады. Егерде сигнал біруақытта екі немесе бірнеше кіріске берілсе,онда шығысында үлкен номері бар кірістің коды тағайындалады.Осыдан шифратордың аты басым (приоритетті) деп аталады. Егер 0…7 кірістерінің біріне сигнал (лог.«0») берілсе, DD3 шығыстарында тура кодтың кіші разрядтары пайда болады, ал G DD1 шығысында- лог. «0», егерде 8…15 кірістерінің біріне лог.«0» берілсе,онда Р кірісінен берілген лог. «1» DD2 DD1-ің жұмыс істеуіне тиым салады.Бұл жағдайда DD3кіші разрядтары DD2,микросхемамен анықталады, ал 8 крістің шығысында шығыс коды лог. «1» болады. Сонымен 1, 2, 4, 8шығысынан кіріс сигнал берілген кірістің номеріне сәйкес тура код алуға болады |