7-15схтabлек. Лекция. Комбинациялы типті цифрлы рылылар. Екілік сумматорлар (осыштар). Бір разрядты сумматорлар (осыштар) Кп разрядты сумматорлар (осыштар). Арифметикалы логикалы рылылар

Скачать 0.85 Mb. Скачать 0.85 Mb.

|

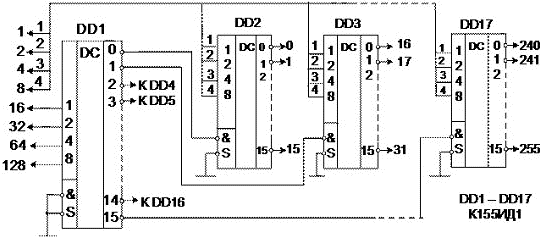

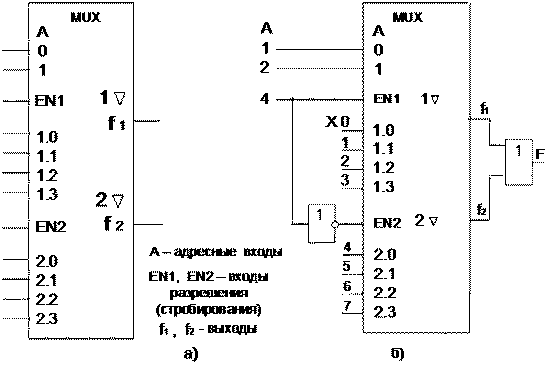

4.2.2 Дешифраторлар (декодерлар)n кірістің кіреберісіндегі кодқа тәуелді, тек қана өзінің 2n кірістерінің бірінде «лог. 1» (жоғарғы деңгейдегі дешифратор) немесе «лог. 1» (төменгі деңгейдегі дешифратор) сигналын тудыратын функционалдық түйіншік дешифратор деп аталады. Дешифратор — функциональный узел, вырабатывающий сигнал «лог. 1» (дешифратор высокого уровня) или сигнал «лог. 0» (дешифратор низкого уровня) только на одном из своих 2n выходах в зависимости от кода двоичного числа на n входах.  29 сурет. Дешифратор: а)ақиқат кестесі; б) – функциональдық сұлба. Дешифраторлар басқару құрылғыларында кеңінен қолдынылады.Олар кірісіндегі сигналға сәйкес қандай бірорындаушы құрылғыға әсер ететін басқаратын сигнал қалыптастырады Дешифраторлардың интегральды микросхемаларды қосымша кірістерімен жасайды, мысалы рұқсат беретін кіріспен (стробтау). Стробтау оның жұмысын кірісіндегі цифрлық код өзгергенде өту үрдісі уақыт интервалында жұмысына тиым салып, кірісінде жалған сигналдардың пайда болдырмайды. ИД3 (30 сурет) микросхемасының 4адресті кірісі бар1,2,4,8 екілік кодының салмақтық коэффициенті бар, стробтайтын S екі инверсті кіріс,ЖӘНЕ мен біріктірген, және 0–15 дейін 16 инверсті кірісі бар. Егер стробтаудың екі кірісінде «лог. 0»,онда номері кіріс кодының ондық эквивалентіне сәйкес шығыста «лог. 0» болады.Егерде S стробтайтын кірістердің бірінде «лог. 1» болса, онда микросхемалардыңбарлық шығысында кірістерінің жағдайына байланысыз «лог. 1».қалыптасады.  Екі стробтау кірісінің барлығы микросхемалардың қолданылуының мұмкіндігін кеңейтеді. Бір инвертормен толықтырылған ИД3 екі микросхемадан 32 кірісі бар дешифратор(31сурет), жинауға болады, ал 17 микросхемадан-256 кірісі бар дешифраторды(32сурет).  32сурет. 256 шығысы бар дешифратор . Цифрлық сигналдардың коммуторлары. Мультиплексорлар. Дешифраторлар-демультиплексорлар. 9.1Мультиплексорлар n-адрестік кірісі, N=2nинформациялықкірісі,бір шығысы бар және N кіріс желісінен түсетін шығыс желісіне түсетін информацияны басқарылатын коммутация жасайтын функциональдық түйіншікті мультиплексор дейді. Белгілі кіріс желісін коммутациялау екілік адрестік кодына an-1,…a2,a1,a0сәйкес іске асырылады. Егерде адрестің коды n разрядты болса,әр бір N кіріс желісін шығыс желісін қосуды қамтамасыз ететін N=2nадрестік сигналдардың комбинацияларын әске асыруға болады.Мұндай мультиплексорды «N-нен бірге» аталады. Артық адрестік сигналдардың комбинациялары бар болса, кіріс желісініңкез келген N≤2n саны бар мультиплексор жасауға болады. Қарапайым жағдайда екі разрядты адрестық кодта(n=2)шығатын желілердің максималь саны N=2n=4 тең. Мультиплексордың ақиқат кестесі 33,асуретте көрсетілген.  33сурет.4:1 мультиплексорыа) ақиқат кестесі; б)функциональдық сұлбасы; в)шарты графикалық белгісі. Ақиқат кестесіне сәйкес жазылған мультиплексордың сипатама теңдеуі мына түрде жазылады: Мультиплексордың функциональдық сұлбасының құрамына екі инвертор, төрт «ЖӘНЕ»вентилі, және бір «НЕМЕСЕ» вентилі кіретіні алынған теңдеулерден білуге болады. Қазіргі уақытта өндіріс құрамына n=2,3 және 4 адресті кірісі бар мультиплексорлер кіретін МС сериясын шығарады. n=2 тең болғанда қабаталғантөртканалды(2n=4)мультиплексорлердің информациялық кірістердің сигналдарының саны 2n+2n=8.4 каналды қабаталғанстробтайтын К555КП12мультиплксордың шарты графикалық белгісі 34,а суретте келтірілген.  34сурет.Қосақталған 4-каналды мультиплексор К555КП12 а) және оның негіздегі 8-каналды мультиплексор б). Стробтау кірістері, k2n-информациалық кірістері бар,мұндағы k=2, 3, 4… тең , мультиплексорларды (коммутаторларды) істеуге қолдынылады.Сторбтауы бар,қосақталған 4-каналды 8:1 мультиплексордың сұлбасы 34,б суретте келтірілген. лог. «0» жәнелог. «1» сәйкес тұрақты деңгейді ақпараттық кірістерге берілсе, онда мультиплексордың шығысында кез келген өзіңе ұнаған басқаратын кодтың айнымалысының функциясын алуға болады.Бірақ бұл жағдайда іске асырылатын шығатын функцияның айнымалыларының саны басқаратын кодтың разрядына тең. Жалпы жағдайда ақпаратық кірістерге тұрақсыз логикалық деңгейлер беруге болады, сонда мультиплексордың шығысында айнымалысы көп логикалық функция іске асырылады. В общем случае на информационные входы можно подавать не постоянные логические уровни, тогда на выходе мультиплексора реализуется логическая функция с большим числом переменных. |