0_МПиИСТС_Все главы. Микропроцессоры и интерфейсные средства транспортных средств

Скачать 10.01 Mb. Скачать 10.01 Mb.

|

4.12 Контрольные вопросы и задания

- PUSH D; - MVI M, A6; - LXI H, 012E; - CALL 023D; - LDAX D; - CMA. 7. Как влияют команды пересылки на состояние регистра признаков? 8. Как выполняется команда MOV D, M? 9. Какая или какие из приведенных ниже мнемонических записей ошибочны: - MOV D, B4; - LHLD 01D6; - PUSH PSW; - PCHL; - POP C; - LDA B4; - STAX D. 10. Какая из команд MOV C,M и MOV D,E требует для своего выполнения больше времени и почему? 11. В каком случае после выполнения команды MOV H, L содержимое регистров H и L не изменится? 12 . Как выполняется команда SPHL? 13. Особенности выполнения команды POP PSW.

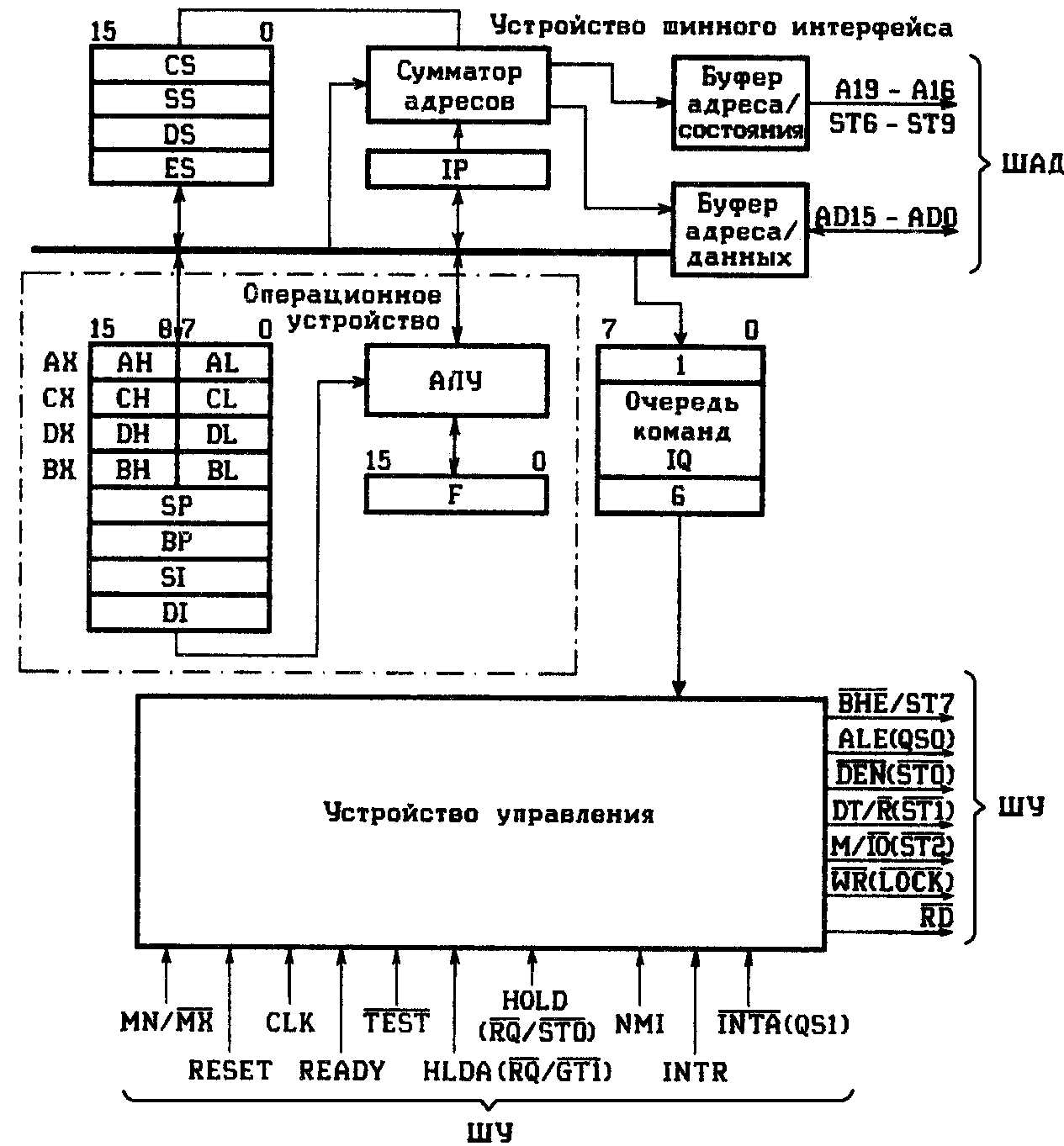

19. Перечислите логические команды МП КР580ВМ80А. 20. Перечислите арифметические команды МП КР580ВМ80А. 21. Как изменяются признаки при выполнении команды ADD? 22. Как изменяются признаки при выполнении команды SUB? 23. Как изменяются признаки при выполнении команды SBB? 24. Как изменяются признаки при выполнении команды ANA? 25. Как изменяются признаки при выполнении команд ORA и XRA? 26. В каких случаях может возникнуть переполнение разрядной сетки в командах сложения и вычитания? 27. Назовите признаки переполнения разрядной сетки. 28. Какая или какие из перечисленных ниже команд не относятся к группе арифметических и логических команд? - ANI 4D, - SBB M, - MVI A9, - XRA C, - ADC H, - CPI D4, - CMP E, - LXI B, - SUI 91. 29. Чем отличается выполнение команд сравнения и вычитания? 30. Куда всегда помещается результат выполнения логических команд, команд сложения и вычитания? 31. Определите результаты работы следующей команды: ADD E, при (A) = 7E, (E) = F2. 32. Определите результаты работы следующей команды: SUB L при (A) = 83, (L) = 5A. 33. Определите результаты работы следующих команд: ANA H, ORA H, XRA H при одних и тех же операндах. Глава 5. Микропроцессор К1810ВМ86 (Intel 8086)5.1. Устройство и работа микропроцессора Intel 8086 (K1810BM86)5.1.1. Структура микропроцессора Intel 8086Основные характеристики: -универсальный микропроцессор (МП); - системная магистраль имеет 3 шины (ША – 20 бит, ШД – 16 бит, ШУ), но выводы МП с частичным мультиплексированием (16 младших разрядов ША/Д соответствуют адресам/данным, 4 оставшихся старших разряда ША – сигналы состояния микропроцессора); - способен работать в 3-х режимах (обмен данными, ПДП, режим прерывания); - сегментная организация памяти (размер сегмента 64 Кбайт); - адресные пространства памяти и внешних устройств разделены; - основная форма представления чисел - двоичный дополнительный код с фиксированной запятой; работает с десятичными числами (не только ВСД код, но и ASCII код); - тактовая частота 4,44 МГц; - корпус 40-выводный DIP; - напряжение питания + 5 Вольт. Нововведением МП стало появление очереди байтов команд (6 байтов команд), а также параллельная работа блока сопряжения с шиной (устройства шинного интерфейса) и операционного устройства.

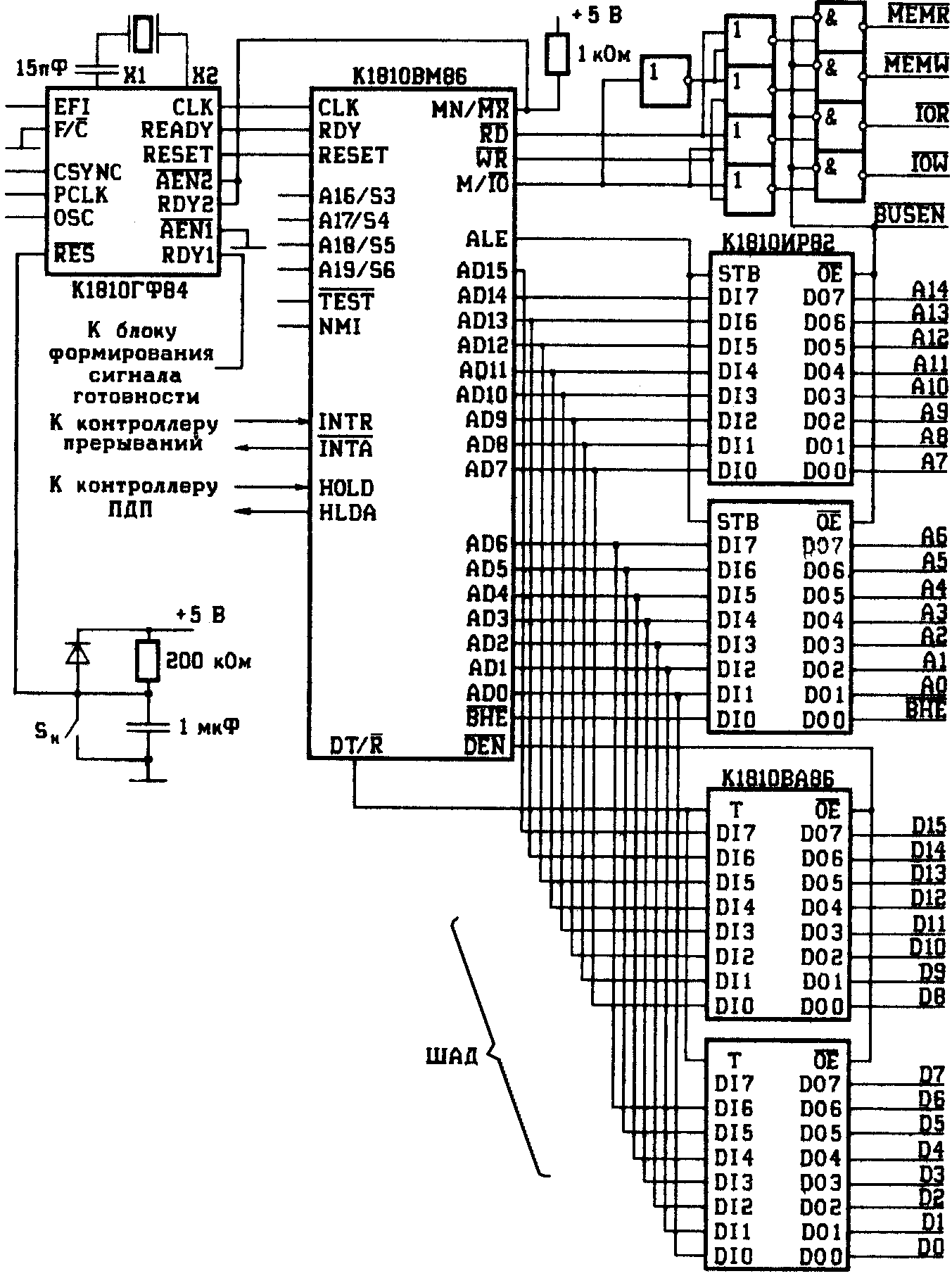

Микропроцессор содержит две основные части: операционное устройство и устройство шинного интерфейса. Оба устройства могут работать параллельно, что обеспечивает совмещение во времени процессов выборки и исполнения команд. Операционное устройство содержит регистры общего назначения, арифметико-логическое устройство (АЛУ), регистр флагов (F), блок управления и обеспечивает выполнение команд. Устройство шинного интерфейса содержит блок сегментных регистров, указатель команд (IP), сумматор адреса, очередь байтов команд, буферы, обеспечивающие связь с шиной, и предназначено для выполнения функций, связанных с выборкой операндов, установлением очередности команд и формирования адресов операндов и команд. Всего данный МП содержит 14 регистров: 3 блока по 4 регистра плюс регистр IP (Instruction Pointer - неполный аналог программного счетчика) и флаговый регистр F. Регистры общего назначения – РОНы (16 разрядов), только они могут адресоваться побайтно. AX/AH/AL – регистр-аккумулятор; BX/BH/BL – индексный регистр базы; CX/CH/CL – регистр-счетчик; DX/DH/DL – регистр данных. Группа указательных и индексных регистров – 2 указательных и 2 индексных регистра: SP – регистр-указатель стека; BP – регистр-указатель базы; SI – индекс источника; DI – индекс приемника. Группа из 4 сегментных регистров: CS – регистр сегмента кода; DS – регистр сегмента данных; SS – регистр сегмента стека; ES – регистр дополнительного сегмента данных. Флаговый регистр 16-ти разрядный. Младший байт флагового регистра такой же, как у МП К580ВМ80. В старшем байте используются 4 бита: 1 флаг и 3 бита управления. Каждый флаг обозначен двумя буквами: CF (Carry Flag) – флаг переноса; PF (Parity Flag) – флаг паритета; AF (Auxiliary Flag) – вспомогательный флаг переноса. ZF (Zero Flag) – флаг нуля; SF (Sign Flag) – флаг знака; OF (Overflow Flag) – флаг переполнения DF (Direction Flag) – флаг направления IF (Interrupt Flag) – флаг прерываний TF (Trap Flag) – флаг трассировки или пошагового выполнения команд программы. 5.1.2. Режимы работы микропроцессораПредполагается, что все устройства, входящие в состав микропроцессорной системы, способны работать в темпе процессора, но может иметься строго ограниченное количество медленных устройств (на практике – 2). Вводится TW – время ожидания, связанное с работой медленных устройств. Процессор способен работать в 2-х режимах: - минимальный; - максимальный. В минимальном режиме МП работает аналогично процессору К580ВМ80 с более высокой производительностью и сам формирует сигналы для шины управления (ШУ). Максимальный режим используется в системах, где присутствуют сопроцессоры (8087, ввода-вывода, и т.д.). В этом случае сигналы управления заменяются специальными сигналами состояния и для восстановления сигналов шины управления необходимо использовать специализированную микросхему системного контроллера. Количество сигналов управления и их назначение становятся иными. Образуется целый ряд сигналов, различных для разных режимов работы. Сигналы на выводах МП частично мультиплексированы и для получения 3-х шинной организации системной магистрали приходится использовать буферные регистры для запоминания адреса. Данные же передаются через двунаправленные шинные формирователи с тремя состояниями без запоминания. 5.1.3. Структура минимально укомплектованной системы на базе микропроцессора К1810ВМ86Системная магистраль микропроцессора имеет раздельные шины адреса и данных, но на выводах микропроцессора они мультиплексированы (рис. 5.2). Для перехода к раздельным шинам адреса и данных разряды адреса запоминаются в буферных регистрах типа КР580ИР82. Запись производится с помощью сигнала ALE - Address Location Enable. В этих регистрах обычно фиксируется сигнал ВНЕ#, разрешающий или определяющий использование старшего байта. Эти регистры постоянно находятся в активном состоянии (вход управления третьим состоянием постоянно заземлен).

5.1.4. Структура системы средней сложности на базе микропроцессора К1810ВМ86Максимальный режим отличается тем, что в нем используются дополнительные управляющие сигналы, обеспечивающие совместную работу центрального процессора с другими процессорами (сопроцессорами). Сопроцессоры берут на себя выполнение арифметических действий (ВМ87) и реализацию обмена данными с внешними устройствами (ВМ89). Кроме того, возможно построение системы, где совместно работает несколько микропроцессоров (ВМ86). При установке максимального режима изменяется назначение восьми выводов микропроцессора, что отражается в изменении их обозначений (таблица 5.3).

На выводах S0#, Sl#, S2# в тактах Т1, Т2 и Т4 присутствует код состояния микропроцессора, характеризующий текущий цикл работы и определяющий способ использования шины A/D. Во время тактов ТЗ и Т4, когда шина A/D не используется, на выводах S0#, Sl#, S2# присутствует код 111. На основе этих сигналов о состоянии микропроцессора системный контроллер К1810ВГ88 формирует необходимые для управления внешними устройствами сигналы системной шины. Таким образом, в максимальном режиме микропроцессор обязательно работает совместно с контроллером системной шины.

Выводы RQ#/GT0# и RQ#/GT1# являются двунаправленными линиями, предназначенными для организации захвата системной шины другими устройствами. Вход запроса захвата RQ#/GT0# имеет более высокий приоритет, а в остальном эти входы функционально эквиваленты. Захват начинается с поступления на один из входов RQ#/GTi# сигнала запроса шины длительностью в один такт от внешнего устройства (если запрос приходит на оба входа, выбирается наиболее приоритетный). Во время очередного такта Т1 или Т4 на этот вывод микропроцессор подает выходной сигнал захвата, который информирует запросившее устройство о разрешении. В следующем такте микропроцессор освобождает шину сигналом, который также подается на вывод RQ#/GTi# микропроцессора, и имеет длительность один такт. Получив этот сигнал, микропроцессор возобновляет работу. Вывод LOCK#, так же как и выводы RQ#/GTi#, служит для организации взаимодействия микропроцессора с внешними устройствами. Активный сигнал LOCK# = 0 вырабатывается с помощью специальной команды и позволяет, в случае необходимости, запретить захват шины микропроцессора внешними устройствами. Выводы QS0, QS1 несут информацию о формировании очереди из байтов команд. Для дешифрации сигналов состояния микропроцессора (S0, SI, S2) в систему (при использовании микропроцессора в максимальном режиме) включается системный контроллер К1810ВГ88, позволяющий осуществить полную развязку управляющей, адресной и информационной шин, а также учесть различия ВУ и ЗУ при обращении к ним. Это позволяет полностью реализовать возможности адресации, предусмотренные ВМ86, т.е. возможности обращения к 1 Мбайт памяти и 64 Кбайт портов ввода-вывода. | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||