0_МПиИСТС_Все главы. Микропроцессоры и интерфейсные средства транспортных средств

Скачать 10.01 Mb. Скачать 10.01 Mb.

|

9.3 Разработка устройств сопряжения для ISAПри разработке УС необходимо в первую очередь сформулировать требования, предъявляемые к нему, проанализировать функции, которые компьютер должен выполнять с помощью данного УС. В общем случае эти функции могут быть реализованы как аппаратурой УС, так и программным обеспечением компьютера. В свою очередь, УС может включать в себя процессор, микроконтроллер, микропрограммный автомат, интегральные схемы программируемой логики или жесткую логику. Сочетания перечисленных решений различаются между собой стоимостью, сложностью решаемых задач, гибкостью (способностью перенастройки на другую задачу), быстродействием При выборе того или иного решения надо учитывать степень трудоемкости его реализации. Очень часто значительные трудности вызывает составление программного обеспечения для встроенного контроллера или микропрограммного обеспечения для встроенного микропрограммного автомата. Для этого обычно требуются сложные системы разработки. В то же время проектирование жесткой логики требует большого мастерства в части схемотехнических решений. Вместе с тем при прочих равных условиях представляется наиболее разумным сочетание программных средств компьютера и жесткой логики УС с перенесением сложной обработки на компьютер и достижением высокого быстродействия с помощью жесткой логики. К сожалению, это удается не всегда. Функции, выполняемые УС, можно разделить на две группы. К первой группе относятся интерфейсные функции, то есть те, которые обеспечивают обмен с выбранным интерфейсом компьютера (ISA, Centronics, RS-232C, USB или какие-нибудь еще). Вторую группу образуют операционные или основные функции, ради которых, собственно, и создается УС. Строго говоря, если УС предназначено для сопряжения компьютера с каким-нибудь другим устройством, также имеющим стандартный интерфейс, то добавляются еще и функции обмена с этим интерфейсом. В соответствии с этими двумя выделенными группами функций в структуре УС можно также выделить две части: интерфейсную и операционную. При этом подходы к проектированию этих двух частей имеют принципиальные отличия. Операционные части УС могут быть самыми разнообразными. Это открывает простор для творчества, нестандартных решений, оптимизации и экспериментирования с целью наилучшего решения той уникальной задачи, для которой создается УС. А интерфейсные части практически у всех УС одинаковы или очень похожи между собой, так как интерфейсные функции жестко определяются протоколом выбранного стандартного интерфейса. Конечно, интерфейсные части могут быть более или менее сложными в зависимости от задачи, решаемой УС, но все-таки все они состоят из одного и того же набора блоков и узлов, реализующих одинаковые функции и строящиеся, как правило, по стандартным схемам. Поэтому основное внимание в этом параграфе будет уделено проектированию именно интерфейсных частей, однако будет также рассмотрено несколько конкретных схем УС, имеющих наиболее характерные операционные части. Прежде чем перейти к методам построения отдельных блоков интерфейсных частей УС, ориентированных на ISA, надо выделить основные интерфейсные функции, определяемые стандартом магистрали. В соответствии с определением интерфейса, приведенным в другой главе, мы должны обеспечить информационную, электрическую и конструктивную совместимость устройств на магистрали. О конструктивной совместимости мы здесь говорить не будем (она относится к этапу проектирования печатной платы и сводится к точному соблюдению всех размеров платы, разъемов и крепежных элементов). Информационная совместимость предполагает точное выполнение протоколов обмена и правильное использование сигналов магистрали. Электрическая совместимость подразумевает согласование уровней входных, выходных и питающих напряжений и токов. 9.3.1. Проектирование аппаратуры для сопряжения с ISAПри проектировании узлов УС, особенно входящих в интерфейсную часть УС, необходимо учитывать временные диаграммы ISA (рис. 9.3 — рис. 9.6). Наиболее важными при проектировании УС, работающих как устройства ввода/вывода, являются следующие временные интервалы: • задержка между выставлением адреса и передним фронтом строба обмена (не менее 91 нс) — определяет время распознавания своего адреса проектируемым УС; • длительность строба обмена (не менее 176 нс); • задержка между передним фронтом сигнала -IOR и выставлением УС читаемых данных (не более 110 нс) — определяет требования к быстродействию буфера данных УС; • задержка между задним фронтом сигнала -IOW и снятием записываемых данных (не менее 30 нс) — определяет требования к быстродействию принимающих данные узлов УС. При работе УС в циклах обмена с памятью берутся аналогичные временные интервалы (рис. 9.4). Буферирование сигналов магистрали Буферирование магистральных сигналов применяется для электрического согласования и выполняет две основные функции: электрическая развязка (для всех сигналов) и передача сигналов в нужном направлении (только для двунаправленных сигналов). Это первая и наиболее очевидная интерфейсная функция любого УС. Иногда с помощью буферирования реализуется также мультиплексирование сигналов. Для буферирования наиболее часто используются микросхемы магистральных приемников, передатчиков, приемопередатчиков, называемые также нередко буферами или драйверами. Электрическая развязка подразумевает обеспечение нужных входных и выходных токов (уровни напряжения на ISA — ТТЛ). Как уже упоминалось, входные каскады УС должны обеспечивать уровень входного тока не более 0,8 мА, а выходные и двунаправленные каскады должны выдавать выходной ток не менее 24 мА (при нулевом выходном сигнале). Несоблюдение этого правила может привести к сбоям в работе компьютера и даже к выходу из строя его отдельных узлов. При этом, строго говоря, все определяется конфигурацией системы. Если к магистрали компьютера подключена только одна плата расширения, то требования к ней будут гораздо мягче, чем в случае использования нескольких плат. Но всегда надо рассчитывать на возможность развития системы и подключения дополнительных плат. Поэтому лучше все-таки придерживаться приведенных величин. Выбор типа драйвера для каждого магистрального сигнала (приемник, передатчик или приемопередатчик) определяется назначением этого сигнала и возможными режимами работы УС. Так, например, в случае, когда УС работает в режиме программного обмена, приемники используются для сигналов адреса SAO ... SA9 и для управляющих сигналов -IOR, -IOW, AEN, BALE, -SBHE, передатчики используются для I/O СН RDY и -I/O CS 16. Для сигналов данных могут использоваться приемники (если УС работает только в режиме записи), передатчики (если УС работает только в режиме чтения) или приемопередатчики (если УС работает как в режиме чтения, так и в режиме записи). Если возможен обмен по прерываниям, то добавляется передатчик для сигнала IRQ, а если применяется ПДП, то применяется передатчик для сигнала DRQ и приемник для сигнала DACK. Остановимся подробнее на характеристиках микросхем, которые могут применяться для буферирования. Приемники магистральных сигналов должны удовлетворять двум основным требованиям: малые входные токи и высокое быстродействие (они должны успевать отрабатывать в течение отведенных им временных интервалов циклов обмена). Конкретное значение допустимых времен задержек определяется используемой схемой интерфейсной части УС в целом, но можно определенно сказать, что микросхемы обычных (не быстродействующих) КМОП серий здесь непригодны, несмотря на их малые входные токи. Не подходят и микросхемы серии К155 (SN74) из-за их больших входных токов. Требованиям, предъявляемым к приемникам, удовлетворяют следующие серии микросхем: КР1533 (SN74ALS), К555 (SN74LS) и КР1554 (74АС). Величины входных токов логического нуля для них составляют соответственно 0,2 мА, 0,4 мА и 0,2 мА, а величины временных задержек не превышают соответственно 15 нс, 20 нс и 10 нс. Кроме этих серий, в качестве приемников можно использовать специальные микросхемы магистральных приемников серии КР559 (входной ток не более 0,12 мА, задержка не более 30 нс). Требованиям, предъявляемым к приемникам, удовлетворяют также микросхемы электрически программируемых ППЗУ и ПЛМ серии КР556 (136, N82S, DM87S, НМ76). Это тоже немаловажно, так как их очень удобно использовать в схемах селекторов адреса УС. Входные токи этих микросхем не превышают 0,25 мА. Пример входного буфера показан на рис. 9.7. Отметим, что малые входные токи микросхем серий КР1533 и КР1554 позволяют подключать к линии магистрали даже два входа таких микросхем.  Рис. 9.7. Пример входного буфера Перейдем к передатчикам. Требования к ним: большой выходной ток и высокое быстродействие. Часто они должны иметь также отключаемый от линии выход (например, для шины данных), то есть иметь выход с открытым коллектором или с тремя состояниями. Это связано с необходимостью перехода УС в пассивное состояние в случае отсутствия обращения к нему. Выбор микросхем передатчиков гораздо больше, такие микросхемы есть практически в каждой серии (К155, К555, КР1533, К559 и т.д.).

Передатчики часто выполняют функцию мультиплексирования данных, которые должны поступать на шину данных ISA от различных источников. На рис. 9.8. упрощенно показаны два наиболее распространенных подхода к решению данной задачи (для 8-разрядной шины данных). Отметим, что при использовании микросхем мультиплексоров следует брать те из них, которые имеют выходы с тремя состояниями и большие выходные токи. Рассмотрим теперь приемопередатчики. Требования к ним включают в себя требования к приемникам и передатчикам, то есть малый входной ток, большой выходной ток, высокое быстродействие и обязательное отключение выходов. Надо отметить, что в простейшем случае (когда разрядов немного) приемопередатчики могут быть построены на микросхемах приемников и передатчиков с отключаемыми выходами. Однако при большом количестве разрядов надо использовать специальные микросхемы приемопередатчиков. Эти микросхемы бывают двух основных типов (рис. 9.9): с двумя двунаправленными шинами или с тремя шинами (одной двунаправленной, одной входной шиной и одной выходной шиной).

Для управления работой приемопередатчиков используются два управляющих сигнала. Характеристики некоторых приемопередатчиков приведены в таблице 9.10. В ней указаны разрядность шин, величины задержек и входных/выходных токов всех шин микросхем. В табл. 9.11 приведены режимы работы в зависимости от управляющих сигналов. Отметим такую особенность микросхемы КР59ИПЗ, как невозможность одновременного отключения ее двунаправленной и выходной шин. В таблице использованы следующие обозначения: ОК — выход с открытым коллектором, ЗС — выход с тремя состояниями. Отметим, что если приемопередатчики с открытым коллектором используются для буферирования шины данных, то на их выходах необходимо включать резисторы на шину +5В (если они не работают на линию, к которой эти резисторы уже подключены). Поэтому их применение иногда оказывается нежелательным. Это совсем не означает, что они не могут быть использованы, например, в операционной части УС. Особенностью микросхемы КР580ВА86 (87) является то, что шины имеют различные выходные токи, и только одна из них (В) удовлетворяет требованиям стандарта ISA. У других микросхем все двунаправленные шины выдают требуемые выходные токи. Те или иные сигналы управления могут быть более или менее удобны в каждом конкретном случае. Табл. 9.10. Характеристики приемопередатчиков.

Табл. 9.11. Микросхемы приемопередатчиков.

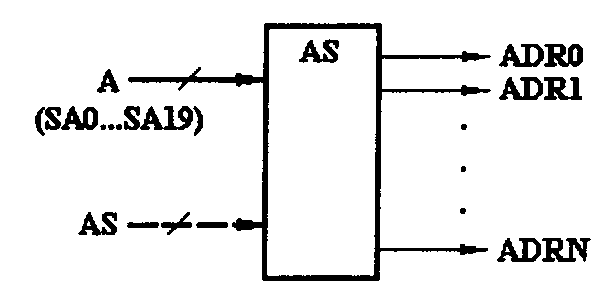

На рис. 9.10 показаны три варианта реализации приемопередатчиков для шины данных: на приемнике и передатчике, на приемопередатчике с двумя шинами и на приемопередатчике с тремя шинами (для 8-разрядных данных). Отметим, что чаще нужны приемопередатчики с раздельными входными и выходными шинами данных УС, но при использовании многоразрядных микросхем ОЗУ или сдвиговых регистров типа КР1533ИР24 (SN74ALS299), которые имеют двунаправленную шину данных, удобнее применять приемопередатчики с совмещенными входными/выходными данными УС. Построение селекторов адреса Второй основной интерфейсной функцией, выполняемой УС, работающими в режиме программного обмена, является селектирование или дешифрация адреса. Эту функцию выполняет узел, называемый селектором (дешифратором) адреса, который должен выработать сигналы, соответствующие выставлению на шине адреса магистрали кода адреса, принадлежащего данному УС, или одного из зоны адресов данного УС. Обобщенная схема селектора адреса для УС, работающего как устройство ввода/вывода, показана на рис. 9.11. Здесь шина А — это шина адреса магистрали, шина AS — внутренняя шина УС, на которой присутствует код, сравниваемый с адресом магистрали (может отсутствовать), ADR — выходные сигналы селектора адреса, формируемые при обращении по магистрали к данному УС.  Рис. 9.10 Варианты построения приемопередатчиков данных Заметим, что совсем не обязательно дешифровать все линии адресной шины магистрали. Довольно часто для упрощения схемы УС удобно часть этих линий отбросить, не заводить на селектор адреса. При этом важно, чтобы адреса проектируемого УС не перекрывались с адресами, занятыми другими устройствами компьютера. Наиболее часто отбрасывают младшие разряды адреса.

Рассмотрим селектор адреса для УС, работающего в адресном пространстве памяти. В этом случае необходимо обрабатывать 20 разрядов адресной шины (при полном объеме памяти до 1 Мбайта) или все 24 разряда адресной шины (при полном объеме памяти до 16 Мбайт). Надо отметить, что разработка УС, работающего как устройство ввода/вывода, гораздо проще. Переход в адресное пространство памяти вызывается обычно необходимостью ускорения обмена с внутренним ОЗУ или ПЗУ, входящим в состав УС. Но в этом случае селектор адреса не должен обрабатывать столько младших разрядов адреса, сколько адресных входов имеет это ОЗУ или ПЗУ. Например, если внутреннее ОЗУ имеет организацию 1К х 8 (десять адресных входов), то десять младших разрядов адреса SA0 ... SA9 должны подаваться не на селектор адреса, а (через соответствующие буфера) непосредственно на адресные входы ОЗУ. Разряды адреса LA17 ... LA23 перед подачей на селектор адреса должны быть зафиксированы на все время цикла обмена (рис. 9.12). Отметим, что при использовании микросхемы регистра с малыми входными токами можно обойтись без входных буферов как для сигналов LA17 ... LA23, так и для сигнала ALE. Помимо сигналов, показанных на рис. 9.11, на селектор адреса часто подают сигнал AEN, который при этом используется для запрещения выработки выходных сигналов. То есть, если по магистрали осуществляется прямой доступ к памяти, то устройство ввода/вывода должно быть обязательно отключено от магистрали и не должно реагировать на выставляемые на шине адреса коды.  Рис. 9.12 Обработка сигналов LA17…LA23 Рассмотрим несколько наиболее характерных схемотехнических решений селекторов адреса. Но сначала выделим требования, предъявляемые к ним: • высокое быстродействие (селектор адреса должен иметь задержку не более чем интервал между выставлением адреса и началом сигнала строба обмена); • возможность изменения селектируемых адресов (это особенно важно для устройств ввода/вывода из-за малого количества свободных адресов); • малые аппаратурные затраты. Самое простое решение при построении селектора адреса — использование только микросхем логических элементов. Например, на рис. 9.13 показана схема, реагирующая на единственный адрес 3CF. Основным достоинством такого подхода является высокое быстродействие (для схемы на рис. 9.13 задержка не превышает 30 нс при выбранных элементах). При использовании микросхем с малыми входными токами можно обойтись без буферов. Но есть и недостатки: необходимость проектирования схемы заново для каждого нового адреса, невозможность смены адреса, сложность организации выбора нескольких адресов. Если надо предусмотреть возможность изменять выбираемый адрес, то можно использовать отключаемые инверторы для всех линий адреса. Тогда, подключая или отключая нужные инверторы с помощью перемычек или переключателей, мы получаем возможность перестраивать в некоторых пределах наш селектор адреса. Другой путь — применение элементов "исключающее ИЛИ", работающих как управляемые инверторы. На рис. 9.14 показан такой же, что и на рис. 9.13, селектор адреса, но выбирающий в зависимости от кода на шине AS, задаваемого перемычками, адреса 3CF, 2CF, ICF, OCF и т.д. (всего 8 возможных адресов).

Селекторы адреса могут быть реализованы также на микросхемах стандартных дешифраторов. Вообще говоря, можно построить селектор адреса только на этих микросхемах, но объем аппаратуры получается при этом очень большим. Поэтому более правильным решением будет обработка старших адресных разрядов какой-то другой схемой (например, одним или несколькими логическими элементами), а младших — с помощью одной микросхемы дешифратора. Примером может служить селектор адреса на рис. 9.15, сигналы на выходах которого соответствуют выбору шестнадцати адресов в пределах зоны, задаваемой другой частью схемы (обозначена AS). Вовсе не обязательно использовать дальше все сигналы ADRO ... ADR15, можно с помощью перемычек применять их для изменения адресов УС. Отметим такое достоинство этого подхода по сравнению с рассмотренным ранее, как возможность селектирования нескольких адресов.

Следующий метод реализации селектора адреса — использование микросхем цифровых компараторов кодов, на одну входную шину которых подается адрес из магистрали, а на другую входную шину — код AS, соответствующий селектируемому (выбираемому) адресу. Очевидно, что каскадируя эти микросхемы, можно построить селектор адреса исключительно на них, но это приведет к значительным аппаратурным затратам. Гораздо эффективнее применять компараторы кодов для изменения селектируемых адресов. Наконец, наиболее универсальными являются селекторы адреса на базе ППЗУ, ПЛМ и ИС ПЛ. В таком случае селектируемый адрес (или селектируемые адреса) зависит не от схемотехнических решений и не от кода, задаваемого переключателями, а от прошивки ППЗУ, ПЛМ или ИС ПЛ. Такой подход требует решения двух задач: - выбора микросхемы; - разработки таблицы прошивки.

Выработка внутренних стробирующих сигналов Следующая важная функция интерфейсной части УС — выработка внутренних стробирующих сигналов синхронно с магистральными командными сигналами (-IOR, -IOW, -MEMR, -MEMW) в случае обращения по адресам проектируемого УС. Условно узел, выполняющий эту функцию, может быть представлен в следующем виде (рис. 9.16). На его входы подаются сигналы ADRO ... ADRN с выхода селектора адреса, SBHE (в случае необходимости разделения 8- и 16-разрядных циклов), а также буферированные магистральные стробы записи и чтения (R и W). Выходы — это сигналы STRO ... STRn, соответствующие обращениям с записью или чтением по всем адресам или группам адресов УС. Рассмотрим несколько методов построения этого узла.

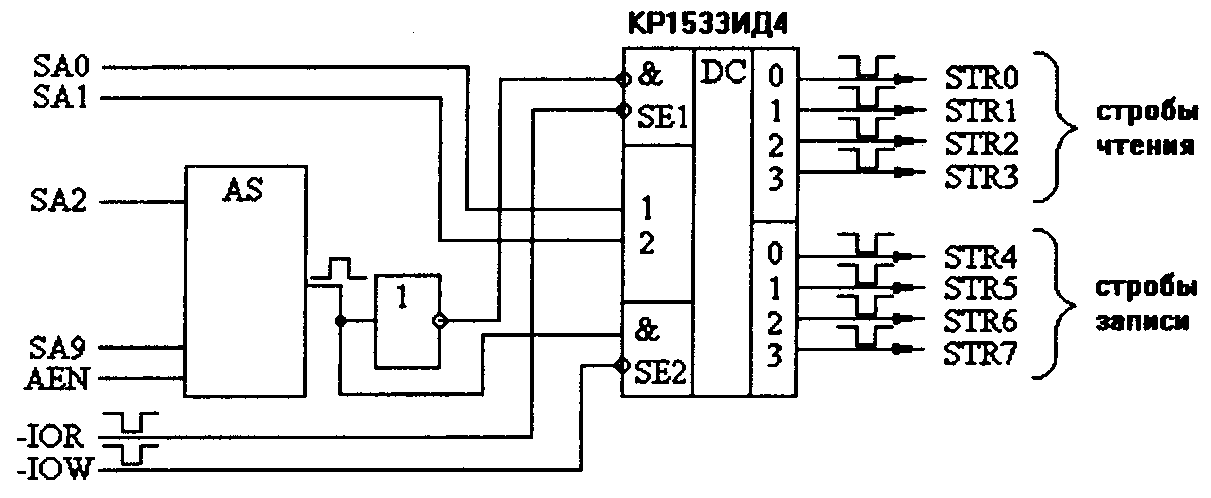

Самый простейший подход — использование логических элементов — удобен в случае малого числа внутренних стробов STR. На рис. 9.17 показана схема для двух адресов УС, доступных по чтению и записи. Достоинства такого подхода — малое число элементов и высокое быстродействие, а недостаток состоит в том, что каждый раз приходится разрабатывать свою схему для нового УС. В случае необходимости выработки большого числа внутренних стробирующих сигналов удобно использовать микросхемы дешифраторов. Пример такого решения представлен на рис. 9.18. Здесь два младших разряда адреса подаются не на селектор адреса, а непосредственно на дешифратор, верхняя половина которого управляется сигналом с селектора адреса и сигналом -IOR, а нижняя — сигналом с селектора адреса и -IOW. Таким образом, выходы STRO ... STR3 соответствуют циклам чтения из четырех последовательных адресов, a STR4 ... STR7 — записи в эти адреса. Отметим, что не обязательно надо использовать все выходы дешифратора. Достоинства этого подхода — однотипность схемы рассматриваемого узла для всех УС и малые аппаратурные затраты при необходимости получения большого количества внутренних стробов обмена.  Рис. 9.17. Выработка внутренних стробов с помощью логических элементов В некоторых случаях удобно не разделять интерфейсную часть УС на селектор адреса и формирователь внутренних стробов.

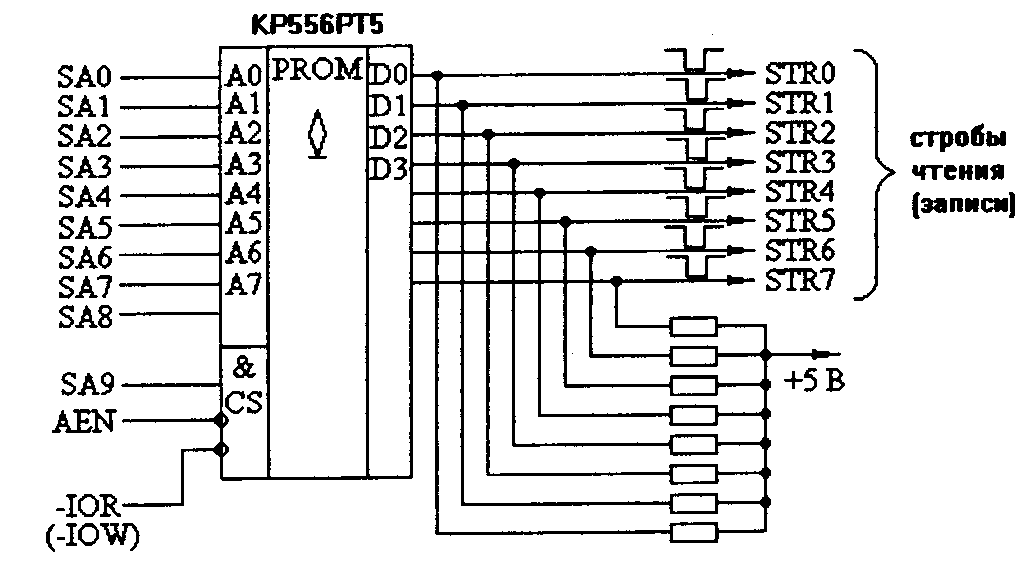

Пусть, например, УС должно работать только в циклах записи по его адресам (или только в циклах чтения). При этом оба рассмотренных узла могут быть выполнены на одной микросхеме ППЗУ (рис. 9.19). Здесь к моменту прихода магистрального строба обмена ППЗУ уже успеет сформировать выходные сигналы (закончится время выборки адреса). Поэтому внутренние стробы обмена будут задержаны относительно магистральных стробов только на время выбора ППЗУ. Такой недостаток всех микросхем ППЗУ, как неопределенность выходных сигналов в течение некоторого времени после любого изменения адреса, здесь не сказывается на работе схемы. Однако не следует надеяться, что схема будет работать также нормально при подаче одного или обоих магистральных стробов обмена (-IOR и -IOW) на адресные входы ППЗУ. Особо следует остановиться на организации 16-разрядного обмена и разделении пересылок старшего и младшего байтов. Здесь участвуют два сигнала магистрали, которые не используются при 8-битном обмене: -SBHE и -I/O CS 16 (или -MEM CS 16). При этом сигнал -SBHE должен обрабатываться УС только в случае необходимости как 16, так и 8-разрядного обмена (вспомним, что он определяет тип цикла обмена совместно с сигналом SAO в соответствии с таблицей 9.3). На рис. 9.20 в качестве примера приведена схема формирователя внутренних стробов для 16-разрядного УС, работающего только в цикле записи 16-разрядного слова, старшего байта или младшего байта.

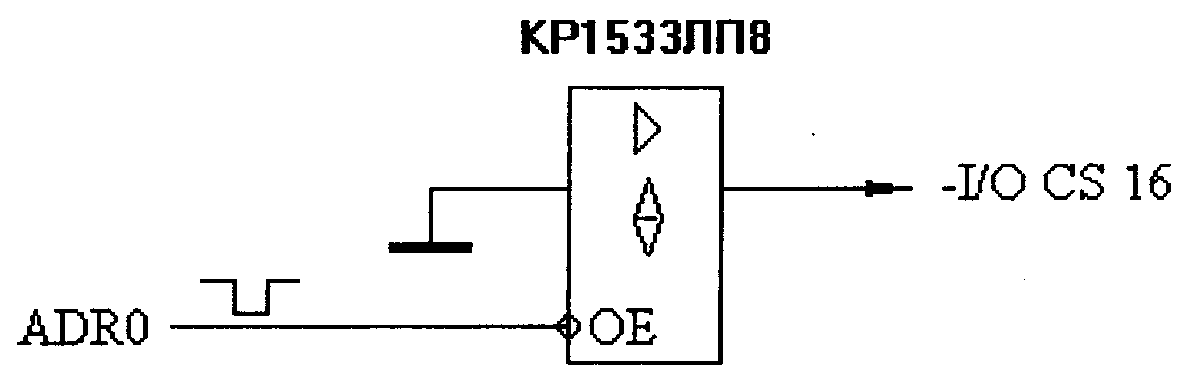

Выходной строб формирователя STR0 соответствует записи старшего байта или слова, а выходной строб STRI — записи младшего байта или слова. Сигнал -I/O CS 16 вырабатывается при любом обращении к нашему УС, детектируемым селектором адреса. Отметим, что этот сигнал может формироваться и элементом с тремя состояниями, но в этом случае надо обеспечить активный нулевой уровень при селектировании адреса и высокоимпедансное состояние в противном случае (рис. 9.21). Это предотвратит конфликт на линии -I/O CS 16 сигналов от разных плат расширения.

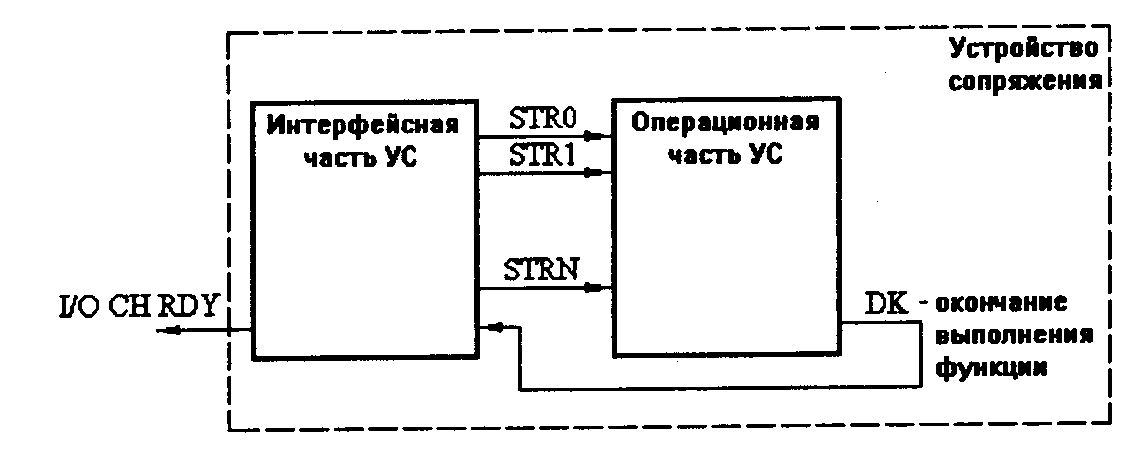

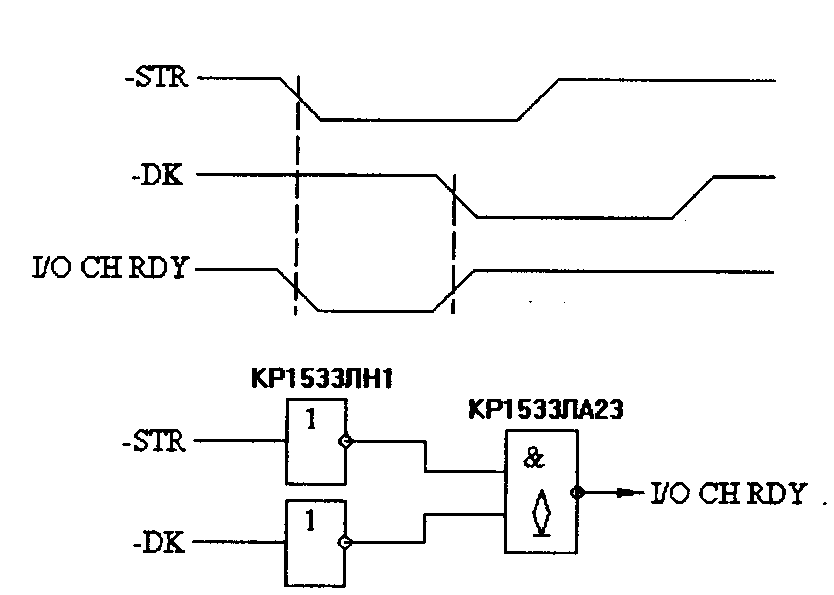

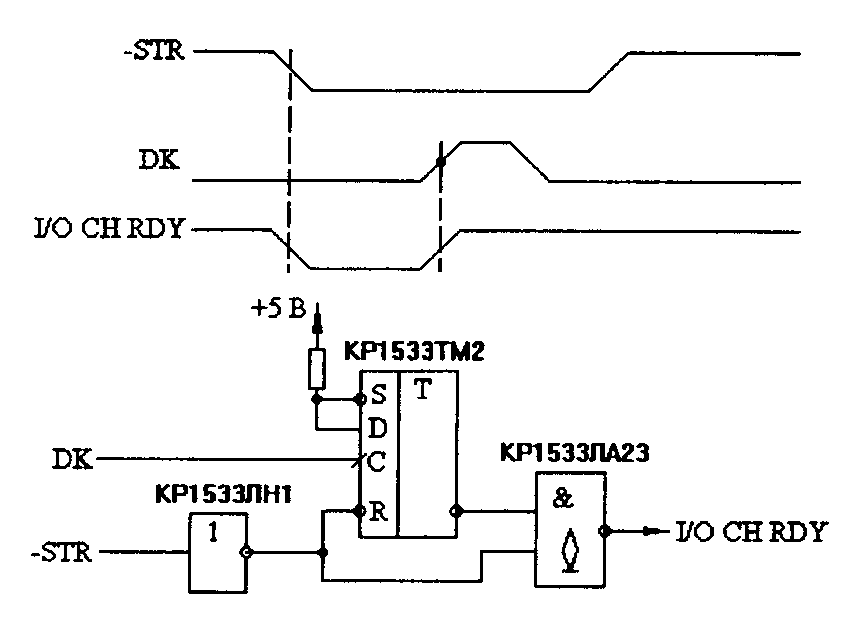

Асинхронный обмен по ISA Основным типом обмена по ISA является синхронный обмен, то есть обмен в темпе задатчика без учета быстродействия исполнителя. Однако возможен и асинхронный обмен, при котором "медленный" исполнитель приостанавливает работу задатчика на время выполнения им требуемой команды. В этом случае надо использовать сигнал I/O СН RDY, снятие которого (установка в состояние логического нуля) говорит о неготовности исполнителя к окончанию цикла обмена. Как уже отмечалось, приостановка производится на целое число периодов SYSCLK и не может быть дольше системного времени ожидания 15,6 мкс (для некоторых компьютеров — 2,5 мкс). Рассмотрим некоторые аппаратурные решения для асинхронного обмена. Прежде всего, здесь можно выделить две ситуации: когда существует внутренний сигнал УС, говорящий об окончании выполнения функции записи или чтения, и когда такого сигнала нет. В качестве этого сигнала (обозначим его DK) может выступать, например, сигнал окончания преобразования (готовности данных) АЦП, входящего в состав УС. На рис. 9.22 приведена структура УС с сигналом DK. DK может быть потенциальным (то есть сниматься после окончания стробов обмена) или импульсным (то есть окончанию выполнения функции соответствует фронт сигнала DK). Временные диаграммы и схемы для этих двух случаев показаны на рис. 9.23 и 9.24 (для упрощения считаем, что строб обмена — единственный).

Если сигнал DK отсутствует в явном виде, но известно время выполнения функции или его верхний предел, то необходимо сформировать задержку в самой интерфейсной части. В схеме на рис. 9.25 слева эта задержка определяется временем выдержки одновибратора. Надо отметить, что при проектировании УС одним из показателей мастерства разработчика является количество использованных им одновибраторов или RC-цепочек (естественно, эти величины обратно пропорциональны друг другу). Это связано с тем, что любые аналоговые цепи подвержены действию помех и требуют настройки. Поэтому, если есть возможность, то надо формировать задержки, временные сдвиги, интервалы с помощью магистральных тактовых сигналов SYSCLK и OSC или внутренних тактов УС. На рис. 9.26 справа приведена схема с использованием линии задержки на сдвиговом регистре, задержка которой определяется номером замкнутого переключателя и задается с точностью до периода сигнала SYSCLK. Но, в принципе, в данном случае требования к точности времени задержки невысоки, и использование одновибратора и даже простой RC-цепочки вполне допустимо.

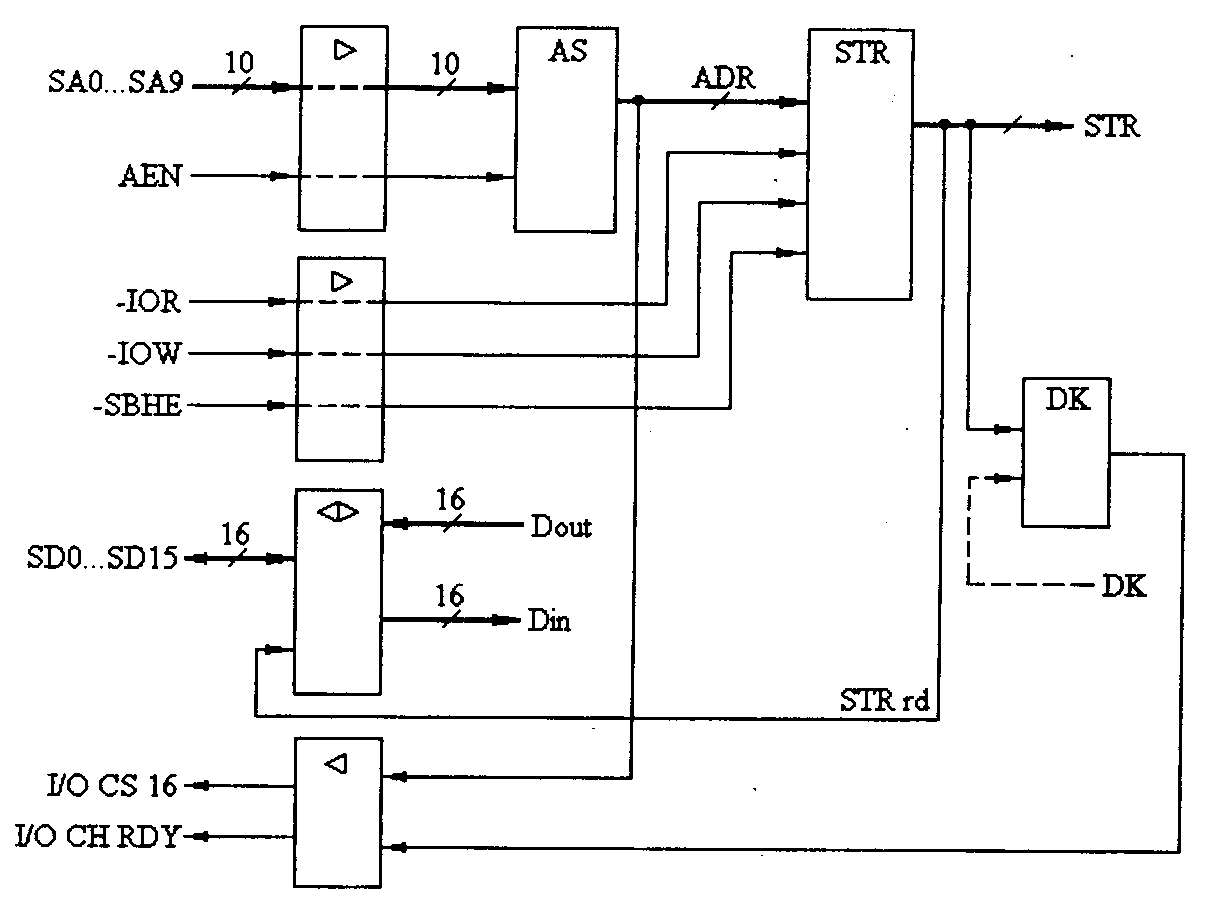

Асинхронный режим обмена по ISA можно реализовать и на более высоком уровне: путем опроса задатчиком флага готовности исполнителя и путем использования прерываний. Эти решения удобны в случае очень медленных УС, то есть тех, время реализации функции которыми превышает предельное системное время задержки (системный тайм-аут). Теперь попробуем изобразить обобщенную структурную схему интерфейсной части УС, включающей в себя все рассмотренные узлы (рис. 9.27). Здесь использованы входные буфера, двунаправленный буфер данных (в общем случае должен быть разделен на два для каждого байта), выходной буфер, селектор адреса, формирователь внутренних стробов и формирователь сигнала асинхронного обмена I/O СН RDY (DK).

Оценим предельные значения времен задержек всех узлов интерфейсной части. Здесь надо рассмотреть две ситуации. Если наше УС работает только в режиме записи в него информации, то желательно, чтобы задержка сигнала STR относительно сигнала -IOW и задержки сигналов данных были примерно одинаковыми. Ни в коем случае задержка сигнала STR не должна превышать задержку данных более чем на 30 нс, иначе УС примет неверные данные. Разность задержки буферирования и селектирования адреса и задержки буферирования сигнала -IOW не должна превышать 91 нс, иначе УС не будет реагировать на свой адрес. Если наше УС работает только в режиме чтения из него информации, то сумма задержки сигнала STR относительно сигнала -IOR и задержки буфера данных не должна превышать 110 нс, иначе процессор примет неправильные данные от УС. Требования к буферу адреса и селектору адреса такие же. Если же УС должно работать как в режиме чтения, так и в режиме записи, то оно должно удовлетворять всем перечисленным требованиям.

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||