КП_МПС_Абрамов. Микропроцессорное устройство управления регулятором температуры по заданному закону

Скачать 2.47 Mb. Скачать 2.47 Mb.

|

|

3.5 Проектирование блока управления термостатом В курсовом проекте блок управления термостатом состоит из вентилятора, нагревателя и электронных схем, с помощью которых можно будет программно включать и выключать вентилятор и нагреватель для изменения температуры по заданному закону. В данном случае достаточно применить мощный ключ, управляемый одним из битов порта микроконтроллера. Так как термостат представляет собой закрытый объем, в котором осуществляется регулирование температуры, то можно сделать вывод, что охлаждение с помощью вентилятора будет протекать интенсивнее, если предусмотреть в закрытом объеме регулируемые жалюзи. Для управления ими можно назначить еще один из битов порта микроконтроллера, но в нашем случае привяжем их к управлению вентилятором. Когда мы подаем команду включить вентилятор, происходит его включение и открывание жалюзи, а по команде выключить вентилятор происходит его выключение и закрывание жалюзи. Для управления нагревателем назначим бит Р3.5, а для управления вентилятором бит Р3.4. схема блока управления термостатом приведена на рисунке 3.11.  Рисунок 3.11 – Схема управления термостатом  На схеме оптопара U2 коммутирует контакты нагревателя к сети переменного тока, а оптопара U1 коммутирует контакты вентилятора к сети переменного тока, а также коммутирует контакты механизма открывания жалюзи.  4 Расчет потребляемой мощности и разработка блока питания 4 Расчет потребляемой мощности и разработка блока питанияДля расчета потребляемой мощности достаточно просуммировать потребляемую мощность всех компонентов, входящих в состав схемы. Результаты расчета приведены в таблице. При расчете использованы максимальные напряжения питания, повышенные на 5%. В расчете не учитывается потребляемая мощность усилителей, связывающий МПС с внешними устройствами, поскольку их типы не заданы.

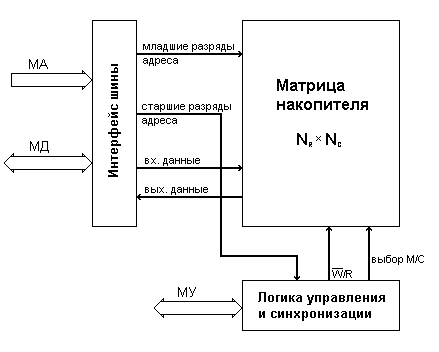

Для получения полной потребляемой мощности необходимо просуммировать полученное значение (2481,25) и потребляемую мощность модуля памяти, равную 1440,15 мВт. Таким образом потребляемая мощность МПС равна 2781,4 мВт. К разрабатываемому блоку питания (рисунок 4.1) предъявляется следующее требование: обеспечение выходных напряжений +5 В (ток 900 мА), +15 В (ток 1 мА) и -15 В (ток 0,015 мА). Схема блока показана на рисунке 4.1. Его основу составляет трансформатор T. Сетевая обмотка трансформатора подключается к бытовой сети переменного тока (U=220В, F=50Гц). На первой вторичной обмотке генерируется напряжение U21=10В, а на второй U22=20В. Напряжение на первой вторичной обмотке получаются исходя из формулы: UII = B*Uн, где Uн - требуемое постоянное напряжение на нагрузки; UII - переменное напряжение, которое должно быть на вторичной обмотке сетевого трансформатора; В - коэффициент, зависящий от тока нагрузки.  Отсюда U21 = 2,4*5 В = 12 В (для тока нагрузки 1 А). Отсюда U21 = 2,4*5 В = 12 В (для тока нагрузки 1 А).Определим максимальный ток, текущий через каждый диод выпрямительного моста: IД = 0,5*С*Iн, где IД - ток через диод, А; Iн - максимальный ток нагрузки, А; С - коэффициент, зависящий от тока нагрузки. Получим IД = 0,5*0,9*2 = 0,9 А. Подсчитаем обратное напряжение, которое будет приложено к каждому диоду выпрямителя: Uобр = 0,9*Uн, где Uобр - обратное напряжение, В; Uн - напряжение на нагрузке, В. Тогда, Uобр = 0,9*5 В = 4,5 В. В соответствии с этими данными выберем диоды: КД202Б (Iпр = 3А; Uобр = 50 В; Uпр = 1 В). Определим емкость конденсатора фильтра: Сф=Iн*dU / (2*Fc), где Iн - ток, потребляемый нагрузкой источника, dU-пульсации напряжения (принято 5мВ), Fc=50Гц - частота напряжения в обмотке. Получаем С1=45 мкФ. Выбирается конденсатор К50-35 - 50 мкФ. В качестве конденсатора С5 используется КД1 - 0,1 мкФ. Напряжение с выхода фильтра поступает на вход ИМС DD1 интегрального стабилизатора 142ЕН5А (Iпр.max=3А, Uст=5В), с выхода которой снимается стабильное напряжение +5В. Вторая вторичная обмотка имеет вывод средней точки, что используется для получения двуполярного напряжения. Диодный мост, построенный на VD5-VD8 (Д7А: Iпр.max=0.3А, Uобр=50В, Uпр=0,4В), электролитические конденсаторы С3, С4 (К50-35 - 50 мФ) и блокировочные конденсаторы С6,C7 (КД1-0,1 мФ) выбираются по тем же принципам, что и для пятивольтовой цепи. Для стабилизации напряжения применяется простейшая схема параметрического стабилизатора на стабилитроне VD9 (VD10 - для -15В). Параметры этого стабилитрона (типа Д814Д) следующие: Uст=15В, Iст=25мА. Рассчитать номиналы баластных резисторов R1 и R2 можно по следующей формуле: R = (0,9*U2-(2*Uпр+ Uст)) / (Icc+Iст), где  U2=20В - напряжение на вторичной обмотке трансформатора; Uпр=0,5В - падение напряжения на диоде VD5-VD8 при прямом включении, Icc-ток, потребляемый нагрузкой, Iст-ток стабилизации стабилитрона. U2=20В - напряжение на вторичной обмотке трансформатора; Uпр=0,5В - падение напряжения на диоде VD5-VD8 при прямом включении, Icc-ток, потребляемый нагрузкой, Iст-ток стабилизации стабилитрона. Расчет дает R1 = 75 Ом, R2 = 82 Ом.  Рисунок 4.1 - Схема источника питания МПС  5. Разработка и расчет модуля памяти Типичный модуль памяти можно разделить на три функциональных устройства: матрица накопителя; логика управления и синхронизации; интерфейс шины.  ША ШД ШУ Рисунок 5.1 Структурная схема модуля памяти Матрица накопителя модуля памяти состоит из идентичных БИС и представляет собой запоминающую среду. Микросхемы памяти организованы в матрицу из NR строк и NC столбцов. Для получения нужной длины слова (числа бит в слове) каждая строка содержит несколько БИС, каждая из которых представляет часть слова.  Логика управления воспринимает сигналы считывания и записи с шины управления (ШУ) системной шины, а также старшие разряды с шины адреса (ША). Из старших разрядов шины адреса формируется сигнал выбора модуля. Логика интерфейса шины управляет направлением передачи данных и адресов при обращениях к модулю памяти. При записи в память данные с ШД направляются в матрицу накопителя, при считывании – данные передаются в противоположном направлении. Адрес с ША при обращении должен запоминаться в регистрах интерфейса шины. Старшие разряды направляются в логику управления для выбора одной из строк матрицы, а младшие разряды подключаются на адресные входы всех БИС матрицы, но выбираются только одно слово данных из БИС разрешенной строки. Логика управления воспринимает сигналы считывания и записи с шины управления (ШУ) системной шины, а также старшие разряды с шины адреса (ША). Из старших разрядов шины адреса формируется сигнал выбора модуля. Логика интерфейса шины управляет направлением передачи данных и адресов при обращениях к модулю памяти. При записи в память данные с ШД направляются в матрицу накопителя, при считывании – данные передаются в противоположном направлении. Адрес с ША при обращении должен запоминаться в регистрах интерфейса шины. Старшие разряды направляются в логику управления для выбора одной из строк матрицы, а младшие разряды подключаются на адресные входы всех БИС матрицы, но выбираются только одно слово данных из БИС разрешенной строки.Требуется разработать функциональную схему модуля памяти ОЗУ и ПЗУ и сделать ее расчет. Разработать схемы дешифрации модуля памяти, выбрать конкретные микросхемы для схем дешифрации. Исходные данные: Тип микропроцессора – ОЭВМ MCS-51 (AT89C51); Объем каждого субмодуля – 2Кх8; Тип микросхем: - ОЗУ – К537РУ14Б (4Кх1); - ПЗУ – КР556РТ13 (1Кх4);  5.1 Модуль ОЗУ на базе микросхемы КР537РУ14Б. 5.1 Модуль ОЗУ на базе микросхемы КР537РУ14Б.Модуль ОЗУ предназначен для хранения оперативных данных, как было сказано выше. То есть он должен выполнять следующие функции: - хранение данных; - считывание данных; - запись данных; Входными сигналами для данного модуля являются сигналы шины управления (CS,RD,WR), а также сигнала шины адреса. Выходными же сигналами являются сигналы, выставляемые на шину данных при считывание данных из м/с. Микросхема КР537РУ14Б имеет следующие характеристики: Информационная емкость - 4096 бит; Внутренняя организация - 4Кх1; Ucc – 5 В; U1L – 0.8 В; U1H – 2 В; U0L – 0.4 В; U0H – 2.8 В; Iп.х. – 5 мкА; Iп. д. – 35 мА; I0вх. – 3,2 мА; I1вх. – 2 мА; Pcc – 20 мВт; С – 50 пФ; tсчит. (tA(A)) – 14 нс; tCY (WR) – 130 нс; tW(WR) – 90 нс; tW(CS), WR – 90 нс; tW (CS), RD – 130 нс; tSU(A - CS)=20нс;   Рисунок 5.2. Цоколевка микросхемы ОЗУ КР537РУ14Б Таблица 3. Таблица истинности м/с КР537РУ14Б

5.2. Модуль ПЗУ на базе микросхемы КР556РТ13 5.2. Модуль ПЗУ на базе микросхемы КР556РТ13Модуль ПЗУ предназначен для хранения и считывания информации. Для данного модуля входными сигналами являются сигналы шины управления и шины данных, а выходными являются данные выставляемые на шину данных при чтении ПЗУ. Микросхема ПЗУ КР556 РТ13 имеет следующие характеристики: Информационная емкость 4096 бит; Внутренняя организация 1Кх4; Ucc – 5 В; Iпот. – 140мА; I0вх. – 0,25 мА; I1вх. – 40 мкА; Pcc – 735 мВт; tA(A) - 60 нс; С – 30 пФ; tSU(A - CS)=40нс;   Рисунок 5.3. Цоколевка микросхемы ПЗУ КР556РТ13 Таблица 4. Таблица истинности м/с КР556РТ13

5.3 Разработка карты памяти 5.3 Разработка карты памяти

Рисунок 5.4. Карта памяти ОЗУ 0000h

Рисунок 5.5. Карта памяти ПЗУ  Таблица 5. Распределение адресов карты памяти Таблица 5. Распределение адресов карты памяти

5.4 Разработка дешифратора для модуля памяти 5.4 Разработка дешифратора для модуля памятиДля дешифрации адресного пространства используем микросхемы мелкой логики: К564ЛЕ10 (3ИЛИ-НЕ) – DD6; КР1564ЛИ1 (4 эл. 2И) – DD7 К155ЛН6 (6 эл. НЕ) – DD2, DD8;  Рисунок 5.6. Схема дешифрации С помощью микросхемы DD6 (К564ЛЕ10) выделяем диапазон 0000h-07FFh адресного пространства для ОЗУ и ПЗУ. Затем сигналом PSEN мы выбираем микросхему ПЗУ, а сигналом с порта P3.7 MCS-51 мы выбираем микросхему ОЗУ. Из-за внутренней организации микросхемы ПЗУ КР556РТ13 (1Кх4) диапазон адресов 0000h-07FFh разбиваем на два поддиапазона (0000h-03FFh и 0400h-07FFh) с помощью микросхем DD7 (КР1564ЛИ1) и DD2 (К155ЛН6).  5.5 Проверка согласования микросхем МПС по току. 5.5 Проверка согласования микросхем МПС по току.Исходные данные: а) б) в)    Рисунок 5.7. Цоколевка микросхем: а) К564ЛЕ10 б) К155ЛН6 в) КР1564ЛИ1  а  ) б) ) б) |