|

|

Исследование основных логических элементов (1). Отчет по лабораторной работе Исследование основных логических элементов и простейших комбинационных устройств

Саратовский государственный технический университет Балаковский институт техники, технологии и управления

Отчет по лабораторной работе

«Исследование основных логических элементов и простейших комбинационных устройств»

Выполнили:

Студенты группы УИТ-2з

Проверил:

БАЛАКОВО 2008

Цель работы: исследование базовой логики. Определение реализуемых функций схемных решений построенных на основе базовой логики

Описание установки

Назначение

Стенд предназначен для проведения лабораторных занятий по курсам "Основы автоматики и вычислительной техники", "Основы промышленной электроники", "Основы информатики и ЭВТ" в высших учебных заведениях и техникумах, в которых данные дисциплины не являются профилирующими предметами.

Стенд (рис.1) позволяет проводить лабораторные работы по изучению и исследованию следующих элементов, узлов И устройств цифровой вычислительной техники:

1. Логических элементов НЕ, ИЛИ, ИЛИ-НЕ,И, И-НЕ. ИСКЛЭЧАЮЩЕЕ ИЛИ, НЕРАВНОЗНАЧНОСТЬ;

2. Комбинационных узлов, собранных на базовых логических элементах -трехзарядного устройства проверки на четность, устройства сравнения двух двухразрядных чисел, двоичного одноразрядного сумматора (два варианта);

3. Комбинационных узлов, выполненных в виде самостоятельных ИМС-дешифратора, демультиплексора, мультиплексора, преобразователя двоичного кода в код семисегментного индикатора, четырехразрядного двоичного сумматора, четырехразрядного арифметическо-логического устройств»;

4. Последовательностных элементов, собранных на базовых логических элементах -RЗ -триггере на элементах И-НЕ, R3 -триггера на элементах ИЛИ-НЕ;

5. Последовательностных элементов и узлов, выполненных в виде самостоятельных ИМС:

R3 - триггера, D - триггера, Т - триггера, двухразрядного параллельного регистра, двухразрядного последовательного регистра, четырехразрядного универсального регистра, кольцевого счетчика, суммирующего и вычитающего двоичных счетчиков, счетчика с коэффициентом счета некратным степени 2, реверсивного счетчика с пред установкой, оперативного запоминающего устройства с организацией 16х4 бит.

6. Модели микроЭВМ в составе: АЛУ, ОЗУ, регистров операндов, команды и адреса, регистра-аккумулятора, мультиплексора общей шины, дешифратора сигналов управления, устройств ввода и вывода информации.

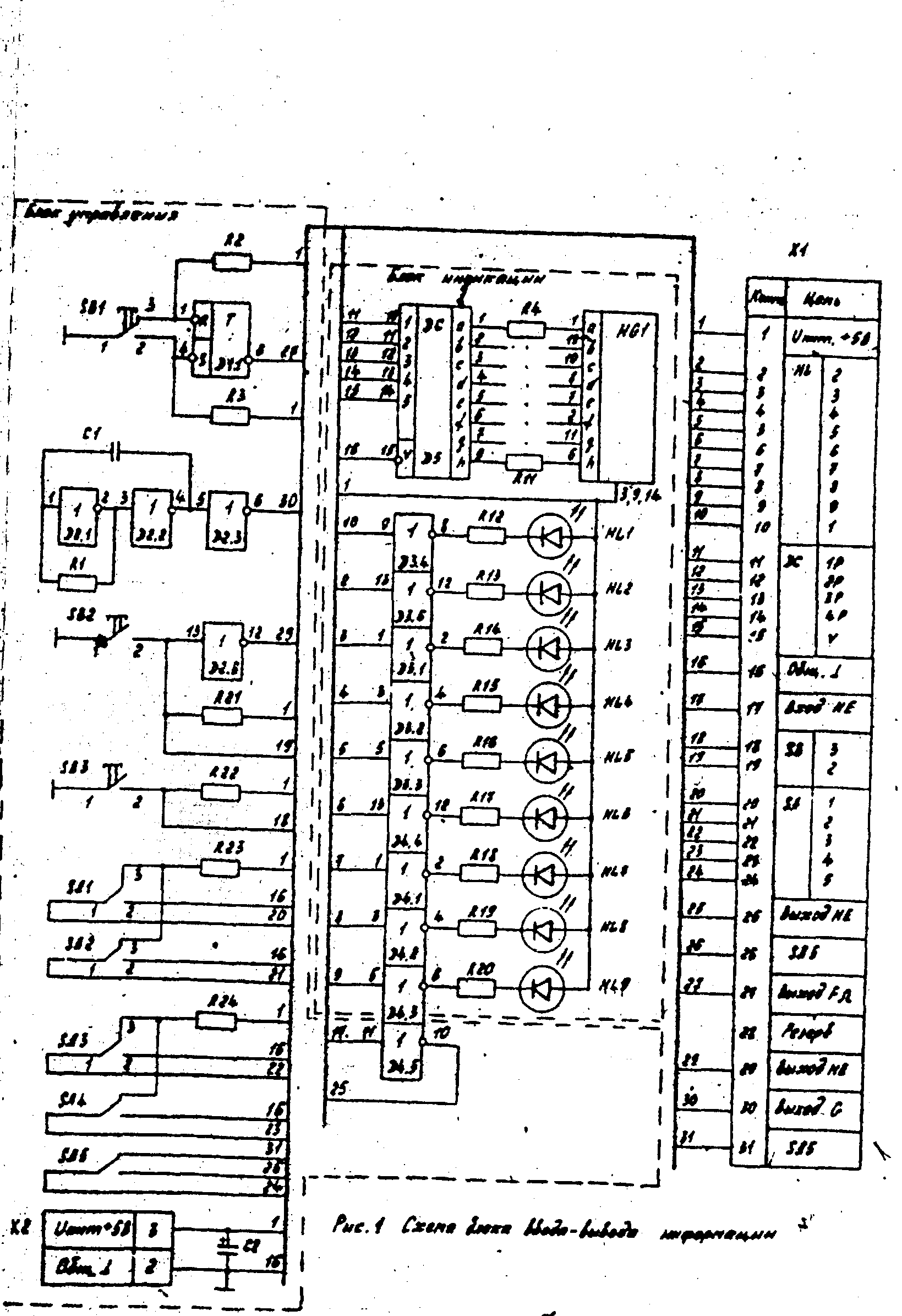

Стенд состоит из общего блока ввода-вывода информации и шести сменных плат, на которых установлены все исследуемые элементы, узлы и устройства. Стенд комплектуется набором сменных технологических карт (28 штук) с функциональными схемами исследуемых устройств .

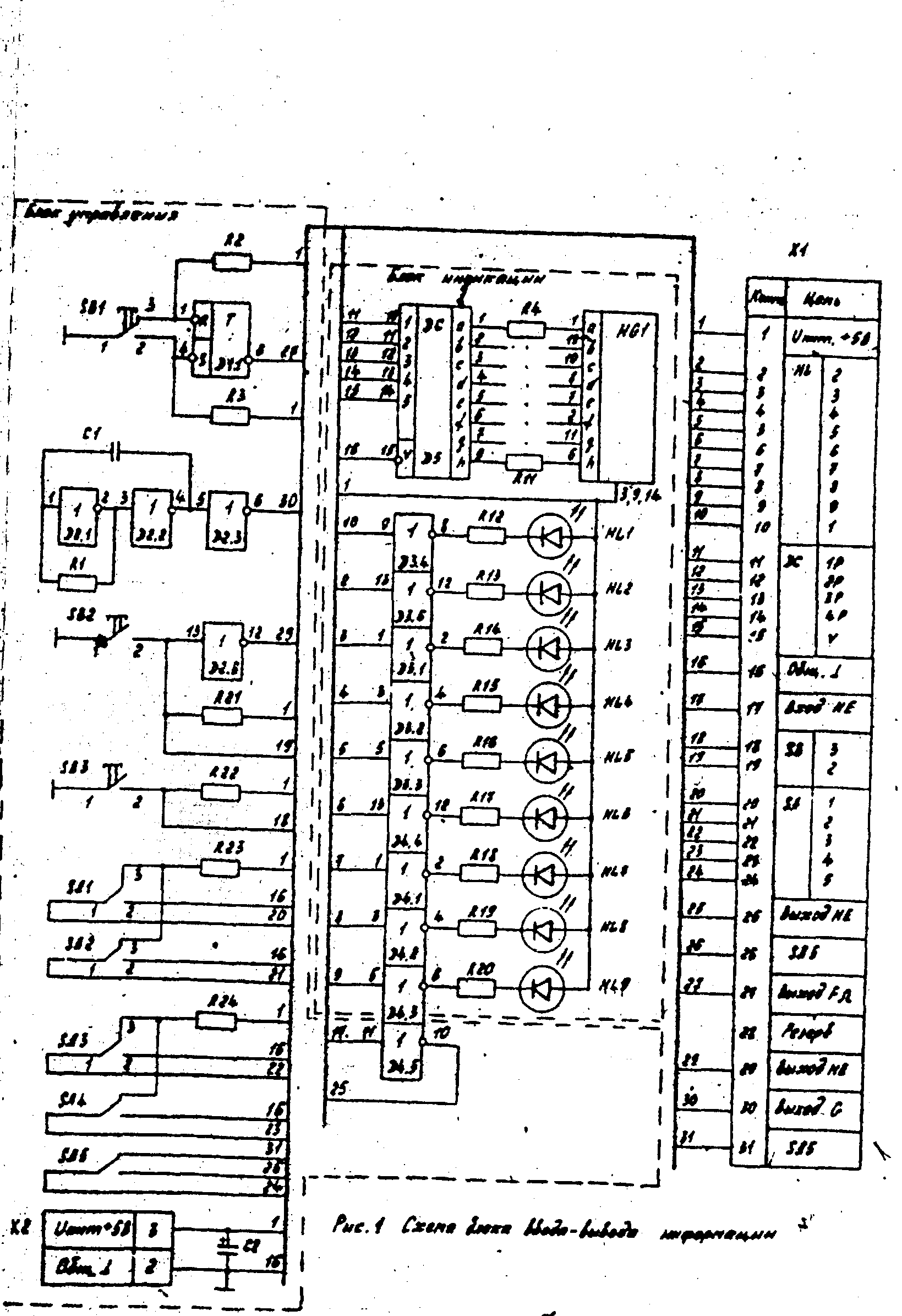

Рис.1

Техническое описание установки

Блок ввода-вывода информации

Принципиальная схема блока приведена на рис. I. Разъём Х2 предназначен для подключения внешнего стабилизированного источника постоянного тока с напряжением 5 ± 0,25 В и максимальным по требляемым током до 0,8 А (вариант 2 поставки). Разъём XI предназначен для подключения сменных плат с исследуемыми устройствами. В варианте 2 поставки разъём Х2 отсутствует, выходы "+5В" и "общий" блока питания подключаются к соответствующим контактам I и 16 разъёма XI.

На передней (наклонной) панели блока установлены тумблеры (SА1 -SА5) и кнопки (SВ1-SВЗ) ввода информации и задания режимов работы исследуемых устройств. Выводы всех тумблеров и кнопок, кроме SВ1, подключены непосредственно к контактам разъёма XI. Переключатели SА1- SА4, SВ2 и SВЗ предназначены для подачи логических сигналов с уровнями "0"(соответствующий вывод замкнут на общий провод) или "I" (вывод - на +5В). Тумблер SА5 подключается всеми своими выводами к разъёму и поэтому может использоваться в качестве переключателя "двух сигналов в одну линию" или, наоборот, "одного сигнала на два направления". Кнопка SВ1 подключена к схеме защиты от "дребезга" на триггере (микросхема D 1.1). С помощью этой кнопки на выходе триггера (27 контакт.разъёма XI). ;

формируется одиночный импульс с крутыми фронтами необходимый для нормальной работы исследуемых триггеров, регистров и счетчиков. При нажатии SВ1 на 27 контакте появляется логический 0, а при отпускании - логическая 1. Этот блок в дальнейшем на схемах обозначается как формирователь одиночного импульса .

1.1

X1 X1

& Y1

X2

Экспериментальная таблица

-

Х1

|

Х2

|

Y1

|

0

|

0

|

1

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

0

|

Реализуемая функция: 2 И-НЕ

1.2

X1 X1

& & Y1

X2

Экспериментальная таблица

-

Х1

|

Х2

|

Y1

|

0

|

0

|

0

|

0

|

1

|

0

|

1

|

0

|

0

|

1

|

1

|

1

|

Реализуемая функция: 2И. Коньюнкция, Y1=X1*X2

1.3

X1 X1

1 Y1 1 Y1

X2

Экспериментальная таблица

-

Х1

|

Х2

|

Y1

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

0

|

1

|

1

|

0

|

Реализуемая функция: 2ИЛИ-НЕ. Стрелка Пирса, Y1=X1↓X2=

1.4

X1 X1

1 1 Y1

X2

Экспериментальная таблица

-

Х1

|

Х2

|

Y1

|

0

|

0

|

0

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

Реализуемая функция: ИЛИ. Дизьюнкция, Y1=X1+X2

1.5

X1 X1

=1 Y1

X2

Экспериментальная таблица

-

Х1

|

Х2

|

Y1

|

0

|

0

|

0

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

0

|

Реализуемая функция: исключительное ИЛИ

1.6

X1 X1

=1 1 Y1 =1 1 Y1

X2

Экспериментальная таблица

-

Х1

|

Х2

|

Y1

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

0

|

1

|

1

|

1

|

Реализуемая функция: равнозначность (эквиввалентность), Y1=X1X2=X1*X2+⌐X1*⌐X2

1.7

X1 X1

=1 =1 Y1 =1 =1 Y1

X2 X2

Х3 Х3

Экспериментальная таблица

-

№ п.п

|

Х1

|

Х2

|

Х3

|

Y1

|

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

1

|

|

0

|

1

|

0

|

1

|

|

0

|

1

|

1

|

0

|

|

1

|

0

|

0

|

1

|

|

1

|

0

|

1

|

0

|

|

1

|

1

|

0

|

0

|

|

1

|

1

|

1

|

1

|

Реализуемая функция: Проверка на чётность (если число 1 на входе четно, то выход 0, если число 1 не чётно, то выход 1)

1.8

X1 X1

=1 =1

X2 X2

1 Y1 1 Y1

Х3 Х3

=1

Х4

Экспериментальная таблица

-

№ п.п

|

Х1

|

Х2

|

Х3

|

Х4

|

Y1

|

1

|

0

|

0

|

0

|

0

|

1

|

2

|

0

|

0

|

0

|

1

|

0

|

3

|

0

|

0

|

1

|

0

|

0

|

4

|

0

|

0

|

1

|

1

|

1

|

5

|

0

|

1

|

0

|

0

|

0

|

6

|

0

|

1

|

0

|

1

|

0

|

7

|

0

|

1

|

1

|

0

|

0

|

8

|

0

|

1

|

1

|

1

|

0

|

9

|

1

|

0

|

0

|

0

|

0

|

10

|

1

|

0

|

0

|

1

|

0

|

11

|

1

|

0

|

1

|

0

|

0

|

12

|

1

|

0

|

1

|

1

|

0

|

13

|

1

|

1

|

0

|

0

|

1

|

14

|

1

|

1

|

0

|

1

|

0

|

15

|

1

|

1

|

1

|

0

|

0

|

16

|

1

|

1

|

1

|

1

|

1

|

Реализуемая функция: Сравнение двух двухразрядных чисел

1.9

X1 Y2 Y1 X1 Y2 Y1

X2

=1 =1

& 1

Экспериментальная таблица

-

Х1

|

Х2

|

Y2

|

Y1

|

0

|

0

|

0

|

0

|

0

|

1

|

0

|

1

|

1

|

0

|

0

|

1

|

1

|

1

|

1

|

0

|

Реализуемая функция: двоичный одноразрядный сумматор (Y1 и Y2, представляют число в двоичной системе счисления)

Вывод: В данной лабораторной работе исследовали базовую логику и определили реализуемые функции схемных решений. Также познакомились с принципом работы испытательного стенда для изучения устройств цифровой вычислительной техники. |

|

|

Скачать 170 Kb.

Скачать 170 Kb.

X1

X1 =1 =1 Y1

=1 =1 Y1

X2

X2 Х3

Х3 X1

X1 =1

=1  X2

X2 1 Y1

1 Y1

Х3

Х3 X1 Y2 Y1

X1 Y2 Y1

X1

X1