Отчет по лабораторной работе Построение многоразрядных комбинационных сумматоров

Скачать 193.5 Kb. Скачать 193.5 Kb.

|

государственное автономное профессиональное образовательное учреждение Чувашской Республики «Межрегиональный центр компетенций – Чебоксарский электромеханический колледж» Министерства образования и молодежной политики Чувашской Республики Дисциплина МДК 01.01 Цифровая схемотехника ОТЧЕТ

ЛР.Кс1-16.26.МДК01.01.ОТ

2018 Цель работы: Изучение принципа работы многоразрядных комбинационных сумматоров. Выполнение работы:

Сформированная сумма накапливается в сдвигающем регистре суммы. Возникающий перенос с задержкой на элементе задержки на один такт поступает на вход сумматора только в следующем такте, когда на входы а и в будут поданы следующие разряды чисел А и В.

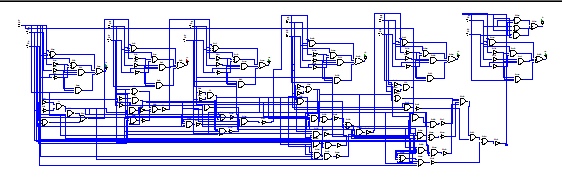

Рисунок 1 – Комбинационная схема четырехразрядного двоичного сумматора с последовательным переносом

с    0=a0*b0*Свх*h0 0=a0*b0*Свх*h0c     1=a1*b1* a0*b0*h1* Свх*h1*h0 1=a1*b1* a0*b0*h1* Свх*h1*h0c      2=a2*b2*a1*b1*h2*a0*b0*h1*h2* Свх*h2*h1*h0 2=a2*b2*a1*b1*h2*a0*b0*h1*h2* Свх*h2*h1*h0с         3=a3*b3*a2*b2*h3*a1*b1*h2*h3*a0*b0*h1*h2*h3* Свх*h3*h2*h1*h0 3=a3*b3*a2*b2*h3*a1*b1*h2*h3*a0*b0*h1*h2*h3* Свх*h3*h2*h1*h0c        4=a4*b4*a3*b3*h4*a2*b2*h3*h4*a1*b1*h2*h3*h4*a0*b0*h1*h2*h3*h4* Свх*h4*h3*h2*h1*h0 4=a4*b4*a3*b3*h4*a2*b2*h3*h4*a1*b1*h2*h3*h4*a0*b0*h1*h2*h3*h4* Свх*h4*h3*h2*h1*h0c         5=a5*b5*a4*b4*h5*a3*b3*h4*h5*a2*b2*h3*h4*h5*a1*b1*h2*h3*h4*h5* a0*b0*h1*h2*h3*h4*h5*Свх*h5*h4*h3*h2*h1*h0 5=a5*b5*a4*b4*h5*a3*b3*h4*h5*a2*b2*h3*h4*h5*a1*b1*h2*h3*h4*h5* a0*b0*h1*h2*h3*h4*h5*Свх*h5*h4*h3*h2*h1*h0c             6=a6*b6*a5*b5*h6*a4*b4*h5*h6*a3*b3*h4*h5*h6*a2*b2*h3*h4*h5*h6*a1*b1*h2*h3*h4*h5*h6*a0*b0*h1*h2*h3*h4*h5*h6*Свх*h6*h5*h4*h3*h2*h1*h0 6=a6*b6*a5*b5*h6*a4*b4*h5*h6*a3*b3*h4*h5*h6*a2*b2*h3*h4*h5*h6*a1*b1*h2*h3*h4*h5*h6*a0*b0*h1*h2*h3*h4*h5*h6*Свх*h6*h5*h4*h3*h2*h1*h0

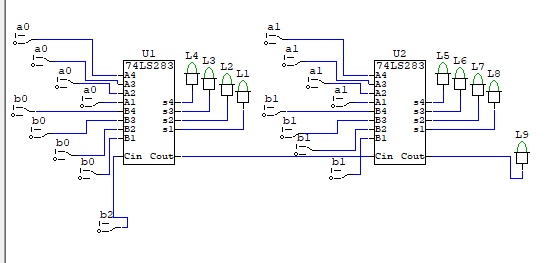

Рисунок 2 – Схема шестиразрядного двоичного сумматора с параллельным переносом

Рисунок 3 – Схема восьмиразрядного комбинационного двоичного сумматора с последовательным переносом на интегральных микросхемах Вывод Разобрали принципы работы многоразрядных комбинационных сумматоров. С помощью схемы рассмотрели работу четырехразрядного двоичного сумматора с последовательным переносом, шестиразрядного двоичного сумматора с параллельным переносом и восьмиразрядного комбинационного двоичного сумматора с последовательным переносом на интегральных микросхемах. Закрепили знания о сумматорах. | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

равнения функций формирования признака переноса:

равнения функций формирования признака переноса: